تراشهها یک قسمت از طراحی را ساده کردهاند اما جعبه پاندورا را در جلوی دیگر باز کردهاند. پیچیدگی شبیه سازی هر کدام تراشه پایین تر است اما اکنون اتصال تراشه به تراشه پیچیده شده است. مردم در حال آزمایش با پروتکل های مختلف اتصال، تغییرات UCIe، تغییر تنظیمات UCIe، سرعت رابط، تعداد لایه های فیزیکی و غیره هستند. اکنون استانداردهای قدیمی مانند AXI، پروتکل های جدید مانند PICE6.0 و انسجام کش را به ترکیب اضافه کنید.

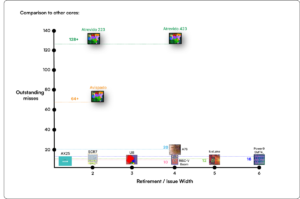

در کل، این یک مجموعه کاملاً جدید از آزمایشات را ایجاد می کند. یکی که شبیه سازی سنتی و مدل سازی RTL برای آن کار نخواهد کرد. شما باید ابتدا تلاش خود را صرف معاوضه معماری کنید، نه فقط در انتخاب اجزا. این بدان معنی است که شما باید تجزیه و تحلیل ترافیک، پارتیشن بندی برنامه، اندازه سیستم و تاثیر انواع مختلف لایه فیزیکی را انجام دهید. همچنین، بسته به برنامه، معیار بسیار متفاوت خواهد بود.

مشخصات UCIe جدید است و هیچ معیار مشخصی وجود ندارد. همچنین، مشخصات UCIe فقط راهنمایی در مورد تأخیر و قدرت ارائه می دهد. هر دو الزامات سختگیرانه هستند. این به این معنی است که یک مطالعه قدرت-عملکرد-منطقه اجتناب ناپذیر است. از آنجایی که شما تبدیل پروتکل-پروتکل-پروتکل مانند PCIe 6.0 به UCIe به AXI دارید، تنظیم مدل سازی پیچیده است.

یک راه حل این است که با استفاده از مدل سازی سیستم نگاه کنید VisualSim از جانب میرابیلیس طرح. آنها اخیراً یک مدل IP در سطح سیستم UCIe را راهاندازی کردهاند و تعدادی از موارد استفاده از اتصال متقابل را به نمایش خواهند گذاشت. اجلاس چیپلت. برای راهنمایی طراحان، آنها یک راهنمای با موارد استفاده زیاد، نتایج مورد انتظار قدرت عملکرد و گزینه هایی برای بهینه سازی منتشر کرده اند. آنها هم یک ارائه مقاله و هم یک غرفه در اجلاس سران دارند. امیدوارم آنجا ببینمت!

همچنین، در اینجا پیوند مقاله ای است که مردم می توانند دریافت کنند: مدل سازی عملکرد یک سیستم محاسباتی ناهمگن بر اساس معماری UCIe Interconnect

چکیده:

طرحهای تراشههای پیچیده امروزی در گرههای پیشرو عموماً از چندین قالب (یا تراشهها) تشکیل شدهاند. این رویکرد امکان استفاده از قالب های تولید کنندگان یا فرآیندهای مختلف و همچنین IP قابل استفاده مجدد را فراهم می کند. طراحان برای ارزیابی پیاده سازی های مختلف چنین موقعیت های پیچیده ای به یک مدل سطح سیستم نیاز دارند.

یک سیستم نمونه شامل یک چیپلت ورودی/خروجی، چیپلت هسته کم توان، چیپلت هسته با کارایی بالا، چیپلت صوتی-تصویری و چیپلت آنالوگ است که با استفاده از استاندارد جهانی تراشه های اتصال سریع (UCIe) به هم متصل شده اند.

تیم ما چندین سناریو و پیکربندی از جمله بستههای پیشرفته و استاندارد، پروفایلها و منابع ترافیک متنوع، و یک زمانسنج را برای افزایش دسترسی و ارزیابی رویدادها در زمان وقفه در نظر گرفت. شناسایی نقاط قوت و ضعف اتصال UCIe برای برنامههای ماموریتی به ما کمک کرد تا پیکربندی بهینه برای هر زیرسیستم را برای برآوردن نیازهای عملکرد، قدرت و عملکرد به دست آوریم.

درباره Mirabilis Design Inc.

Mirabilis Design یک شرکت نرمافزاری دره سیلیکون است که نرمافزار و راهحلهای آموزشی برای شناسایی و حذف ریسک در مشخصات محصول، پیشبینی دقیق منابع انسانی و زمانی مورد نیاز برای توسعه محصول و بهبود ارتباطات بین مهندسی متنوع ارائه میدهد.

تیم.

VisualSim Architect مالکیت معنوی، مدلسازی در سطح سیستم، شبیهسازی، تجزیه و تحلیل محیط و قالبهای کاربردی را برای بهبود قابل توجه ساخت مدل، شبیهسازی، تجزیه و تحلیل و تأیید RTL ترکیب میکند. محیط طراحان را قادر می سازد تا به سرعت به طرحی همگرا شوند که مجموعه متنوعی از نیازهای زمان و توان وابسته به یکدیگر را برآورده می کند. در مراحل اولیه طراحی به موازات (و به عنوان کمکی برای) مشخصات نوشته شده و قبل از پیاده سازی (به عنوان مثال، RTL، کد نرم افزار، یا شماتیک) محصول استفاده می شود.

همچنین خواندن:

وبینار: چگونه در حین کاوش در معماری به بیش از 95% اندازه گیری قدرت دقیق دست یابیم

نگاشت SysML به معماری سخت افزار

دوره های طراحی مدل محور برای دانشجویان

اشتراک گذاری این پست از طریق:

- محتوای مبتنی بر SEO و توزیع روابط عمومی. امروز تقویت شوید.

- PlatoData.Network Vertical Generative Ai. به خودت قدرت بده دسترسی به اینجا.

- PlatoAiStream. هوش وب 3 دانش تقویت شده دسترسی به اینجا.

- PlatoESG. کربن ، CleanTech، انرژی، محیط، خورشیدی، مدیریت پسماند دسترسی به اینجا.

- PlatoHealth. هوش بیوتکنولوژی و آزمایشات بالینی. دسترسی به اینجا.

- منبع: https://semiwiki.com/ip/mirabilis-design-ip/341339-chiplets-open-pandoras-box/

- : دارد

- :است

- :نه

- a

- دقیق

- به درستی

- رسیدن

- اضافه کردن

- پیشرفته

- کمک

- اجازه می دهد تا

- در امتداد

- همچنین

- an

- تحلیل

- و

- دیگر

- کاربرد

- برنامه های کاربردی

- روش

- معماری

- هستند

- محدوده

- AS

- At

- مستقر

- BE

- شدن

- قبل از

- محک

- معیار

- میان

- هر دو

- جعبه

- اما

- نهانگاه

- CAN

- می توانید دریافت کنید

- موارد

- تراشه

- واضح

- رمز

- ترکیب

- ارتباط

- شرکت

- به طور کامل

- پیچیده

- پیچیدگی

- اجزاء

- محاسبه

- رفتار

- پیکر بندی

- در نظر گرفته

- تشکیل شده است

- ساخت و ساز

- همگرا

- تبدیل

- هسته

- دوره

- ایجاد

- نشان دادن

- بستگی دارد

- طرح

- روند طراحی

- طراحان

- طرح

- توسعه

- مختلف

- مختلف

- در طی

- هر

- در اوایل

- تلاش

- از بین بردن

- شبیه سازی

- را قادر می سازد

- محیط

- ارزیابی

- حوادث

- مثال

- انتظار می رود

- تجربه

- آزمایش

- صریح

- گسترش

- نام خانوادگی

- برای

- از جانب

- جلو

- تابعی

- عموما

- دریافت کنید

- گوگل

- راهنمایی

- راهنمایی

- سخت افزار

- آیا

- کمک کرد

- اینجا کلیک نمایید

- عملکرد بالا

- امید

- چگونه

- چگونه

- HTTPS

- انسان

- i

- شناسایی

- شناسایی

- تأثیر

- پیاده سازی

- پیاده سازی ها

- بهبود

- in

- از جمله

- فکری

- مالکیت معنوی

- به هم پیوسته

- رابط

- IP

- IT

- JPG

- تنها

- تاخیر

- راه اندازی

- لایه

- لایه

- میراث

- سطح

- پسندیدن

- ارتباط دادن

- نگاه کنيد

- مقدار زیادی

- کم

- کاهش

- تولید کنندگان

- حداکثر عرض

- متوسط

- به معنی

- اندازه گیری

- دیدار

- ملاقات

- ماموریت

- مخلوط

- مدل

- مدل سازی

- مدل سازی

- چندگانه

- نیاز

- جدید

- نه

- گره

- اکنون

- عدد

- گرفتن

- of

- on

- ONE

- فقط

- باز کن

- باز

- بهینه

- بهینه سازی

- گزینه

- or

- بسته

- مقاله

- موازی

- کارایی

- فیزیکی

- افلاطون

- هوش داده افلاطون

- PlatoData

- پست

- قدرت

- پیش بینی

- ارائه

- روند

- فرآیندهای

- محصول

- پروفایل

- ویژگی

- پروتکل

- فراهم می کند

- ارائه

- منتشر شده

- سریعا

- رسیدن به

- خواندن

- تازه

- ضروری

- مورد نیاز

- منابع

- نتایج

- قابل استفاده مجدد

- خطر

- سناریوها

- دیدن

- انتخاب

- تنظیم

- تنظیمات

- برپایی

- چند

- به طور قابل توجهی

- سیلیکون

- سیلیکون ولی (Silicon Valley)

- ساده شده

- شبیه سازی

- شرایط

- So

- نرم افزار

- راه حل

- مزایا

- مشخصات

- سرعت

- خرج کردن

- استاندارد

- استانداردهای

- نقاط قوت

- دقیق

- مهاجرت تحصیلی

- چنین

- قله

- سیستم

- تیم

- قالب

- که

- La

- آنجا.

- آنها

- این

- زمان

- به

- سنتی

- ترافیک

- آموزش

- انواع

- جهانی

- us

- استفاده کنید

- استفاده

- با استفاده از

- دره

- تغییرات

- تایید

- بسیار

- از طريق

- نقاط ضعف

- خوب

- که

- اراده

- با

- مهاجرت کاری

- کتبی

- شما

- زفیرنت