See on huvitav idee, mis kasutab simulatsiooni kiirendamiseks riistvaratoega spekulatiivset paralleelsust, kusjuures keerd nõuab kohandatud riistvara. Paul Cunningham (vanem VP/GM, Cadence'i kontrollimine), Raúl Camposano (Silicon Catalyst, ettevõtja, endine Synopsysi tehnoloogiadirektor ja nüüd Silvaco tehnikadirektor) ja mina jätkame oma uurimisideede sarja. Nagu alati, on tagasiside teretulnud.

Innovatsioon

Selle kuu valik on Chronos: tõhus spekulatiivne paralleelsus kiirendite jaoks. Autorid esitlesid artiklit 2020. aasta programmeerimiskeelte ja operatsioonisüsteemide arhitektuurilise toe konverentsil ning on pärit MIT-st.

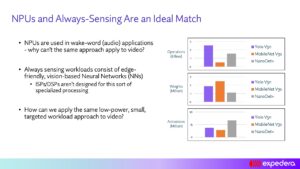

Paralleelsuse ärakasutamine mitmetuumaliste protsessorite abil on üks võimalus rakendustes, kus paralleelsus on iseenesestmõistetav. Teisi algoritme ei pruugi olla nii lihtne osadeks jagada, kuid need võivad kasu saada spekulatiivsest täitmisest, mis kasutab sisemist paralleelsust. Tavaliselt sõltub spekulatiivne täitmine vahemälu sidususest, mis on eriti simulatsiooni jaoks suur üldkulu. See meetod väldib sidususe vajadusi, lokaliseerib ülesande täitmise füüsiliselt, et arvutada paanid sihtmärgi lugemis-kirjutamisobjekti järgi, tagades, et konfliktide tuvastamist saab tuvastada lokaalselt, ilma et oleks vaja globaalset sidususe haldust. Ülesandeid saab täita spekulatiivselt paralleelselt; mis tahes tuvastatud konflikti saab ülesandest selle alamülesannete kaudu lahti rullida ja seejärel uuesti käivitada, ilma et oleks vaja teisi lõime peatada.

Siin on veel üks märkus. See meetod toetab erinevalt enamikust riistvarakiirenduse tehnikatest viivituspõhist simulatsiooni.

Pauli nägemus

Vau, milline imeline kõrge oktaanarvuga paber MIT-ilt! Kui küsitakse paralleelarvutuse kohta, mõtlen kohe lõimedele, mutexidele ja mälu sidususele. Loomulikult on kaasaegsed mitmetuumalised protsessorid kujundatud nii. Kuid see pole ainus viis riistvara paralleelsuse toetamiseks.

Selles artiklis pakutakse paralleelseks alternatiivset arhitektuuri nimega Chronos, mis põhineb järjestatud ülesannete järjekorral. Käitusajal täidetakse ülesanded ajatempli järjekorras ja iga ülesanne saab luua uusi alamülesandeid, mis lisatakse dünaamiliselt järjekorda. Täitmine algab mõne algülesande järjekorda panemisega ja lõpeb siis, kui järjekorras enam ülesandeid pole.

Järjekorras olevad ülesanded jaotatakse paralleelselt mitmele töötlemiselemendile (PE) – see tähendab, et Chronos täidab spekulatiivselt tulevasi ülesandeid enne, kui praegune ülesanne on lõpetatud. Kui praegune ülesanne tühistab kõik spekulatiivselt täidetud tulevased ülesanded, siis nende tulevaste ülesannete toimingud tühistatakse ja need pannakse uuesti järjekorda. Selle kontseptsiooni õige rakendamine riistvaras pole lihtne, kuid väliskasutaja jaoks on see ilus: lihtsalt kodeerite oma algoritmi nii, nagu käivitataks tegumijärjekorda ühel PE-l. Pole vaja kodeerida ühtegi mutexet ega muretseda ummikseisu pärast.

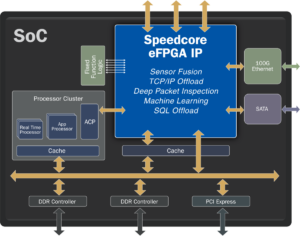

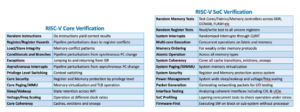

Autorid rakendavad Chronose SystemVerilogis ja kompileerivad selle FPGA-ks. Suur osa paberist on pühendatud selgitamisele, kuidas nad on rakendanud ülesannete järjekorda ja mis tahes vajalikku riistvara lahtirullimist, et tagada maksimaalne tõhusus. Chronose võrdlusuuringu aluseks on neli algoritmi, mis sobivad hästi tegumijärjekorrapõhise arhitektuuriga. Iga algoritmi rakendatakse kahel viisil: esiteks kasutatakse spetsiaalset algoritmispetsiifilist PE-d ja teiseks kasutatakse PE-na avatud lähtekoodiga 32-bitist manustatud RISC-V protsessorit. Seejärel võrreldakse Chronose jõudlust Intel Xeoni serveris töötavate algoritmide mitme lõimega tarkvararakendustega, millel on Chronose jaoks kasutatava FPGA-ga sarnane hinnasilt. Tulemused on muljetavaldavad – Chronos on 3x kuni 15x parem kui Xeoni serveri kasutamine. Kuid tabeli 3 võrdlemine joonisega 14 paneb mind natuke muretsema, et suurem osa neist kasudest tuli pigem algoritmispetsiifilistelt PE-delt kui Chronose arhitektuurilt endalt.

Arvestades, et see on kinnitusblogi, suumisin loomulikult sisse väravataseme simulatsiooni etaloni. EDA tööstus on teinud suuri investeeringuid, et proovida ja paralleelselt loogilise simulatsiooniga simuleerida, ning on osutunud raskeks näha suurt kasu peale mõne konkreetse kasutusjuhtumi. See on peamiselt tingitud enamiku reaalmaailma simulatsioonide toimivusest, kus domineerivad laadimis-/salvestamisjuhised, mis puuduvad L3-vahemälus ja lähevad DRAM-ile. Selles dokumendis on ainult üks testjuhtumi võrdlusanalüüs ja see on väike 32-bitine kandesalvestuse lisaja. Kui loete seda ajaveebi ja oleksite huvitatud põhjalikumast võrdlusuuringust, siis andke mulle teada – kui Chronos suudab pärismaailma simulatsioonidel tõeliselt hästi skaleerida, oleks sellel tohutu kaubanduslik väärtus!

Raúli nägemus

Selle artikli peamine panus on Ruumiliselt paiknevate järjestatud ülesannete (SLOT) täitmise mudel mis on tõhus riistvarakiirendite jaoks, mis kasutavad ära paralleelsust ja spekulatsioone, ning rakenduste jaoks, mis genereerivad käitusajal dünaamiliselt ülesandeid. Dünaamilise paralleelsuse tugi on simulatsiooni jaoks vältimatu ja spekulatiivne sünkroonimine on ahvatlev valik, kuid sidususe üldkulud on liiga suured.

SLOT väldib vajadust sidususe järele, piirates iga ülesande töötamist (kirjutamist) ühel objektil ja toetab järjestatud ülesandeid, et võimaldada mitme objekti atomaalsust. SLOT-rakendused on järjestatud, dünaamiliselt loodud ülesanded, mida iseloomustavad ajatempel ja objekti ID. Ajatemplid määravad tellimuse piirangud; objekti ID-d määravad andmete sõltuvused, st ülesanded on andmetest sõltuvad siis ja ainult siis, kui neil on sama objekti ID. (kui on lugemissõltuvus, saab ülesande täita spekulatiivselt). Konfliktide tuvastamine muutub lokaalseks (ilma keerukate jälgimisstruktuurideta), vastendades objekti ID-d tuumadele või plaatidele ja saates iga ülesande kohta, kus selle objekti ID on kaardistatud.

. Chronos süsteem rakendati AWS FPGA raamistikus 16 plaadiga süsteemina, millest igaühel on 4 rakendusspetsiifiline töötlemiselement (PE), mis töötab sagedusel 125 MHz. Seda süsteemi võrreldakse baastasemega, mis koosneb 20-tuumalisest/40-lõimelisest 2.4 GHz Intel Xeon E5-2676v3-st, mis on valitud spetsiaalselt seetõttu, et selle hind on võrreldav FPGA-ga (umbes 2 dollarit tunnis). Ühe ülesande täitmisel ühel PE-l on Chronos 2.45 korda kiirem kui algtasemel. Samaaegsete ülesannete arvu suurenedes suureneb Chronose juurutamine 44.9 plaadil enesesuhtelise kiiruseni 8-kordselt, mis vastab 15.3-kordsele kiirusele võrreldes protsessori juurutusega. Nad võrdlesid ka rakendust, mis põhineb üldotstarbelisel RISC-V-l, mitte rakendusespetsiifilistel PE-del; PE-d olid 5 korda kiiremad kui RISC-V.

Minu arvates oli see paber muljetavaldav, kuna see hõlmab kõike alates kontseptsioonist kuni SLOT-i täitmismudeli määratlemiseni kuni riistvara rakendamiseni ja üksikasjaliku võrdluseni traditsioonilise Xeoni protsessoriga nelja rakenduse jaoks. Pingutused on märkimisväärsed, Chronos on üle 4 20,000 SystemVerilogi rea. Tulemuseks on 5.4-kordne keskmine (neljast rakendusest) kiirem võrreldes tarkvaraga paralleelsete versioonidega, mis on tingitud suuremast paralleelsusest ja spekulatiivse täitmise suuremast kasutamisest. Paberit tasub lugeda ka mittesimulatsiooniülesannete täitmiseks; paber sisaldab kolme näidet.

Jaga seda postitust:

- SEO-põhise sisu ja PR-levi. Võimenduge juba täna.

- Platoblockchain. Web3 metaversiooni intelligentsus. Täiustatud teadmised. Juurdepääs siia.

- Allikas: https://semiwiki.com/eda/326261-speculation-for-simulation-innovation-in-verification/

- :on

- 000

- 2020

- 8

- a

- MEIST

- kiirendama

- kiirendus

- kiirendid

- ACM

- meetmete

- lisatud

- algoritm

- algoritme

- alternatiiv

- alati

- ja

- ahvatlev

- taotlus

- rakendusespetsiifiline

- rakendused

- arhitektuuri-

- arhitektuur

- OLEME

- AS

- At

- autorid

- AWS

- põhineb

- Baseline

- BE

- ilus

- sest

- muutub

- enne

- on

- võrrelda

- võrdlusuuring

- kasu

- Parem

- Peale

- Suur

- Natuke

- Blogi

- by

- vahemälu

- Cadence

- kutsutud

- CAN

- viima

- juhtudel

- Katalüsaator

- iseloomustatud

- laps

- valitud

- kood

- kaubandus-

- võrreldav

- võrreldes

- võrrelda

- võrdlus

- Lõpetatud

- keeruline

- arvutamine

- Arvutama

- mõiste

- konkurent

- Konverents

- konflikt

- Koosneb

- piiranguid

- jätkama

- panus

- Vastav

- kursus

- kaaned

- Protsessor

- looma

- loodud

- CTO

- Praegune

- tava

- andmed

- pühendunud

- Sõltuvus

- sõltub

- kavandatud

- üksikasjalik

- tuvastatud

- Detection

- raske

- dünaamiline

- dünaamiliselt

- e

- iga

- kergesti

- efektiivsus

- tõhus

- jõupingutusi

- elemendid

- varjatud

- võimaldama

- lõppeb

- tagades

- Ettevõtja

- eriti

- kõik

- näited

- täitma

- hukkamine

- täitmine

- selgitades

- Ekspluateeri

- kiiremini

- tagasiside

- vähe

- Joonis

- esimene

- eest

- endine

- avastatud

- FPGA

- Raamistik

- Alates

- tulevik

- Kasum

- Üldine

- tekitama

- GHz Intel

- Globaalne

- läheb

- riistvara

- Olema

- tugevalt

- siin

- Suur

- Kuidas

- aga

- HTTPS

- tohutu

- i

- ID

- idee

- ideid

- kohe

- rakendada

- täitmine

- rakendatud

- rakendamisel

- muljetavaldav

- in

- hõlmab

- Tõstab

- tööstus

- vältimatu

- esialgne

- Innovatsioon

- juhised

- Intel

- huvitatud

- huvitav

- sisemine

- investeerinud

- IT

- ITS

- ise

- Teadma

- Keeled

- liinid

- kohalik

- kohapeal

- asub

- põhiline

- TEEB

- juhtimine

- kaardistus

- max laiuse

- maksimaalne

- vahendid

- Mälu

- meetod

- võib

- puuduvad

- MIT

- mudel

- Kaasaegne

- rohkem

- kõige

- mitmekordne

- vajalik

- Vajadus

- Uus

- number

- objekt

- of

- on

- ONE

- avatud

- avatud lähtekoodiga

- töötama

- tegutsevad

- operatsioonisüsteemid

- valik

- et

- Muu

- väljaspool

- P&E

- Paber

- Parallel

- Paul

- jõudlus

- Füüsiliselt

- valima

- Platon

- Platoni andmete intelligentsus

- PlatoData

- palun

- Punkt

- post

- esitatud

- hind

- töötlemine

- töötlejad

- Programming

- programmeerimiskeeled

- teeb ettepaneku

- tõestatud

- eesmärk

- Putting

- pigem

- Lugenud

- Lugemine

- reaalne

- päris maailm

- teadustöö

- piirav

- kaasa

- Tulemused

- jooksmine

- sama

- Säästa

- Skaala

- Kaalud

- Teine

- saatmine

- vanem

- Seeria

- riiul

- Räni

- sarnane

- simuleerimine

- ühekordne

- So

- tarkvara

- mõned

- allikas

- konkreetse

- eriti

- spekulatsioonid

- mahukas

- toetama

- Toetab

- Sünkroonimine

- süsteem

- süsteemid

- tabel

- TAG

- sihtmärk

- Ülesanne

- ülesanded

- tehnikat

- et

- .

- Need

- kolm

- Läbi

- ajatempel

- et

- liiga

- Jälgimine

- traditsiooniline

- vääne

- kasutama

- Kasutaja

- tavaliselt

- Kontrollimine

- kaudu

- Tee..

- kuidas

- teretulnud

- Hästi

- M

- mis

- koos

- ilma

- imeline

- maailm

- väärt

- oleks

- kirjutama

- Sinu

- sephyrnet