Alates 1980. aastate debüüdist 10 Mbps jagatud kohtvõrkudega koaksiaalkaablite kaudu on Ethernet näinud järjepidevaid edusamme, nüüd on võimalik toetada kiirust kuni 1.6 Tbps. See areng on võimaldanud Ethernetil teenindada laiemat valikut rakendusi, nagu otseülekanne, raadiojuurdepääsuvõrgud ja tööstuslik juhtimine, rõhutades usaldusväärse pakettide edastamise ja teenuse kvaliteedi tähtsust. Kuna praegune Interneti-ribalaius on ~500 Tbps, kasvab nõudlus täiustatud andmekeskusesisese andmekeskuse liikluse haldamise järele. Kuigi üksikud serverid ei tööta veel terabiti sekundis tasemel, on andmekeskuse üldine liiklus sellele ulatusele lähenemas, mis sunnib IEEE 802.3dj gruppi standardimistööd tegema ning laieneva andmevoo haldamiseks on vaja tugevaid Etherneti kontrollereid ja SerDesid. Suurenevate nõudmiste taustal on protsessoritevaheline suhtlus juba saavutamas seda kiirust.

Protsessoritevaheline side juhib vajadust 1.6 T kiiruse järele minimaalse latentsusega. Kuigi üksikuid seadmeid piirab nende loomulik töötlemisvõimsus ja kiibi suurus, võib kiipide kombineerimine neid võimsusi oluliselt suurendada. Esimese põlvkonna rakendustele järgneb eeldatavasti andmekeskusesisesed lüliti-lüliti ühendused, mis võimaldavad ühendada suure jõudlusega protsessoreid ja mälu, suurendades pilvandmetöötluse skaleeritavust ja tõhusust.

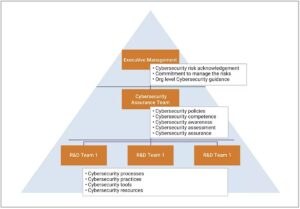

IEEE 802.3dj algatus: Etherneti standardite täiustamine 1.6 Tbps koostalitlusvõime jaoks

Järgimine arenevatele standardimispüüdlustele on ökosüsteemide sujuva koostalitlusvõime jaoks ülioluline. IEEE 802.3dj grupp on koostamas tulevast Etherneti standardit, mis hõlmab füüsilisi kihte ja haldusparameetreid kiirustele 200 G kuni 1.6 terabitti sekundis. Rühma eesmärk on 1.6 Tbps Etherneti MAC andmeedastuskiirus, mille eesmärk on MAC-kihi maksimaalne bitiveamäär mitte üle 10–13. Täiendavad sätted hõlmavad valikulisi 16 ja 8 rajaga kinnitusüksuste liideseid (AUI), mis sobivad erinevate kiibirakenduste jaoks, võimendades 112G ja 224G SerDes. Füüsiliselt hõlmab 1.6 Tbps spetsifikatsioon edastust 8 paari vasest twinax-kaablite kaudu kuni ühe meetri ulatuses ja 8 paari kiudusid vahemaadel, mis ulatuvad 500 meetri ja 2 km vahele. Kuigi standardi täielikku ratifitseerimist oodatakse 2026. aasta kevadeks, valmib põhifunktsioonide komplekt 2024. aastaks.

Ribalaiuse ülekoormus ja veaparandus 1.6T Etherneti alamsüsteemides

Joonis 1: 1.6T Etherneti alamsüsteemi komponentide skeem.

Varasemates Etherneti iteratsioonides keskendus PCS peamiselt andmete kodeerimisele usaldusväärseks pakettide tuvastamiseks. Ent 1.6T Etherneti kiiruse suurenemisega muutub ilmseks vajadus edasisuunatud veaparanduse (FEC) järele, eriti selleks, et vältida signaali halvenemist isegi lühikeste linkide korral. Sel eesmärgil kasutab 1.6T Ethernet jätkuvalt Reed-Solomon FEC-i. See lähenemisviis loob koodisõna, mis sisaldab 514 10-bitist sümbolit, mis on kodeeritud 544 sümboliplokki, mille tulemuseks on 6% ribalaius. Need FEC-koodisõnad on jaotatud AUI füüsiliste linkide vahel, nii et iga füüsiline link (8 1.6T Etherneti jaoks) ei kanna tervet koodisõna. See meetod ei paku mitte ainult täiendavat kaitset veapurskete eest, vaid võimaldab ka paralleelseerimist kaugemal dekoodris, vähendades seeläbi latentsust.

Physical Medium Attachment (PMA), millel on käigukast ja SerDes, toob Etherneti signaali edastatavatele kanalitele. 1.6T Etherneti puhul hõlmab see 8 kanalit, millest igaüks töötab kiirusega 212 Gbps, mis moodustab 6% FEC-i üldkulu. Kasutatav modulatsioonitehnika on 4-tasemeline impulsi amplituudmodulatsioon (PAM-4), mis kodeerib iga edastussümboli jaoks kaks andmebitti, kahekordistades seeläbi tõhusalt ribalaiust, kui seda kõrvutada traditsioonilise mittetagasi nulli (NRZ) lähenemisviisiga. Edastusmehhanism põhineb digitaal-analoogmuundamisel, samas kui vastuvõtuotsas tagab täpse signaali eraldamise DSP-dega kombineeritud analoog-digitaalmuundus.

Lisaks on oluline märkida, et Etherneti PCS-is on "välimine FEC", mis hõlmab Etherneti lingi otsast lõpuni. Pikema ulatusega kanalite tugevdamiseks on kavas lisada üksikute füüsiliste liinide veaparanduskiht, mis tõenäoliselt võtab kasutusele hamming-koodi FEC. Eeldatakse, et see parandus leiab selle esmase rakenduse optiliste transiiveri moodulite puhul, kus selline parandus on hädavajalik.

Joonis 2: Skeem, mis näitab täiendavat üldkulu, mis on lisatud, kui kasutatakse laiendatud ulatuseks ühendatud FEC-i.

Joonisel fig 2 kujutatud näidissüsteemis on MAC ja PCS ühendatud optilise mooduli ja kiudriba kaudu. PCS-i biti veamäär on 10-5 optilise mooduli lingil, pluss optilise lingi enda vead. Ainsa RS-FEC otsast lõpuni kasutamisest ei piisa 10 saavutamiseks-13 Etherneti standard, mis muudab lingi ebausaldusväärseks. Üks võimalus oleks eraldi RS FEC kolmekordne rakendamine igal hüppel, suurendades märkimisväärselt kulusid ja latentsust. Tõhusam lahendus on ühendatud Hamming Code FEC integreerimine spetsiaalselt optilise lingi jaoks, et rahuldada optiliste ühenduste tüüpilisi juhuslikke vigu. See sisemine FEC-kiht suurendab liinikiirust 212 Gbps-lt 226 Gbps-le, seega on oluline, et SerDes saaks seda liinikiirust toetada.

Latentsusprobleemid 1.6T Etherneti süsteemides

Joonis 3: 1.6T Etherneti alamsüsteemi latentsustee.

Etherneti latentsusaega aitavad kaasa mitmesugused komponendid: edastusjärjekord, edastuse kestus, keskmise läbimise aeg ning mitmed töötlemis- ja vastuvõtuajad. Selle visualiseerimiseks vaadake joonist 3, mis näitab kõikehõlmavat 1.6T Etherneti alamsüsteemi. Kuigi latentsust võib mõjutada kaugrakenduse reaktsiooniaeg, on see tegur Ethernetist väline ja seetõttu jäetakse latentsusanalüüsi käigus sageli välja. Latentsuse minimeerimine Etherneti liideses nõuab konkreetsete asjaolude mõistmist. Näiteks ei pruugi latentsus olla peamine probleem kommutaatorite vaheliste magistraalühenduste puhul aeglasemate kliendilinkide loomupäraste viivituste tõttu. Oma rolli mängib ka kaugus; suuremad pikkused toovad kaasa rohkem latentsust. Muidugi ei tähenda see, et peaksime teiste stsenaariumide puhul latentsust tähelepanuta jätma, latentsusaja vähendamine on alati eesmärk.

Edastamise latentsus on oma olemuselt seotud Etherneti kiiruse ja kaadri suurusega. Täpsemalt, 1.6T Etherneti süsteemi puhul on minimaalse suurusega paketi edastamiseks vajalik 0.4 ns – sisuliselt üks Etherneti kaader 2.5 GHz kella märgi kohta. Teisest küljest võtab standardse maksimaalse suurusega kaadri edastamine aega 8 ns, ulatudes Jumbo Frame'i puhul 48 ns-ni. Valitud meedium määrab veelgi latentsusaja. Näiteks optilise kiu latentsusaeg on tavaliselt 5 ns meetri kohta, samas kui vaskkaabeldus on veidi kiirem 4 ns meetri kohta.

Märkimisväärne osa üldisest latentsusest on juurdunud vastuvõtja kontrolleris. RS FEC dekooder lisab oma olemuselt latentsust. Veaparanduse käivitamiseks peab süsteem vastu võtma 4 koodisõna, mis kiirusel 1.6 Tbps on 12.8 n. Hilisemad tegevused, sealhulgas vigade parandamine ja puhverdamine, suurendavad seda latentsust. Kuigi FEC-koodisõna salvestuskestus jääb samaks, sõltub latentsus sõnumi vastuvõtmisel konkreetsest teostusest. Sellegipoolest saab latentsusaega optimeerida, kasutades täpseid digitaalse disaini strateegiaid.

Sisuliselt on FEC-mehhanismi ja füüsilise kauguse või kaabli pikkuse tõttu omane vältimatu latentsus. Lisaks nendele teguritele mängivad projekteerimisalased teadmised Etherneti kontrolleri latentsuse minimeerimisel keskset rolli. Täieliku lahenduse kasutamine, mis integreerib ja optimeerib MAC-i, PCS-i ja PHY-d, sillutab teed kõige tõhusamale ja madala latentsusajaga juurutamisele.

kokkuvõte

Joonis 4: Synopsys 224G Ethernet PHY IP esimese läbimise räni õnnestumine 3nm protsessis, mis näitab väga lineaarseid PAM-4 silmi.

1.6 Tbps Ethernet on kohandatud kõige ribalaiust nõudvate ja latentsustundlike rakenduste jaoks. 224G SerDes tehnoloogia esilekerkimisega koos MAC ja PCS IP edusammudega on nüüd saadaval terviklikud lahendused, mis vastavad pidevalt arenevatele 1.6T Etherneti standarditele. Lisaks peavad protokollile ja veaparandusmeetoditele omase latentsusaja tõttu asjatundlikud disainerid hoolikalt välja töötama IP digitaalse ja analoogse kujunduse, et vältida andmeteele tarbetut latentsust.

1.6T SoC-disainide parima jõudluse saavutamiseks on vaja tõhusalt optimeeritud arhitektuuri ja iga kiibi komponendi täpseid projekteerimisvõtteid. See rõhutab energiasäästu ja minimeerib räni jalajälge, muutes 1.6T andmeedastuskiirused reaalsuseks. Silikooniga tõestatud Synopsys 224G Ethernet PHY IP on seadnud aluse 1.6T MAC- ja PCS-kontrollerile. Kasutades tipptasemel disaini-, analüüsi-, simulatsiooni- ja mõõtmistehnikaid, pakub Synopsys jätkuvalt erakordset signaali terviklikkust ja värinat. täielik Etherneti lahendus, sealhulgas MAC+PCS+PHY.

- SEO-põhise sisu ja PR-levi. Võimenduge juba täna.

- PlatoData.Network Vertikaalne generatiivne Ai. Jõustage ennast. Juurdepääs siia.

- PlatoAiStream. Web3 luure. Täiustatud teadmised. Juurdepääs siia.

- PlatoESG. Süsinik, CleanTech, Energia, Keskkond päikeseenergia, Jäätmekäitluse. Juurdepääs siia.

- PlatoTervis. Biotehnoloogia ja kliiniliste uuringute luureandmed. Juurdepääs siia.

- Allikas: https://semiengineering.com/latency-considerations-for-1-6t-ethernet-designs/

- :on

- :on

- :mitte

- : kus

- $ UP

- 1

- 12

- 16

- 2024

- 2026

- 212

- 220

- 362

- 500

- 8

- a

- juurdepääs

- juurdepääsetav

- raamatupidamine

- täpne

- Saavutada

- üle

- tegevus

- lisatud

- Täiendavad lisad

- Lisaks

- Vastuvõtmine

- edusammud

- edeneb

- vastu

- Eesmärk

- lubatud

- juba

- Ka

- Kuigi

- alati

- keset

- summad

- võimendama

- an

- analüüs

- ja

- Oodatud

- taotlus

- rakendused

- lähenemine

- arhitektuur

- OLEME

- AS

- At

- vältima

- Back-end

- taustaks

- Bandwidth

- BE

- muutub

- vahel

- Peale

- Natuke

- Blokeerima

- toetama

- võimendamine

- Toob

- Ehitab

- kuid

- by

- kaabel

- kaablid

- CAN

- võimsused

- viima

- väljakutseid

- kanalid

- kiip

- laastud

- valitud

- asjaolusid

- klient

- kell

- Cloud

- cloud computing

- kood

- kombineeritud

- kombineerimine

- KOMMUNIKATSIOON

- täitma

- lõpetamist

- komponent

- komponendid

- terviklik

- koosnevad

- arvutustehnika

- Murettekitav

- koos

- seotud

- Side

- KAITSE

- Arvestama

- kaalutlused

- järjepidev

- pidev

- pidevalt

- aitama kaasa

- kontrollida

- kontroller

- Konverteerimine

- Copper

- tuum

- kulud

- vastu

- kursus

- meisterdatud

- loob

- Praegune

- andmed

- Datacenter

- debüüt

- viivitusi

- tarnima

- Nõudlus

- nõudlik

- nõudmisi

- kujutavad

- Disain

- disainerid

- disainilahendused

- Detection

- seadmed

- dikteerib

- erinev

- digitaalne

- püüdlikult

- Näidikute

- kaugus

- jagatud

- Ei tee

- kahekordistada

- kaks

- kestus

- ajal

- iga

- Ajalugu

- ökosüsteemi

- Tõhus

- tõhusalt

- efektiivsus

- tõhus

- tõhusalt

- jõupingutusi

- tekkimine

- rõhutab

- rõhutades

- töötavad

- tööle

- võimaldab

- võimaldades

- hõlmab

- lõpp

- Lõpuks-lõpuni

- tagab

- Kogu

- viga

- vead

- eskalatsioon

- olemus

- oluline

- põhiliselt

- Eeter (ETH)

- Isegi

- Iga

- ilmne

- areneb

- näide

- erandlik

- välja jäetud

- laiendades

- laiendamine

- oodatav

- ekspert

- teadmised

- laiendama

- laiendades

- väline

- kaevandamine

- silmad

- faktor

- tegurid

- kaugele

- kiiremini

- FUNKTSIOONID

- Lisaks

- Joonis

- leidma

- esimene

- Esimene põlvkond

- voog

- keskendunud

- Järgneb

- Jalajälg

- eest

- sõnastama

- edasi

- FRAME

- Alates

- edasi

- põlvkond

- annab

- suurem

- Grupp

- Grupi omad

- Kasvavad

- käsi

- Käsitsemine

- Suur

- suur jõudlus

- kõrgelt

- aga

- HTML

- HTTPS

- hädavajalik

- täitmine

- tähtsus

- oluline

- paranenud

- in

- Teistes

- sisaldama

- Kaasa arvatud

- kasvav

- eraldi

- tööstus-

- mõjutatud

- omane

- olemuselt

- algatama

- algatus

- Näiteks

- Integreerib

- integratsioon

- terviklikkuse

- Interface

- liidesed

- Internet

- Koostalitlusvõime

- sisse

- sisemine

- kehtestama

- Tutvustab

- sisse

- hõlmab

- IP

- IT

- kordused

- ITS

- ise

- jpg

- Sõidurada

- Hilinemine

- kiht

- kihid

- Pikkus

- taset

- võimendav

- Tõenäoliselt

- joon

- liinid

- LINK

- lingid

- elama

- enam

- Madal

- mac

- Tegemine

- juhtima

- juhtimine

- max laiuse

- maksimaalne

- mai..

- keskmine

- mõõtmine

- mehhanism

- keskmine

- Mälu

- sõnum

- meetod

- meetodid

- pedantne

- minimaalne

- minimeerima

- minimeerib

- minimeerimine

- moodul

- Moodulid

- rohkem

- kõige

- peab

- lähenemas

- Vajadus

- võrgustikud

- Sellegipoolest

- ei

- meeles

- nüüd

- eesmärk

- of

- sageli

- on

- ONE

- ainult

- tegutsevad

- optimeeritud

- Optimeerib

- valik

- or

- Muu

- üle

- üldine

- paari

- parameetrid

- eriti

- tee

- arvutid

- kohta

- jõudlus

- etendused

- füüsiline

- Füüsiliselt

- torujuhe

- Keskses

- Platon

- Platoni andmete intelligentsus

- PlatoData

- mängib

- pluss

- potentsiaal

- võim

- tavad

- eelkõige

- esmane

- protsess

- töötlemine

- töötlejad

- progressioon

- Prognooside

- kaitse

- protokoll

- pulss

- eesmärk

- Lükkamine

- kvaliteet

- raadio

- juhuslik

- valik

- määr

- Rates

- jõudma

- jõuda

- reaktsioon

- Reaalsus

- saama

- vastuvõtmine

- vastuvõtt

- vähendamine

- usaldusväärne

- jäänused

- rendering

- Vajab

- piiratud

- tulemuseks

- jõuline

- Roll

- Juurdunud

- jooksmine

- Skaalautuvus

- Skaala

- stsenaariumid

- sujuv

- Teine

- nähtud

- segment

- tundlik

- eri

- teenima

- teenus

- komplekt

- mitu

- jagatud

- Lühike

- peaks

- esitlus

- Signaali

- märgatavalt

- Räni

- simuleerimine

- SUURUS

- So

- lahendus

- Lahendused

- ulatub

- juhtroll

- konkreetse

- eriti

- täpsustus

- kiirused

- kevad

- Stage

- standard

- standardimine

- standardite

- ladustamine

- strateegiad

- streaming

- järgnev

- mahukas

- edu

- selline

- sobiv

- toetama

- sümbol

- süsteem

- kohandatud

- võtab

- tehnika

- tehnikat

- Tehnoloogia

- kui

- et

- .

- oma

- Seal.

- sellega

- seetõttu

- Need

- see

- Läbi

- Seega

- puuk

- seotud

- aeg

- korda

- et

- ülemine

- traditsiooniline

- liiklus

- üle

- edastama

- Kolmekordne

- kaks

- tüüpiline

- tüüpiliselt

- vältimatu

- mõistmine

- võtma

- üksus

- tulemas

- peale

- kasutamine

- ära kasutama

- kaudu

- visualiseeri

- Tee..

- we

- millal

- mis

- kuigi

- laiem

- koos

- jooksul

- oleks

- veel

- sephyrnet

- null