Integraallülituse terminoloogias on langus pingelangus, mis toimub vooluringis. See on üldtuntud nähtus ja võib juhtuda järgmistel põhjustel. Toiteallikas langeb alla töövahemiku, mille jaoks kiip oli mõeldud, mille tulemuseks on langus. Juhtivad elemendid võtavad rohkem voolu, kui need on ette nähtud, mille tulemuseks on langus. Mõnikord võivad pinge kõikumised põhjustada ka signaali häired või müra toiteallikas, mille tulemuseks on pinge langus.

Langused võivad mõjutada vooluringi toimimist. Üheks selliseks mõjuks on kiibi vähenenud jõudlus, mis põhjustab pikemat töötlemisaega. Kuid järgmised on mõned tõsisemad ja/või katastroofilisemad tagajärjed. Kiip võib jõudluse säilitamiseks kasutada rohkem voolu, mis suurendab energiatarbimist ja soojuse hajumist. See võib kaasa tuua kiibi eluea lühenemise ja rasketel juhtudel kiibi täieliku rikke seadistuse ja hoidmise erinevuste tõttu. Langused võivad põhjustada ka andmete rikkumist või vigu väljundis. See on väga tõsine probleem rakenduste jaoks, mis sõltuvad kiibi täpsusest ja töökindlusest.

Loomulikult võetakse kiipide ja süsteemide projekteerimisel tõsiselt arvesse kukkumise nähtust. Kõige levinumad meetodid languse leevendamiseks on toiteallika lahtisidumine, pinge reguleerimine, vooluahela optimeerimine ja süsteemi tasemel toitehaldus. Tingimusi ja töökeskkonda, milles kiip töötab, kaalutakse hoolikalt läbi kukkumist leevendavate lahenduste kavandamisel.

Tänapäeva probleemid

Kuna SoC-d muutuvad keerukamaks, võivad ka rippumisprobleemid muutuda üsna keeruliseks. SoC-i disain tuleb optimeerida jõudluse, võimsuse, kulude, vormiteguri jms jaoks, lisaks optimeerimisele allakukkumise leevendamiseks. Mõnikord võivad need optimeerimiseesmärgid üksteisega konkureerida ja minna vastuollu ning teha tuleb kompromisse. Näiteks võivad SoC-arhitektid tõsta tööpinget, lisades varu, et vältida kohalikku ja globaalset langust, kuid see tõus suurendab võimsust ruutkeskmiselt. Teise võimalusena võivad disainerid lasta oma kella genereerimisel kohaneda langusega, mis muudab jõudluse kella genereerimise lülitusaja funktsiooniks.

Järelikult on andmekeskuse arvutustes ja tehisintellekti ruumis olevad suured SoC-d märkimisväärselt vastuvõtlikud kukkumisele. Klientide töökoormus on väga mitmekesine ja dünaamiline, mis toob kaasa olulisi kõikumisi vahetustegevuses ja voolutarvetes. Loomulikult ei saa süsteemid endale lubada, et vajunud probleeme ei lahendata. Võimalik vastutus ebatäpse väljundi või kiibi katastroofilise rikke tõttu on tänapäevaste süsteemide ja rakenduste jaoks liiga kõrge.

Lokaliseeritud kukkumisprobleemid

Rakendusspetsiifilisi kiirendeid kasutatakse laialdaselt koos üldotstarbeliste protsessoritega, et pakkuda tänapäeva nõudlikes andmetöötluskeskkondades nõutavat jõudlust ja energiatõhusust. Kuid need kiirendid, samuti kasvav südamike arv ja töökoormuse asümmeetrilisus suurendavad lokaliseeritud pingelanguse ohtu. Need lokaliseeritud pingelangused on tingitud lülitusaktiivsuse järsust suurenemisest ja võivad põhjustada mööduvaid tõrkeid ja võimalikke missioonirežiimi tõrkeid.

Lokaalse languse korral saab mõju leevendada dünaamilise sageduse skaleerimisega. See saavutatakse ahela ajastuse reguleerimisega programmeeritava kella abil. Programmeeritav kell võimaldab kella sagedust ja ajastust dünaamiliselt reguleerida, lähtudes ahela praegustest töötingimustest.

Movellus muudab lokaliseeritud kukkumiste käsitlemise lihtsaks

Juhtiv digitaalse süsteemi IP-teenuse pakkuja Movellus on välja töötanud Aeonic Generate'i tooteperekonna, et lahendada lokaliseeritud hälbeid. Movellus Aeonicu portfell pakub adaptiivseid kellalahendusi, mis tagavad kiire langusele reageerimise. Portfell sisaldab adaptiivset kellasüsteemi. Ehitusplokid on ehitatud sünteesitavast Verilogist, mis muudab need olemuslikult paindlikuks. Lahendused on konfigureeritavad, skannitavad ja protsessi kaasaskantavad paljude täiustatud SoC-rakenduste jaoks.

Aeonic Generate tooteperekond on ka oluliselt väiksem kui traditsioonilised analooglahendused. Selle tulemusena saavad disainerid IP-d luua vajaliku detailsusega, ilma et see piirkonda oluliselt mõjutaks. Lisaks sellele, kui disainilahendused liiguvad peenemate protsessigeomeetriate poole, jätkub Aeonic Generate'i ala skaleerimine, muutes selle ideaalseks lahenduseks tulevaste kujunduste jaoks.

Paar kasutusjuhtu

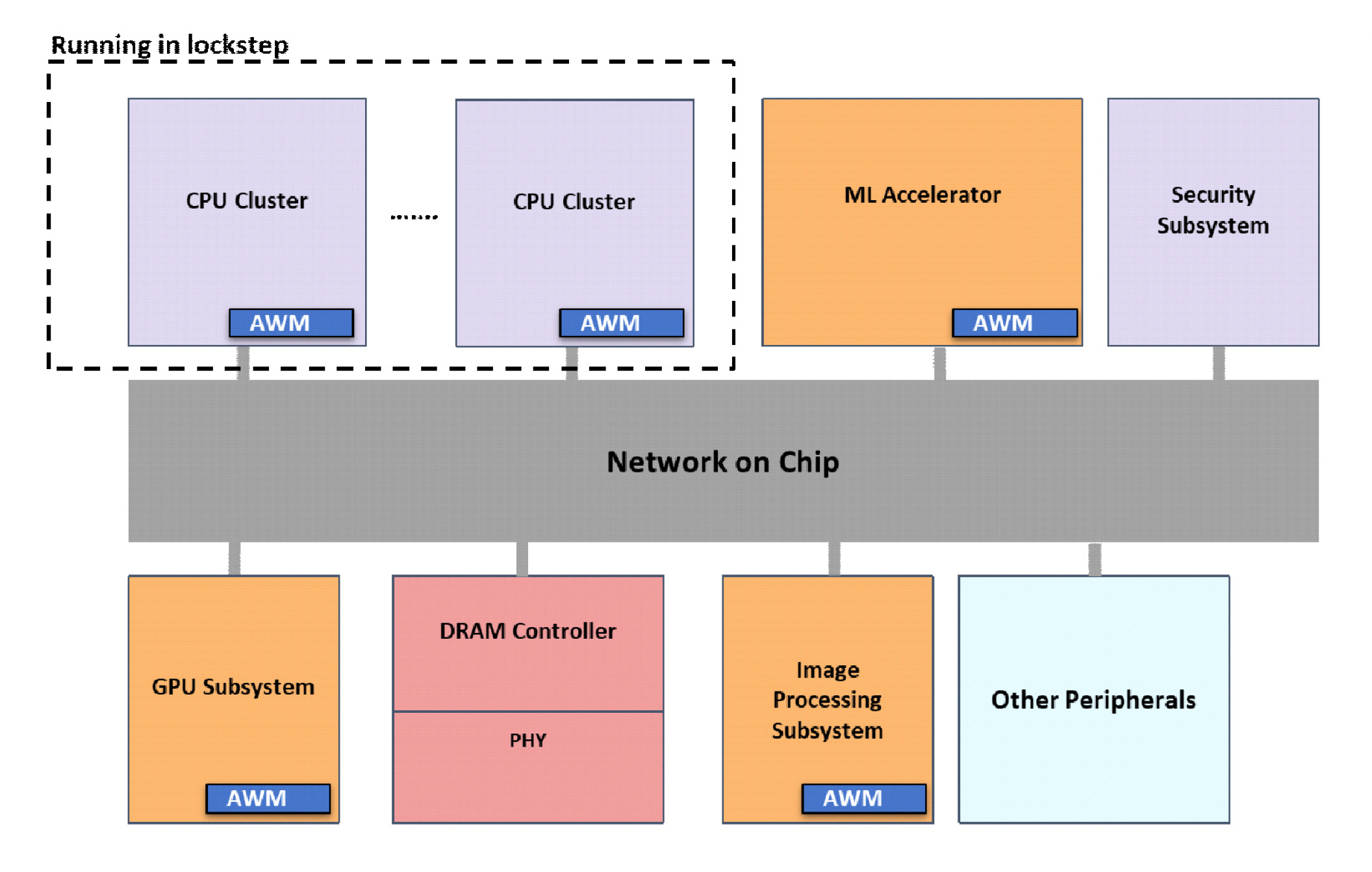

Järgmisel Movelluse joonisel on näidatud ADAS-protsessori arhitektuuri näide koos Aeonic Generate AWM platvormiga lokaliseeritud languse toetamiseks. Arhitekt ühendab AWM-mooduli rakendusespetsiifilise alamploki või kiirendiga, et reageerida töökoormusest tingitud lokaliseeritud langustele viie kellatsükli jooksul ilma tõrgeteta ja kiirete sagedusnihketega. See lähenemine pakub usaldusväärset ja tõhusat lahendust ADAS-i, 5G ja andmekeskuste võrguturgudel esinevate lokaliseeritud katkestuste probleemide lahendamiseks.

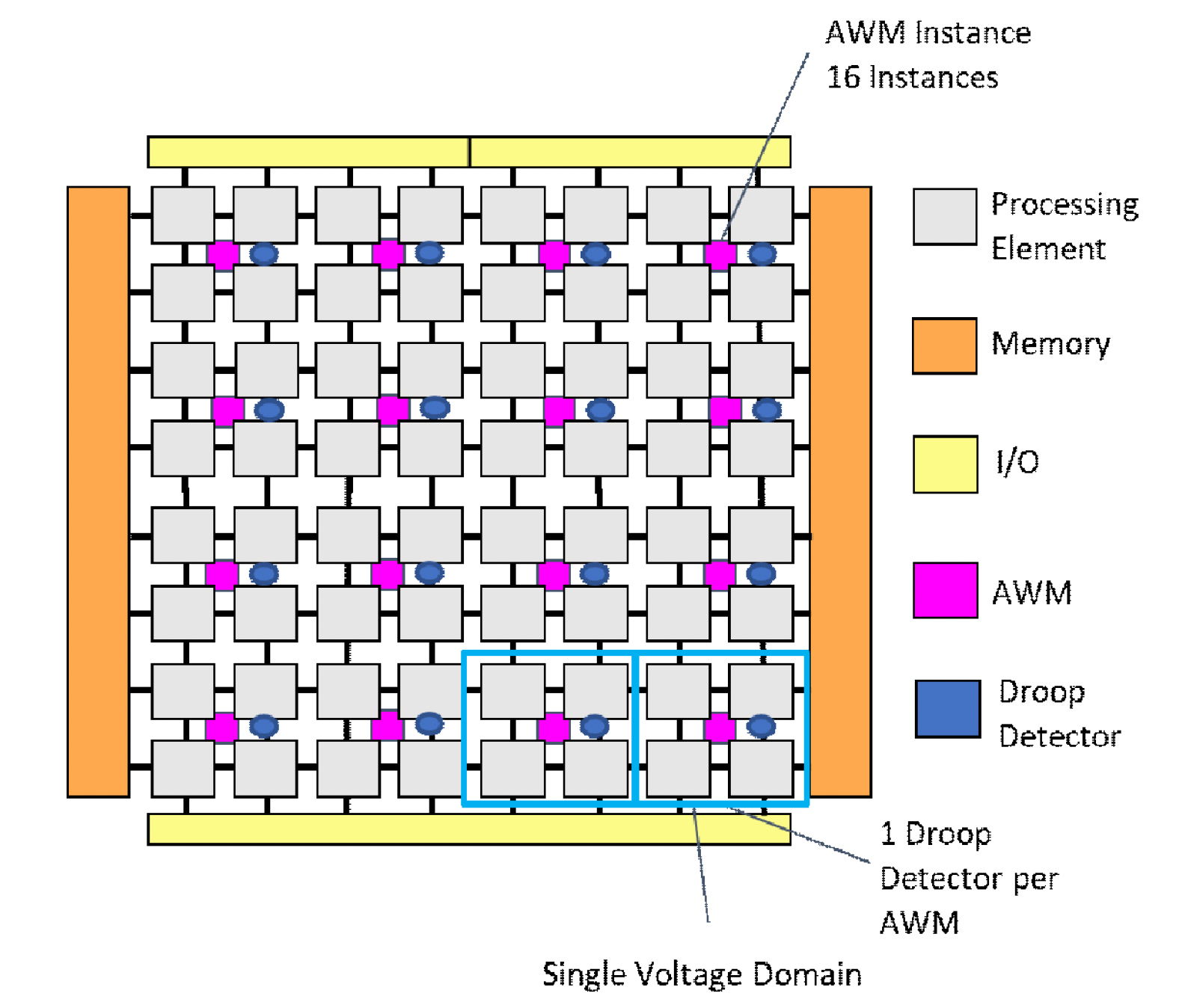

Järgmisel Movelluse joonisel on kujutatud Aeonic Generate'i protsessor-SoC-i arhitektuuri näidet lokaliseeritud rikketoe jaoks. Arhitekt ühendaks Aeonic Generate AWM mooduli protsessori klastri ja sellega seotud pingedomeeni rikkedetektoriga, et kiiresti reageerida töökoormusest tingitud lokaliseeritud langustele. See võimaldab disaineritel pakkuda lokaliseeritud ja sõltumatut langusreaktsiooni, muutmata naaberprotsessoriklastrite jõudlust.

kokkuvõte

Kohalikud pingelangused võivad esineda heterogeensetes SoC-des, mis sisaldavad rakendusespetsiifilisi kiirendeid. Need kõrvalekalded võivad ADAS-is, andmekeskuste võrkudes ja 5G rakendustes põhjustada ajastustõrkeid, mööduvaid tõrkeid ja missioonirežiimi tõrkeid. Süsteemiarhitektid saavad nendele langustele reageerimiseks ja mõju leevendamiseks rakendada adaptiivset takti.

Movellus™ Aeonic Generate Adaptive Workload Module (AWM) suure jõudlusega kella genereerimise IP-toodete perekond on osa Aeonic Intelligent Clock Network™ arhitektuurist. Lisateabe saamiseks vaadake Movelluse Aeonic Generate™ AWM leht.

Samuti loe:

Suuremahuliste sünkroonse kellaaja domeenide eelised tehisintellekti kiipide disainides

Nüüd on aeg nutikella võrkude jaoks

Jõudluse, võimsuse ja pindala (PPA) eelised intelligentsete kellavõrkude kaudu

Jaga seda postitust:- SEO-põhise sisu ja PR-levi. Võimenduge juba täna.

- Platoblockchain. Web3 metaversiooni intelligentsus. Täiustatud teadmised. Juurdepääs siia.

- Allikas: https://semiwiki.com/ip/326488-adaptive-clock-technology-for-real-time-droop-response/

- :on

- 5G

- a

- kiirendi

- kiirendid

- täpsus

- saavutada

- tegevus

- kohandama

- ADA-d

- lisamine

- Lisaks

- aadress

- adresseerimine

- Kohandatud

- edasijõudnud

- AI

- võimaldab

- ja

- rakendused

- lähenemine

- arhitektuur

- OLEME

- PIIRKOND

- AS

- seotud

- At

- põhineb

- BE

- muutuma

- alla

- Kasu

- Blokeerima

- Plokid

- Ehitus

- ehitatud

- by

- CAN

- Saab

- ei saa

- hoolikalt

- juhtudel

- katastroofiline

- Põhjus

- keskus

- väljakutseid

- kiip

- laastud

- kell

- Cluster

- ühine

- võistlema

- täitma

- keeruline

- Arvutama

- arvutustehnika

- Tingimused

- tasu

- kaaluda

- tarbimine

- pidev

- Korruptsioon

- Maksma

- võiks

- Võidelda

- Paar

- kursus

- Praegune

- klient

- tsüklit

- andmed

- Andmekeskus

- Datacenter

- päev

- tarnima

- nõudlik

- Disain

- kavandatud

- disainerid

- projekteerimine

- disainilahendused

- arenenud

- digitaalne

- jagatud

- mitu

- domeen

- Domeenid

- koostatud

- Drop

- Tilgad

- dünaamiline

- dünaamiliselt

- iga

- efektiivsus

- tõhus

- elemendid

- keskkond

- keskkondades

- vead

- jms

- näide

- ebaedu

- juga

- pere

- Joonis

- paindlik

- kõikumisi

- Järel

- eest

- vorm

- Sagedus

- Alates

- funktsioon

- tulevik

- Üldine otstarve

- tekitama

- põlvkond

- saama

- Globaalne

- Go

- Eesmärgid

- juhtuda

- juhtub

- Olema

- Suur

- suur jõudlus

- hoidma

- HTTPS

- ideaalne

- mõju

- Mõjud

- rakendada

- in

- ebatäpne

- hõlmab

- Suurendama

- kasvanud

- Tõstab

- kasvav

- sõltumatud

- info

- integreeritud

- integratsioon

- Intelligentne

- olemuselt

- IP

- probleem

- küsimustes

- IT

- suur

- suuremahuline

- viima

- juhtivate

- Tase

- vastutus

- elu

- kohalik

- enam

- tehtud

- säilitada

- TEEB

- Tegemine

- juhtimine

- Varu

- turud

- max laiuse

- meetodid

- Leevendada

- leevendav

- leevendamine

- moodul

- Moodulid

- rohkem

- kõige

- liikuma

- loodus

- vajadustele

- võrk

- võrgustike loomine

- müra

- eelkõige

- number

- of

- Pakkumised

- on

- ONE

- tegutsevad

- Operations

- optimeerimine

- optimeeritud

- optimeerimine

- Muu

- väljund

- osa

- jõudlus

- esitades

- nähtus

- inimesele

- Platon

- Platoni andmete intelligentsus

- PlatoData

- portfell

- post

- potentsiaal

- võim

- Laboratooriumi toiteallikas

- protsess

- töötlemine

- Protsessor

- töötlejad

- Toodet

- tarnija

- annab

- tõstma

- valik

- kiire

- kiiresti

- Lugenud

- reaalajas

- põhjustel

- Lühendatud

- Määrus

- usaldusväärsus

- usaldusväärne

- nõutav

- Reageerida

- vastus

- kaasa

- tulemuseks

- Tõusma

- Oht

- jooks

- Skaala

- ketendamine

- SEA

- tõsine

- seade

- raske

- Vahetused

- Näitused

- Signaali

- märkimisväärne

- märgatavalt

- väiksem

- nutikas

- lahendus

- Lahendused

- mõned

- Ruum

- selline

- äkiline

- varustama

- toetama

- vastuvõtlik

- süsteem

- süsteemid

- Tandem

- Tehnoloogia

- terminoloogia

- et

- .

- Piirkond

- oma

- Neile

- Need

- Läbi

- aeg

- korda

- ajastamine

- et

- tänane

- liiga

- traditsiooniline

- kasutama

- väga mitmekesine

- kaudu

- Pinge

- Hästi

- hästi tuntud

- mis

- lai

- Lai valik

- laialdaselt

- will

- koos

- jooksul

- ilma

- oleks

- sephyrnet