Investigadores de la Universidad de Stuttgart, UC Berkeley, el Instituto Indio de Tecnología de Kanpur y la Universidad Técnica de Múnich publicaron un nuevo documento técnico titulado "Diseño no tradicional de lógicas dinámicas utilizando FDSOI para computación ultraeficiente", con financiación de la Fundación Alemana de Investigación. .

Compendio

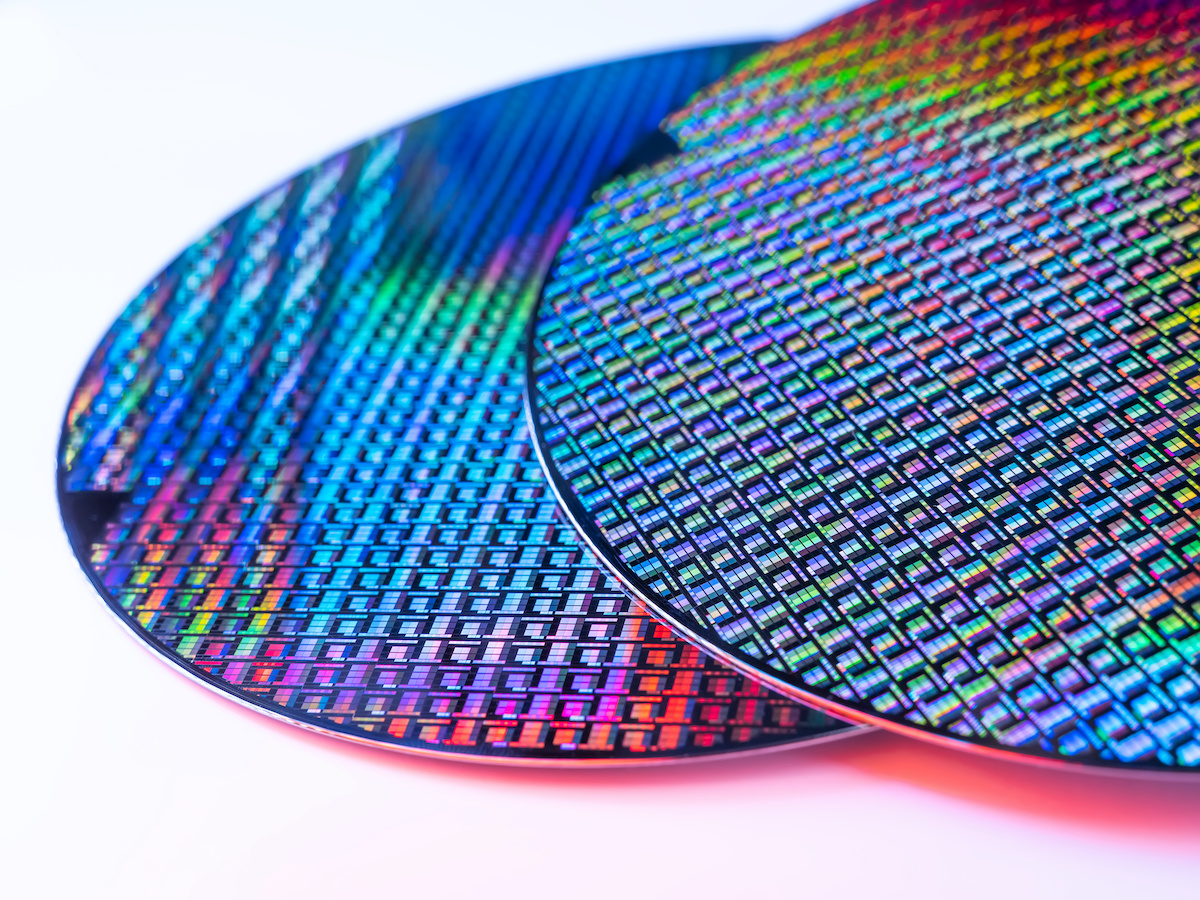

“En este documento, proponemos un diseño no tradicional de circuitos lógicos dinámicos utilizando FET de silicio sobre aislante totalmente agotado (FDSOI). FDSOI FET permite el voltaje de umbral (Vt ) para ser ajustable (es decir, estados de Vt bajo y Vt alto) mediante el uso de la polarización de la puerta trasera. Nuestro diseño utiliza las puertas delantera y trasera de un FET FDSOI como terminales de entrada y propone puertas lógicas dinámicas (como NAND, NOR, AND, OR, XOR y XNOR) y circuitos (como medio sumador y sumador completo). Requiere menos transistores para construir puertas lógicas dinámicas y logra un alto rendimiento con una disipación de potencia baja en comparación con los diseños lógicos dinámicos convencionales. El modelo industrial compacto de FDSOI FET (BSIM-IMG) se ha utilizado para simular puertas lógicas dinámicas y está completamente calibrado para reproducir los datos del nodo de tecnología FDSOI FET de 14 nm. La calibración se realiza tanto para las características eléctricas como para las variaciones del proceso. Los resultados de la simulación muestran una mejora promedio en el recuento de transistores, el retraso de propagación, la potencia y el producto potencia-retraso del 23.43 %, 57.16 %, 47.05 % y 77.29 %, respectivamente, en comparación con los diseños convencionales. Además, nuestro diseño reduce el efecto de carga compartida, que afecta la capacidad de conducción de las puertas lógicas dinámicas. Además, hemos analizado en detalle el impacto del proceso, la tensión de alimentación y las variaciones de la capacidad de carga en el retardo de propagación de la familia lógica dinámica. Los resultados muestran que estas variaciones tienen un impacto menor en el retraso de propagación de las puertas lógicas dinámicas basadas en FDSOI propuestas en comparación con las puertas lógicas dinámicas convencionales”.

Encuentra los documento técnico aquí. Publicado en abril de 2023.

S. Kumar, S. Chatterjee, CK Dabhi, YS Chauhan y H. Amrouch, "Diseño no tradicional de lógica dinámica mediante FDSOI para computación ultraeficiente", en IEEE Journal on Exploratory Solid-State Computational Devices and Circuits, doi: 10.1109/JXCDC.2023.3269141. Acceso abiertos.

- Distribución de relaciones públicas y contenido potenciado por SEO. Consiga amplificado hoy.

- PlatoAiStream. Inteligencia de datos Web3. Conocimiento amplificado. Accede Aquí.

- Acuñando el futuro con Adryenn Ashley. Accede Aquí.

- Compra y Vende Acciones en Empresas PRE-IPO con PREIPO®. Accede Aquí.

- Fuente: https://semiengineering.com/non-traditional-design-of-dynamic-logic-gates-and-circuits-with-fdsoi-fets/

- :posee

- :es

- 10

- 2023

- 23

- 77

- a

- Logra

- adición

- ajustable

- permite

- an

- y

- Abril

- AS

- At

- promedio

- Atrás

- BE

- esto

- Berkeley

- parcialidad

- ambas

- build

- by

- características

- CHARGE

- en comparación con

- informática

- convencional

- datos

- retrasar

- Diseño

- diseños

- detalle

- Dispositivos

- lugar de trabajo dinámico

- e

- efecto

- familia

- FET

- menos

- Fundación

- frontal o trasero

- ser completados

- completamente

- universidad

- promover

- -

- Alemán

- Mitad

- Tienen

- Alta

- HTTPS

- i

- IEEE

- Impacto

- es la mejora continua

- in

- Indian

- industrial

- Las opciones de entrada

- Innovadora

- IT

- revista

- como

- carga

- lógica

- Baja

- menor de edad

- modelo

- Munich

- Nuevo

- nodo

- of

- on

- or

- nuestros

- Papel

- actuación

- Platón

- Inteligencia de datos de Platón

- PlatónDatos

- industria

- Producto

- ofrece

- propuesto

- propone

- publicado

- reduce

- requiere

- la investigación

- investigadores

- respectivamente

- Resultados

- s

- compartir

- Mostrar

- Silicio

- simulación

- Zonas

- suministro

- Técnico

- Tecnología

- esa

- El

- Estas

- así

- umbral

- titulada

- a

- universidad

- usado

- usando

- utiliza

- Tensión

- fue

- we

- que

- zephyrnet