La vieja frase de que la cura es peor que la enfermedad es pertinente cuando se habla de MBIST para grandes SOC donde ejecutar muchas pruebas de MBIST en paralelo puede exceder las capacidades de la red de distribución de energía (PDN). La autoprueba integrada de memoria (MBIST) generalmente se ejecuta automáticamente durante los eventos de encendido. Debido al deseo de acelerar los tiempos de prueba y arranque del chip, estas pruebas se ejecutan con frecuencia en paralelo. El problema es que pueden producir fácilmente una actividad de conmutación que está un orden de magnitud por encima de los niveles que se encuentran durante el funcionamiento normal del chip. De hecho, estos niveles más altos de actividad de conmutación no solo pueden causar una caída del suministro que afecte los resultados de la prueba, sino que también el alto calor generado puede dañar los chips. Estos efectos pueden dar lugar a un agrupamiento incorrecto o a fallos directos y latentes de eventos.

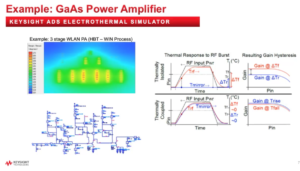

La solución es simular la actividad MBIST para predecir la carga en la PDN y los efectos térmicos relacionados. Con los resultados de la simulación en la mano, los diseñadores pueden decidir correctamente cuántos y qué bloques de memoria se pueden probar en paralelo. Sin embargo, esto no siempre es factible en SOC grandes con muchos bloques de memoria porque los tiempos de simulación pueden ser prohibitivos. Con el nivel de puerta e incluso una simulación RTL menos precisa, puede que no sea posible ejecutar suficientes ciclos para obtener la información necesaria.

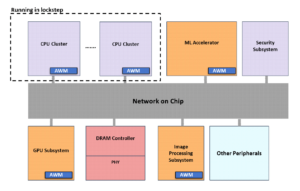

En un documento técnico titulado "Analizar las implicaciones energéticas del uso de MBIST", Siemens EDA analiza cómo los diseñadores pueden ejecutar suficiente simulación para tomar decisiones informadas sobre la estrategia de prueba antes de la finalización. Siemens trabajó con ARM en uno de sus chips de prueba para crear un caso de prueba en el que pudieran aplicar la emulación de hardware con las aplicaciones DFT y Power para el emulador de hardware de Siemens Veloce. Primero, la aplicación Veloce DFT se usa para generar la actividad interna durante la emulación MBIST. La aplicación utiliza el lenguaje de interfaz de prueba estándar (STIL) y produce archivos de salida estándar de la industria.

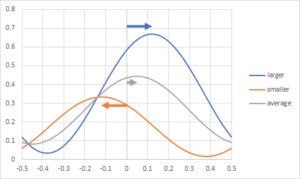

La aplicación Veloce Power toma la información de actividad de las ejecuciones de MBIST para generar formas de onda, perfiles de energía y mapas de calor que pueden indicar cuándo hay picos de energía por encima de los límites especificados. Con esta información, los ingenieros de pruebas pueden tomar decisiones informadas sobre la secuenciación de MBIST.

El caso de prueba ARM descrito en el libro blanco de Siemens contiene 176 millones de puertas. Siemens utilizó un sistema Veloce con 6 placas Veloce Strato para este caso de prueba. La ejecución del emulador Veloce tomó solo 26 horas, que es 15,600 XNUMX veces más rápido que la simulación a nivel de puerta. Otro beneficio del flujo de Veloce es que la aplicación Power transmite la información de la actividad a las herramientas eléctricas en el flujo, lo que ahorra tiempo y espacio en el disco. Los resultados del caso de prueba mostraron varios picos de energía que violaron las especificaciones de diseño del SOC. El resultado de la aplicación Veloce Power muestra los niveles de potencia total a través de la simulación junto con las contribuciones de potencia separadas para el reloj, la lógica combinacional y la memoria. Asimismo, hay información sobre en qué parte del dado se está utilizando el poder. Esta información facilita la determinación de dónde hay problemas.

Encontrar problemas como estos requiere ejecutar millones o miles de millones de ciclos de reloj. Las limitaciones de los simuladores de software hacen prohibitivo realizar el análisis necesario. La emulación ofrece una vía única para examinar de cerca los impactos energéticos de MBIST y otras operaciones de prueba mucho antes que el silicio. El libro blanco de Siemens ofrece información sobre el método de potencia utilizado en un caso de prueba real. El libro blanco está disponible para descargar y leer en el sitio web de Siemens.

Comparte esta publicación a través de: Fuente: https://semiwiki.com/eda/306889-mbist-power-creates-lurking-danger-for-socs/

- Acerca

- análisis

- applicación

- aplicaciones

- ARM

- Hoy Disponibles

- "Ser"

- Causar

- chip

- Papas fritas

- Reloj

- contiene

- podría

- cura

- Diseño

- Enfermedades

- durante

- pasan fácilmente

- certificados

- Evento

- Eventos

- más rápida

- Nombre

- de tus señales

- encontrado

- -

- generar

- Materiales

- Alta

- Cómo

- HTTPS

- energético

- información

- IT

- idioma

- large

- Lead

- Nivel

- carga

- Largo

- Mapas

- millones

- millones

- del sistema,

- Ofertas

- Operaciones

- solicite

- Otro

- Papel

- industria

- Problema

- Perfiles

- Reading

- Resultados

- Ejecutar

- correr

- ahorro

- Siemens

- simulación

- Software

- Espacio

- velocidad

- Estrategia

- streaming

- suministro

- te

- test

- Pruebas

- pruebas

- térmico

- A través de esta formación, el personal docente y administrativo de escuelas y universidades estará preparado para manejar los recursos disponibles que derivan de la diversidad cultural de sus estudiantes. Además, un mejor y mayor entendimiento sobre estas diferencias y similitudes culturales permitirá alcanzar los objetivos de inclusión previstos.

- equipo

- único

- generalmente

- Página web

- detalles de la moneda

- trabajado