Synopsys ha publicado en el sitio SolvNet una fascinante charla impartida por el Dr. Theo Drane de Intel Graphics. El tema es la verificación de equivalencia de rutas de datos. Puede parecer simplemente otro respaldo formal de DPV de Synopsys VC, pero debería verlo de todos modos. Esta es una discusión que amplía la mente sobre los usos y consideraciones en el ámbito formal y que lo llevará más allá de la rutinaria presentación de la guía del usuario hacia un territorio más fascinante.

Comprensión intelectual versus pruebas de muestra

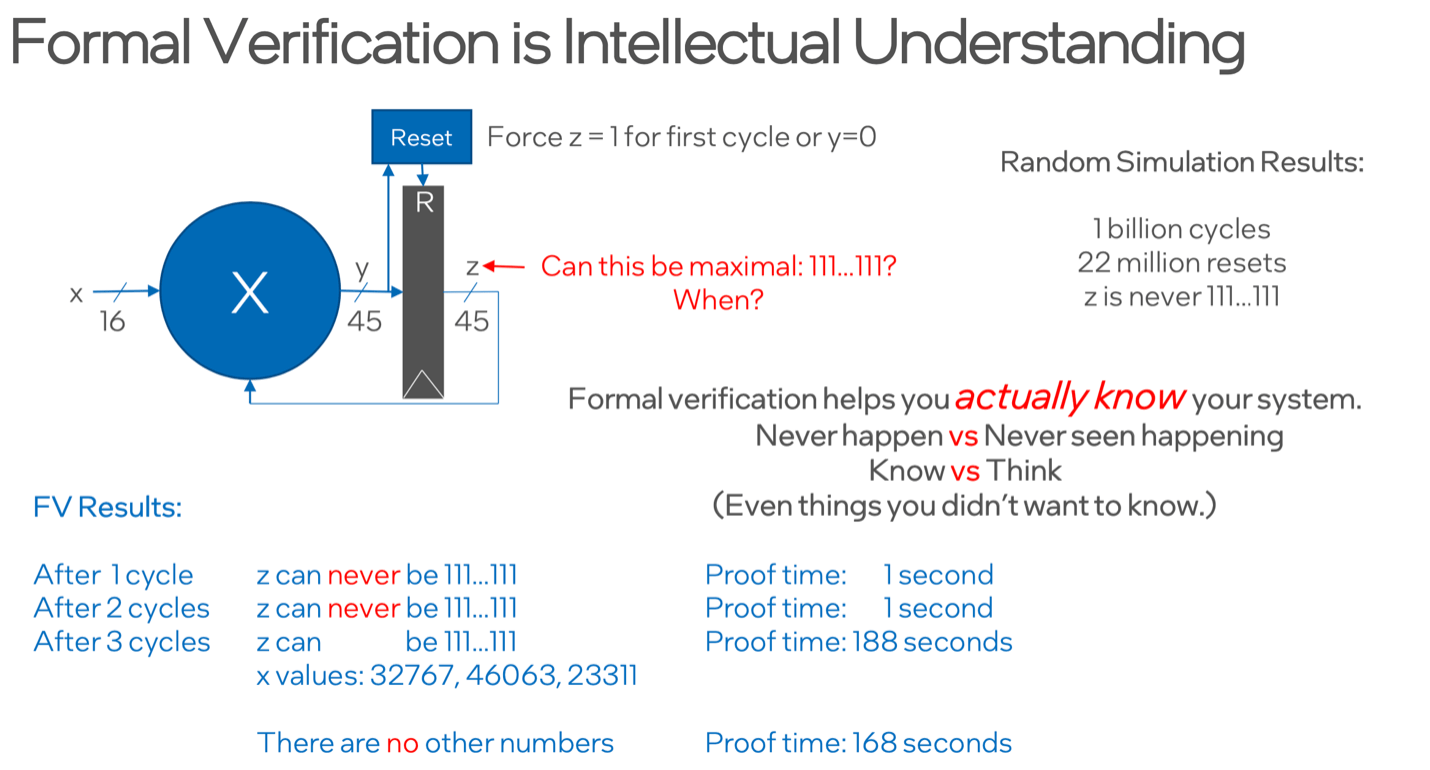

La simulación basada en pruebas en todas sus formas es excelente y, a menudo, insustituible para verificar la exactitud de una especificación o implementación de diseño. También es fácil empezar. Simplemente escriba un programa de prueba y comience a simular. Pero la otra cara de esa simplicidad es que no necesitamos completamente Entienda lo que estamos probando para comenzar. Nos convencemos de que hemos leído las especificaciones detenidamente y entendemos todos los casos extremos, pero no hace falta mucha complejidad para abrumar nuestra comprensión.

Formal lo alienta a comprender la funcionalidad en un nivel profundo (al menos si desea ofrecer un resultado valioso). En el ejemplo anterior, una pregunta simple (¿puede z alguna vez ser todo unos?) no logra demostrar un ejemplo en mil millones de ciclos en un simulador. No es sorprendente, ya que se trata de un caso extremo. Una prueba formal proporciona un ejemplo específico y muy poco obvio en 1 segundos y puede demostrar que este es el único caso así en un tiempo ligeramente menor.

OK, formal hizo lo que las pruebas dinámicas no pudieron hacer, pero lo más importante es que aprendió algo que el simulador quizás nunca le hubiera dicho. Que sólo había un caso posible en el que esa condición podía darse. Formal le ayudó a comprender mejor el diseño a nivel intelectual, no solo como un resumen probabilístico en un conjunto finito de casos de prueba.

Problemas de especificaciones

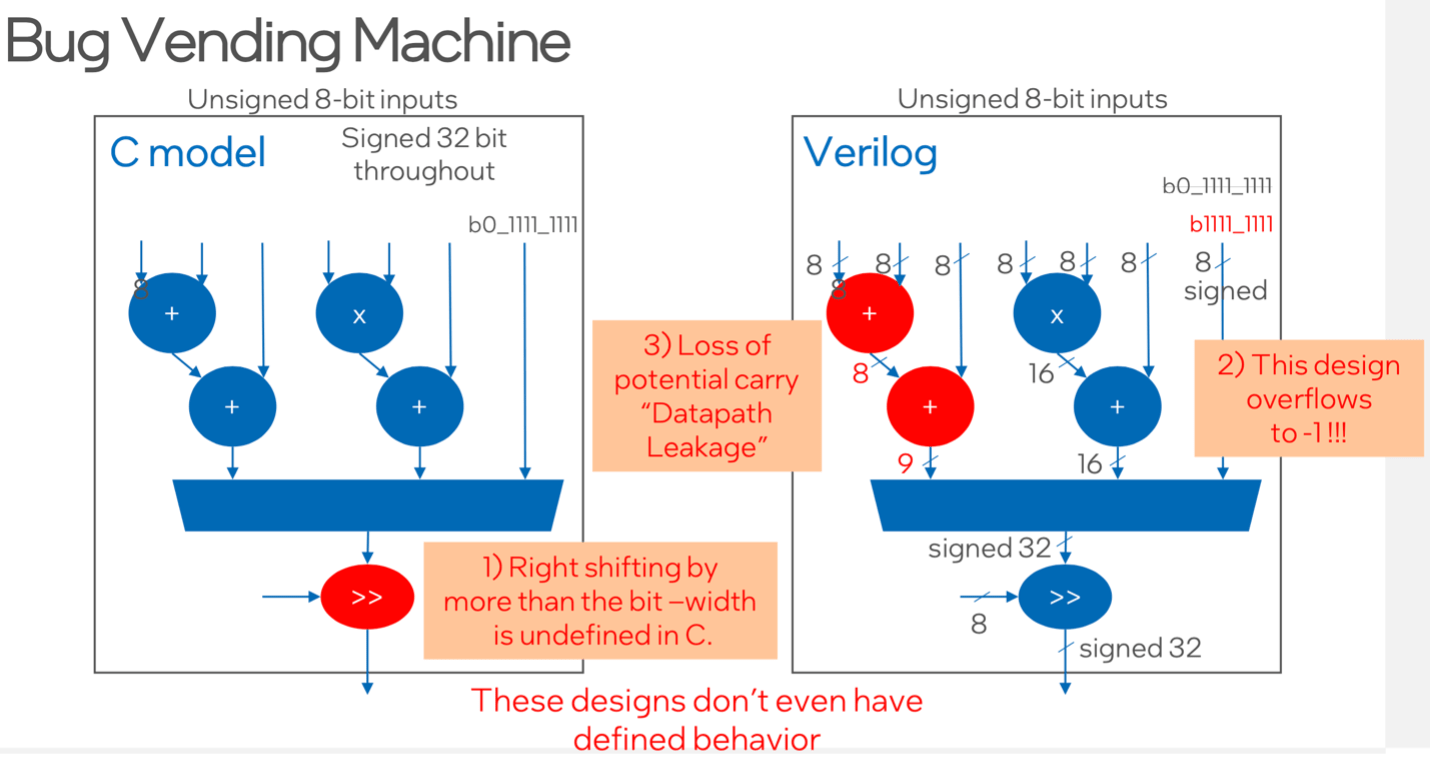

El siguiente ejemplo de Theo se basa en una máquina expendedora de errores (llamada así porque cuando presionas un botón aparece un error). Esto parece un problema de verificación de equivalencia de C a RTL bastante sencillo, modelo C a la izquierda, modelo RTL a la derecha. Una sorpresa para Theo en sus primeros días en el mundo formal fue que el comportamiento de desplazamiento a la derecha en el modelo C no está completamente definido en el estándar C, aunque gcc se comportará razonablemente. Sin embargo, DPV se quejará, como debería ser, de una discrepancia en la comparación con RTL. Es peligroso confiar en el comportamiento indefinido.

La comparación de especificaciones entre C y RTL conlleva otros peligros, especialmente en torno al ancho de las brocas. El truncamiento o la pérdida de un bit de acarreo en una señal intermedia (n.º 3 anterior) son buenos ejemplos. ¿Son estos problemas de especificaciones? Quizás haya un área gris entre las opciones de especificación e implementación.

Más allá de la verificación de equivalencia

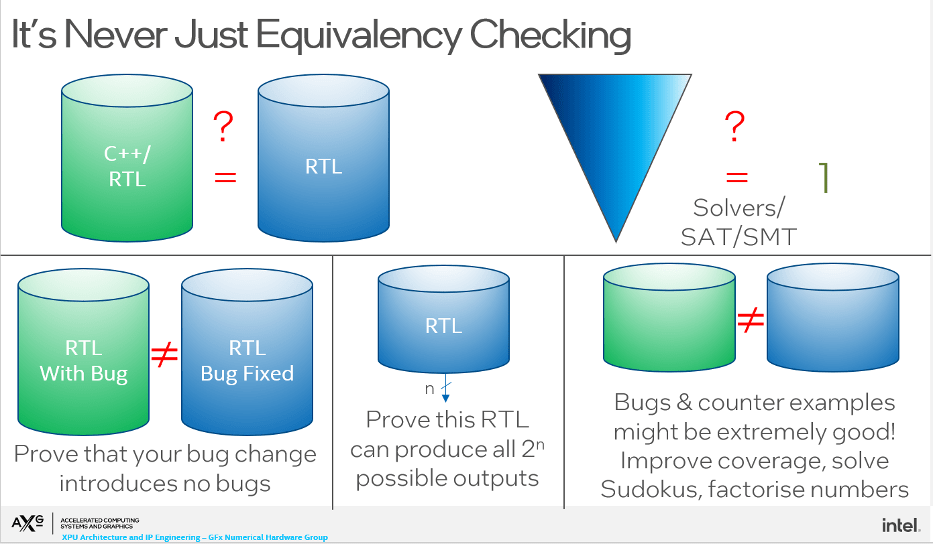

Al parecer, el objetivo principal de DPV es comprobar la equivalencia entre una referencia C o RTL y una implementación RTL. Pero esa necesidad es relativamente infrecuente y hay otras maneras útiles en que se podría aplicar dicha tecnología, aunque un poco fuera de lo común. Primero, un clásico en el mundo de la implementación: hice un cambio, solucioné un error, ¿introduje algún error nuevo como resultado? Un poco como la verificación SEQ después de agregar la activación del reloj. El análisis de accesibilidad en salidas de bloques puede ser otra aplicación útil en algunos casos.

Theo se vuelve aún más creativo y pide a los alumnos que utilicen contraejemplos para comprender mejor el diseño. resolver sudokus or factorizar números enteros. Reconoce que la DPV es una forma extraña de abordar estos problemas, pero señala que su intención es romper la ilusión de que la DPV sirve sólo para comprobar la equivalencia. Una idea interesante y, sin duda, un esfuerzo cerebral para pensar en estos desafíos. (Confieso que inmediatamente comencé a pensar en el problema del Sudoku tan pronto como lo mencionó).

Envolver

Theo concluye con una discusión sobre metodologías importantes en el uso de producción, en torno a restricciones, regresiones y comparaciones con modelos RTL heredados. También los desafíos de saber si lo que estás comprobando realmente coincide con la especificación de lenguaje natural de alto nivel.

Charla muy energizante, vale la pena verla. aquí en SolvNet!

Comparte esta publicación a través de:

- Distribución de relaciones públicas y contenido potenciado por SEO. Consiga amplificado hoy.

- Platoblockchain. Inteligencia del Metaverso Web3. Conocimiento amplificado. Accede Aquí.

- Fuente: https://semiwiki.com/eda/325878-intel-keynote-on-formal-a-mind-stretcher/

- :es

- a

- Nuestra Empresa

- arriba

- a través de

- Después

- Todos

- análisis

- y

- Otra

- Aplicación

- aplicada

- enfoque

- somos

- Reservada

- en torno a

- AS

- At

- basado

- BE

- porque

- mejores

- entre

- Más allá de

- mil millones

- Poco

- Bloquear

- Box

- Descanso

- Error

- loco

- .

- by

- , que son

- PUEDEN

- estudiar cuidadosamente

- llevar

- case

- cases

- ciertamente

- retos

- el cambio

- comprobar

- comprobación

- opciones

- clásico

- Reloj

- comparación

- completamente

- complejidad

- condición

- consideraciones

- restricciones

- convencer

- Esquina

- podría

- Para contrarrestar

- Estudio

- de ciclos

- peligroso

- Días

- profundo

- se define

- entregamos

- demostrar

- Diseño

- HIZO

- discusión

- No

- No

- lugar de trabajo dinámico

- Temprano en la

- anima

- especialmente

- Incluso

- NUNCA

- ejemplo

- ejemplos

- excelente,

- extremo

- falla

- fascinante

- Nombre

- fijas

- Dar la vuelta

- formal

- Formularios

- a la fatiga

- GCC

- obtener

- dado

- candidato

- gráficos

- gris

- área gris

- suceder

- Tienen

- ayudado

- Sin embargo

- HTTPS

- i

- idea

- inmediatamente

- implementación

- importante

- in

- Intel

- propiedad

- intención

- interesante

- Intermedio

- introducir

- cuestiones

- IT

- SUS

- Notas clave

- Tipo

- Conocer

- idioma

- aprendido

- Legado

- Nivel

- como

- pequeño

- MIRADAS

- de

- máquina

- hecho

- para lograr

- max-ancho

- mencionado

- metodologías

- podría

- modelo

- modelos

- más,

- Natural

- Lenguaje natural

- ¿ Necesita ayuda

- Nuevo

- Next

- of

- on

- ONE

- Otro

- (PDF)

- Paso

- Platón

- Inteligencia de datos de Platón

- PlatónDatos

- puntos

- posible

- Publicación

- publicado

- prensa

- bastante

- primario

- Problema

- problemas

- Producción

- Programa

- Demostrar.

- proporciona un

- propósito

- pregunta

- Leer

- relativamente

- resultado

- segundos

- set

- tienes

- Signal

- sencillos

- sencillez

- simulación

- simulador

- desde

- página web

- So

- algo

- algo

- Pronto

- Aislamiento de Sonido

- soluciones y

- especificación

- estándar

- comienzo

- fundó

- sencillo

- tal

- RESUMEN

- sorpresa

- sorprendente

- ¡Prepárate!

- escuchar

- Tecnología

- test

- Pruebas

- esa

- El

- Estas

- cosa

- Ideas

- A través de esta formación, el personal docente y administrativo de escuelas y universidades estará preparado para manejar los recursos disponibles que derivan de la diversidad cultural de sus estudiantes. Además, un mejor y mayor entendimiento sobre estas diferencias y similitudes culturales permitirá alcanzar los objetivos de inclusión previstos.

- equipo

- a

- nivel superior

- tema

- truncamiento

- entender

- comprensión

- Uso

- utilizan el

- Valioso

- VC

- verificando

- Versus

- vía

- Ver ahora

- ver

- Camino..

- formas

- WELL

- ¿

- sean

- que

- seguirá

- mundo

- valor

- se

- escribir

- zephyrnet