Los sistemas de matrices múltiples se componen de varias matrices funcionales especializadas (o chiplets) que se ensamblan en el mismo paquete para crear el sistema completo. Los sistemas de matrices múltiples han surgido recientemente como una solución para superar la desaceleración de la ley de Moore al proporcionar un camino para escalar la funcionalidad en el chip empaquetado de una manera que sea fabricable con buen rendimiento.

Además, los sistemas de matrices múltiples permiten flexibilidad de SKU del producto en términos de escalamiento del rendimiento para satisfacer las necesidades de diferentes segmentos del mercado, optimización del nodo de proceso por función al mezclar y combinar varios nodos de proceso en el mismo producto, tiempo de comercialización más rápido y menor riesgo.

Para permitir una mayor densidad de enrutamiento entre matrices y admitir un mayor tráfico de ancho de banda entre matrices, la tecnología de paquetes ha evolucionado para crear paquetes nuevos y avanzados, basados en intercaladores de silicio (con TSV) o puentes de silicio y, más recientemente, capas de redistribución (RDL). , distribuciones en abanico y sustratos HD.

Un aspecto clave para el éxito de los sistemas de matrices múltiples es la capacidad de garantizar la capacidad de prueba del sistema en diferentes fases de fabricación y ensamblaje, así como garantizar un funcionamiento confiable en el campo. Al utilizar pasos de ensamblaje adicionales y tecnologías de empaquetamiento y golpes más complejas, los sistemas de matrices múltiples requieren procedimientos de prueba y confiabilidad que van más allá de lo que era lo último en diseños monolíticos.

Los troqueles desnudos y el paquete en sí deben probarse previamente para garantizar que se detecten todos los troqueles o paquetes defectuosos antes de ensamblarlos en un paquete. Si se detecta un troquel defectuoso sólo después del montaje, entonces se debe desechar todo el sistema de troqueles múltiples, con un grave impacto en el coste. El proceso de prueba de matrices desnudas se denomina prueba de matrices en buen estado (KGD).

El proceso de montaje en sí varía según la tecnología de embalaje seleccionada. Por ejemplo, las tecnologías de chip primero, donde los troqueles se colocan primero y la interconexión se construye encima de ellos, no permiten realizar pruebas de "paquetes en buen estado", lo que podría resultar en el desguace de troqueles buenos si la interconexión es defectuosa. Por otro lado, en las tecnologías de último chip, donde la interconexión se construye por separado y los troqueles se ensamblan encima, permiten realizar pruebas previas del paquete antes del ensamblaje, lo que reduce la probabilidad de que se desechen los troqueles buenos.

La solución de comprobabilidad del sistema de matrices múltiples se puede dividir en varios aspectos:

- Cobertura de prueba de bloques individuales dentro del troquel.

- Cobertura de prueba de los muñones individuales (muñones desnudos)

- Prueba del sistema ensamblado (con cobertura matriz a matriz)

- Acceso al tejido de prueba en troqueles desnudos.

- Acceso jerárquico al tejido de prueba después del montaje.

Este artículo describe los beneficios de una solución integral de capacidad de prueba que aprovecha UCIe IP para garantizar la confiabilidad del sistema de múltiples matrices.

DFT para la interfaz UCIe

Se logra una solución de alta cobertura de pruebas para la interfaz UCIe mediante la implementación de amplias funciones de capacidad de prueba en UCIe IP para eliminar matrices defectuosas en la fase de prueba de matrices desnudas. Algunas de las características incluyen:

- Cadenas de escaneo que cubren todos los circuitos digitales sintetizados.

- Funcionalidad BIST específica de bloque dedicado

- Funcionalidad de autoprueba incorporada (BIST) de bucle invertido que cubre la cadena de señal completa hasta el pin IO

- Secuencia binaria pseudoaleatoria programable (PRBS) y generadores y verificadores de patrones de prueba definidos por el usuario

- Inyección de errores para eliminar pases falsos.

Además, la funcionalidad para ampliar la cobertura al enlace entre matrices, después del ensamblaje del paquete, puede ayudar a lograr un alto nivel de cobertura de prueba, que incluye:

- Funcionalidad de bucle invertido BIST del lado lejano (die-to-die)

- Enlace entre troqueles BIST

- Margen ocular 2D para analizar marginalidades

- Funcionalidad de prueba y reparación por carril

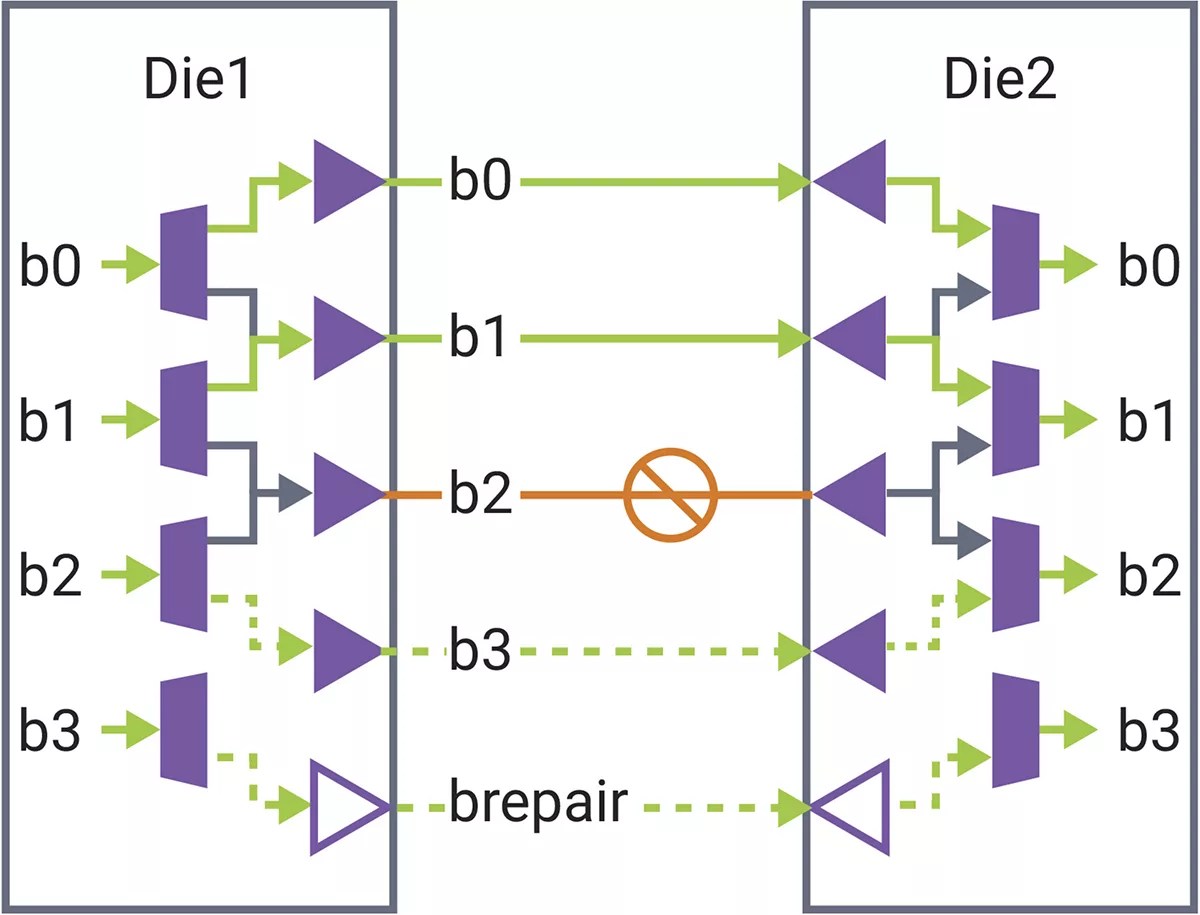

Prueba y reparación UCIe

Los paquetes avanzados permiten enrutamiento de alta densidad con micro-bumping de paso fino y enrutamiento en intercaladores de silicio o RDL. Durante el proceso de ensamblaje, es posible que algunas conexiones de microgolpes no estén bien formadas y se rompan. UCIe ofrece la posibilidad de probar y reparar estas conexiones después del ensamblaje de una manera que recupere la posible pérdida de rendimiento.

La prueba y reparación de UCIe se ejecuta durante la prueba de producción y en la inicialización del enlace. En la fase de prueba se comprueba cada eslabón individual en busca de defectos a baja velocidad. Los enlaces defectuosos se reparan redirigiendo los datos a enlaces de repuesto predefinidos por el estándar UCIe.

Las configuraciones UCIe destinadas a paquetes avanzados incluyen hasta 8 pines de repuesto por dirección (TX y RX) para permitir la reparación de todos los enlaces funcionales:

- Cuatro pines de repuesto para reparación de pines de datos, 2 pines para cada grupo de 32 pines de datos

- Un pasador de repuesto para reparación de relojes y pasadores de seguimiento.

- Tres pines de repuesto, cada uno para reparación de pin válido, pin de datos de banda lateral y pin de datos de reloj

La ejecución de prueba y reparación ocurre cuando no hay tráfico válido en el enlace de matriz a matriz. Una vez completada la reparación y inicializado el enlace, se supone que está en buen estado y que el tráfico puede circular sin problemas. La configuración PHY resultante, denominada firma de reparación PHY, se almacena en registros internos en ambos extremos del enlace.

La degradación, debido al envejecimiento u otros, de las características de microgolpes durante la operación puede afectar el rendimiento del enlace. Esto se detectará a nivel de protocolo mediante un aumento en la tasa de errores de bits (BER) o, peor aún, mediante la pérdida de datos. En ese caso, se espera que se interrumpa el enlace y se realice un nuevo paso de prueba y reparación.

Sin embargo, algunas aplicaciones tienen requisitos estrictos en términos de continuidad del tráfico en el enlace de matriz a matriz: no pueden tolerar la interrupción del tráfico durante la operación. Para estos casos, una solución de capacidad de prueba agrega monitores de integridad de señal (SIM) a cada pin del receptor UCIe.

Fig. 1: Reparación de eslabones utilizando eslabones de repuesto integrados.

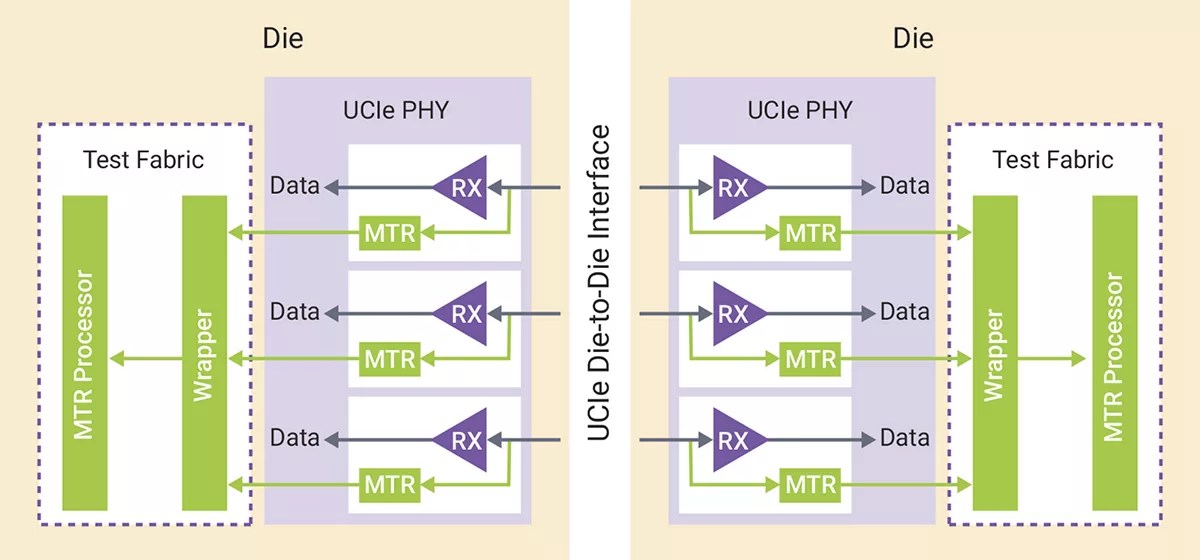

Monitores de integridad de señal

Los monitores SIM son pequeños bloques integrados en el receptor. Detectan constantemente la señal en el pin del receptor, durante el funcionamiento normal, para identificar variaciones en las características de la señal que pueden afectar el rendimiento del enlace o indicar que el enlace ya no está en buen estado y puede romperse en un futuro cercano.

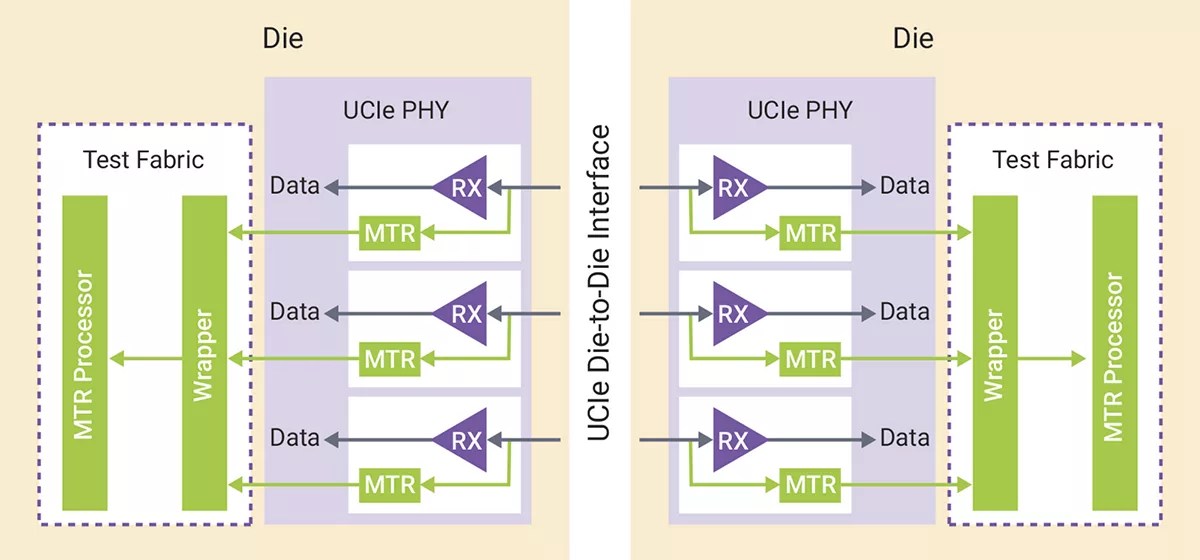

Los datos recopilados por los sensores individuales se recopilan en un controlador de Monitoreo, Prueba y Reparación (MTR), fuera de la interfaz, para su posterior procesamiento. Agregar los datos de múltiples enlaces UCIe puede proporcionar información instantánea sobre el estado del sistema de múltiples matrices y permitir el mantenimiento predictivo de los enlaces.

Si se prevé que un enlace específico esté en riesgo de funcionar mal a través de este procedimiento, se puede desactivar y redirigir los datos a uno de los enlaces de repuesto, aprovechando el mecanismo de reparación UCIe PHY, incluso sin interrupción del tráfico.

Fig. 2: Solución de monitoreo de salud para enlaces UCIe.

Acelerar el tiempo de despertar

Si bien se supone que el patrón de tráfico para la mayoría de los casos de uso de interfaz de matriz a matriz, por ejemplo en la división o escalado de servidores, es estable durante la operación, en algunos casos de uso el tráfico puede exhibir un comportamiento en ráfagas. En tales casos, es deseable poner la interfaz en un modo de bajo consumo para ahorrar energía mientras no hay tráfico. La reinicialización del enlace se puede acelerar evitando el proceso de prueba y reparación y confiando en la firma de reparación de UCIe PHY que se creó durante la inicialización de PHY anterior.

Este concepto se puede ampliar aún más a situaciones en las que el dado está completamente apagado. En estos casos, la firma de reparación de PHY se recupera de la PHY y se almacena en una memoria permanente integrada (eFuse o flash). La memoria posiblemente podría almacenar múltiples firmas, cubriendo diferentes casos o condiciones de uso, lo que permitiría una flexibilidad adicional para el usuario.

Acelerando las pruebas de troqueles con UCIe

El tiempo de prueba es un bien caro. Es posible acelerar el tiempo de prueba dividiendo la estrategia de prueba jerárquicamente para ejecutar pruebas de diferentes troqueles en paralelo. La jerarquía se puede ampliar a través de múltiples matrices en un sistema de múltiples matrices conectando jerárquicamente la infraestructura de prueba de las dos matrices. Este enfoque permite el acceso a todos los troqueles del sistema de troqueles múltiples desde una única interfaz de prueba JTAG (o similar) en el troquel principal.

A menudo, la limitación del tiempo de prueba es el tiempo para cargar o leer los vectores de prueba en los troqueles. Las interfaces JTAG pueden convertirse en un cuello de botella en la velocidad. Para superar esta limitación, los diseñadores pueden utilizar interfaces de alta velocidad existentes, como PCI Express (PCIe) o USB, etc., como interfaces para el equipo de prueba. Los vectores y comandos de prueba se empaquetan para esa interfaz y se despaquetean en el troquel durante la fase de prueba de producción.

Muchos troqueles no tienen una interfaz de alta velocidad; sin embargo, la interfaz de troquel a troquel UCIe se puede utilizar, durante la prueba, para transportar grandes vectores de prueba y comandos entre troqueles a alta velocidad. La interfaz de troquel a troquel UCI amplía el acceso DFT de alta velocidad a todo el sistema de troqueles múltiples sin aumentar el número de pines, lo cual es particularmente importante para IO y troqueles de área limitada.

Resumen

Además de la interfaz matriz a matriz UCIe, el denominador común que permite todas estas funciones de mejora de la confiabilidad y las pruebas es una estructura de prueba, reparación y monitoreo que puede conectar todos los bloques internos. El tejido de prueba, reparación y monitoreo abarca los diversos troqueles del sistema de múltiples troqueles, proporcionando una infraestructura jerárquica estructurada que logra las siguientes funciones importantes:

- Gestiona las pruebas de los troqueles individuales en el sistema de troqueles múltiples.

- Optimiza la programación de pruebas para reducir el tiempo de prueba.

- Admite el acceso a pruebas de alta velocidad a través de las matrices, a través de la interfaz UCIe

- Recopila información de las interfaces de monitoreo de salud integradas en la interfaz UCIe y permite un procesamiento adicional a nivel del sistema.

- Gestiona el almacenamiento de la firma de reparación PHY en una memoria no volátil.

- Y más...

Synopsys proporciona una solución de sistema de múltiples matrices integral y escalable, que incluye EDA e IP, para una integración heterogénea rápida. Para una conectividad integral segura y confiable, Synopsys ofrece una solución completa de controlador UCIe, PHY y verificación IP. Como parte de la familia de pruebas y SLM de Synopsys, está disponible una solución completa de monitoreo, prueba y reparación (MTR) de UCIe junto con la solución STAR Hierarchical System (SHS). La solución MTR incluye un monitor de integridad de la señal para medir la calidad de la señal en los carriles UCIe, BIST para autoprueba y lógica de reparación para la asignación de carriles redundantes, mientras que la solución SHS sirve como tejido de conectividad compatible con los estándares industriales IEEE 1687, IEEE 1149.1 e IEEE 1838. interfaces. Esta solución completa permite un monitoreo eficiente y rentable del estado de UCIe durante todas las fases del ciclo de vida del silicio, lo cual es fundamental para el funcionamiento confiable de los sistemas de matrices múltiples.

Fuentes:

- Distribución de relaciones públicas y contenido potenciado por SEO. Consiga amplificado hoy.

- PlatoAiStream. Inteligencia de datos Web3. Conocimiento amplificado. Accede Aquí.

- Acuñando el futuro con Adryenn Ashley. Accede Aquí.

- Compra y Vende Acciones en Empresas PRE-IPO con PREIPO®. Accede Aquí.

- Fuente: https://semiengineering.com/from-known-good-die-to-known-good-system-with-ucie-ip/

- :posee

- :es

- :no

- :dónde

- $ UP

- 1

- 8

- a

- capacidad

- acelerar

- acelerado

- de la máquina

- Lograr

- alcanzado

- Logra

- a través de

- adición

- Adicionales

- Añade

- avanzado

- Después

- Aging

- Todos

- asignación

- permitir

- permite

- a lo largo de

- an

- analizar

- y

- aplicaciones

- enfoque

- somos

- artículo

- AS

- aspecto

- aspectos

- ensamblada

- Asamblea

- ficticio

- At

- Hoy Disponibles

- evitar

- Ancho de banda

- basado

- BE

- a las que has recomendado

- antes

- "Ser"

- beneficios

- entre

- Más allá de

- Bloquear

- Bloques

- ambas

- Descanso

- puentes

- llevar

- construido

- incorporado

- by

- , que son

- PUEDEN

- no puede

- case

- cases

- cadena

- cadenas

- características

- comprobado

- chip

- Reloj

- Relojes

- mercancía

- Algunos

- completar

- completamente

- integraciones

- exhaustivo

- concepto

- condiciones

- Configuración

- CONTACTO

- Conectándote

- Conexiones

- Conectividad

- constantemente

- controlador

- Cost

- rentable

- podría

- cobertura

- cubierta

- Para crear

- creado

- crítico

- datos

- se define

- densidad

- diseñadores

- diseños

- detectado

- El

- una experiencia diferente

- digital

- dirección

- discapacitados

- dividido

- do

- DE INSCRIPCIÓN

- dos

- durante

- cada una

- eficiente

- eliminarlos

- integrado

- surgido

- habilitar

- permite

- permitiendo

- termina

- Estrategias orientadas

- garantizar

- asegurando que

- equipo

- etc.

- Éter (ETH)

- Incluso

- evolucionado

- ejemplo

- ejecución

- exhibir

- existente

- esperado

- costoso

- expreso

- ampliar

- en los detalles

- extra

- ojos

- material

- false

- familia

- RÁPIDO

- más rápida

- defectuoso

- Caracteristicas

- campo

- en fin

- Nombre

- Flash

- Flexibilidad

- siguiendo

- formado

- en

- función

- funcional

- a la fatiga

- funciones

- promover

- futuras

- reunido

- generadores

- Go

- candidato

- Grupo procesos

- mano

- Tienen

- Salud

- saludable

- ayuda

- jerarquía

- Alta

- más alto

- Sin embargo

- HTTPS

- Identifique

- IEEE

- if

- Impacto

- implementación

- importante

- in

- incluir

- incluye

- Incluye

- aumente

- creciente

- indicar

- INSTRUMENTO individual

- energético

- información

- EN LA MINA

- Insights

- instantáneo

- integración

- integridad

- Interfaz

- las interfaces

- interno

- interrumpido

- dentro

- IP

- IT

- sí mismo

- Clave

- conocido

- Callejuela

- large

- de derecho criminal

- ponedoras

- Nivel

- apalancamientos

- aprovechando

- ciclo de vida

- la limitación

- LINK

- enlaces

- carga

- lógica

- por más tiempo

- de

- perdido

- Baja

- hecho

- Inicio

- un mejor mantenimiento.

- Mercado

- Match

- pareo

- max-ancho

- Puede..

- medición

- mecanismo

- Salud Cerebral

- Moda

- Monitorear

- monitoreo

- monitores

- Monolítico

- más,

- MEJOR DE TU

- MTR

- múltiples

- debe

- Cerca

- Nuevo

- no

- nodo

- nodos

- normal

- número

- of

- Ofertas

- on

- ONE

- , solamente

- Inteligente

- optimización

- or

- Otro

- salir

- afuera

- Superar

- paquete

- empaquetado

- paquetes

- embalaje

- Paralelo

- parte

- particularmente

- pasado

- camino

- Patrón de Costura

- .

- actuación

- permanente

- fase

- patas

- Paso

- Platón

- Inteligencia de datos de Platón

- PlatónDatos

- posible

- posiblemente

- posible

- la posibilidad

- industria

- alimentado

- previsto

- anterior

- Anterior

- probabilidades

- problemas

- procedimientos

- tratamiento

- Producto

- Producción

- protocolo

- proporcionar

- proporciona un

- proporcionando

- calidad

- Rate

- Leer

- recientemente

- Recupera

- reducir

- la reducción de

- registros

- fiabilidad

- confianza

- reparación

- exigir

- Requisitos

- resultante

- Riesgo

- enrutamiento

- Ejecutar

- RX

- mismo

- Guardar

- escalable

- la ampliación

- programación

- seguro

- segmentos

- seleccionado

- sensor

- Secuencia

- grave

- sirve

- Varios

- tienes

- lado

- Signal

- Firmas

- Silicio

- Tarjeta SIM

- similares

- soltero

- circunstancias

- lento

- La desaceleración

- chica

- a medida

- algo

- se extiende

- especializado

- soluciones y

- velocidad

- estable

- estándar

- Estrella

- el estado de la técnica

- paso

- pasos

- STORAGE

- tienda

- almacenados

- Estrategia

- estructurado

- comercial

- tal

- SOPORTE

- Apoyar

- te

- Todas las funciones a su disposición

- orientación

- Tecnologías

- Tecnología

- términos

- test

- Pruebas

- pruebas

- esa

- El

- Les

- luego

- Ahí.

- Estas

- ellos

- así

- A través de esta formación, el personal docente y administrativo de escuelas y universidades estará preparado para manejar los recursos disponibles que derivan de la diversidad cultural de sus estudiantes. Además, un mejor y mayor entendimiento sobre estas diferencias y similitudes culturales permitirá alcanzar los objetivos de inclusión previstos.

- equipo

- a

- parte superior

- seguir

- tráfico

- transportando

- dos

- TX

- usb

- utilizan el

- usado

- Usuario

- usando

- diversos

- Verificación

- vía

- fue

- Camino..

- webp

- WELL

- ¿

- cuando

- que

- mientras

- seguirá

- dentro de

- sin

- Peor

- Rendimiento

- zephyrnet