Los chiplets han simplificado un área del diseño pero han abierto la caja de Pandora en otro frente. La complejidad de la simulación de cada chiplet es menor, pero ahora la interconexión de chiplet a chiplet se ha vuelto compleja. La gente está experimentando con diferentes protocolos de interconexión, variaciones de UCIe, modificando la configuración de UCIe, las velocidades de interfaz, la cantidad de capas físicas, etc. Ahora agregue a la mezcla estándares heredados como AXI, nuevos protocolos como PICe6.0 y coherencia de caché.

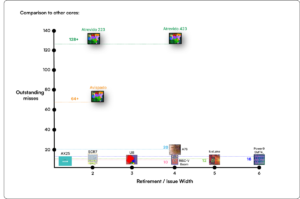

En definitiva, esto crea un conjunto de experimentos completamente nuevo. Uno para el cual la emulación tradicional y el modelado RTL no funcionarán. Primero debe dedicar un esfuerzo a la compensación de la arquitectura, no solo a la selección de componentes. Esto significará que tendrá que realizar análisis de tráfico, partición de aplicaciones, dimensionamiento del sistema e impacto de diferentes tipos de capa física. Además, dependiendo de la aplicación, el punto de referencia será muy diferente.

La especificación UCIe es nueva y no existen puntos de referencia claros. Además, la especificación UCIe solo proporciona orientación sobre latencia y potencia. Ambos son requisitos estrictos. Esto significa que es evitable un estudio del área de rendimiento de energía. Como tiene una conversión de protocolo a protocolo, como PCIe 6.0 a UCIe a AXI, la configuración del modelado es compleja.

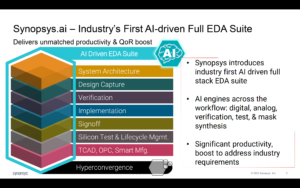

Una solución es analizar el modelado de sistemas utilizando Simulación visual Desde Mirabilis Diseño. Recientemente lanzaron un modelo IP a nivel de sistema UCIe y demostrarán una serie de casos de uso de la interconexión en el Cumbre de chiplet. Para guiar a los diseñadores, han publicado una guía con muchos casos de uso, resultados esperados de rendimiento energético y opciones de optimización. Tienen una presentación en papel y un stand en la Cumbre. ¡Espero verte allí!

Además, aquí está el enlace a un artículo que la gente puede obtener: Modelado del rendimiento de un sistema informático heterogéneo basado en la arquitectura de interconexión UCIe

Abstracto:

Los complejos diseños de chips actuales en los nodos de vanguardia generalmente constan de múltiples matrices (o chiplets). El enfoque permite matrices de diferentes fabricantes o procesos, así como IP reutilizables. Los diseñadores necesitan un modelo a nivel de sistema para evaluar diferentes implementaciones de situaciones tan complejas.

Un sistema de ejemplo consta de un chiplet de E/S, un chiplet de núcleo de bajo consumo, un chiplet de núcleo de alto rendimiento, un chiplet de audio y vídeo y un chiplet analógico, interconectados mediante el estándar Universal Chiplet Interconnect Express (UCIe).

Nuestro equipo consideró varios escenarios y configuraciones, incluidos paquetes avanzados y estándar, diversos perfiles de tráfico y recursos, y un temporizador para ampliar el alcance y evaluar eventos en el tiempo de espera. Identificar las fortalezas y debilidades de la interconexión UCIe para aplicaciones de misión nos ayudó a obtener la configuración óptima para que cada subsistema cumpla con los requisitos funcionales, de potencia y de rendimiento.

Acerca de Mirabilis Design Inc.

Mirabilis Design es una empresa de software de Silicon Valley que ofrece software y soluciones de capacitación para identificar y eliminar riesgos en las especificaciones del producto, prediciendo con precisión los recursos humanos y de tiempo necesarios para desarrollar el producto y mejorando la comunicación entre diversos ingenieros.

equipos.

VisualSim Architect combina propiedad intelectual, modelado a nivel de sistema, simulación, análisis del entorno y plantillas de aplicaciones para mejorar significativamente la construcción de modelos, la simulación, el análisis y la verificación RTL. El entorno permite a los diseñadores converger rápidamente hacia un diseño que cumpla con un conjunto diverso de requisitos interdependientes de tiempo y energía. Se utiliza muy temprano en el proceso de diseño en paralelo con (y como ayuda para) la especificación escrita y antes de una implementación (por ejemplo, RTL, código de software o esquema) del producto.

Lea también

Asignación de SysML a la arquitectura de hardware

Cursos de diseño basado en modelos para estudiantes

Comparte esta publicación a través de:

- Distribución de relaciones públicas y contenido potenciado por SEO. Consiga amplificado hoy.

- PlatoData.Network Vertical Generativo Ai. Empodérate. Accede Aquí.

- PlatoAiStream. Inteligencia Web3. Conocimiento amplificado. Accede Aquí.

- PlatoESG. Carbón, tecnología limpia, Energía, Ambiente, Solar, Gestión de residuos. Accede Aquí.

- PlatoSalud. Inteligencia en Biotecnología y Ensayos Clínicos. Accede Aquí.

- Fuente: https://semiwiki.com/ip/mirabilis-design-ip/341339-chiplets-open-pandoras-box/

- :posee

- :es

- :no

- a

- preciso

- precisamente

- Lograr

- add

- avanzado

- Ayudar

- permite

- a lo largo de

- también

- an

- análisis

- y

- Otra

- Aplicación

- aplicaciones

- enfoque

- arquitectura

- somos

- Reservada

- AS

- At

- basado

- BE

- a las que has recomendado

- antes

- los puntos de referencia

- entre

- ambas

- Box

- pero

- cache

- PUEDEN

- Puede conseguir

- cases

- chip

- limpiar

- código

- combina

- Comunicación

- compañía

- completamente

- integraciones

- complejidad

- componentes

- informática

- Conducir

- Configuración

- considerado

- consiste

- construcción

- converger

- Conversión

- Core

- cursos

- crea

- vas demostrando

- Dependiente

- Diseño

- proceso de diseño

- diseñadores

- diseños

- desarrollar

- una experiencia diferente

- diverso

- durante

- cada una

- Temprano en la

- esfuerzo

- eliminarlos

- emulación

- permite

- Entorno

- evaluar

- Eventos

- ejemplo

- esperado

- experimentando

- experimentos

- expreso

- ampliar

- Nombre

- Desde

- frontal o trasero

- funcional

- en general

- obtener

- guía

- guía

- Materiales

- Tienen

- ayudado

- esta página

- Alto rendimiento

- esperanza

- Cómo

- Como Hacer

- HTTPS

- humana

- i

- Identifique

- identificar

- Impacto

- implementación

- implementaciones

- mejorar

- in

- Incluye

- propiedad

- la propiedad intelectual

- interconectado

- Interfaz

- IP

- IT

- jpg

- solo

- Estado latente

- lanzado

- .

- ponedoras

- Legado

- Nivel

- como

- LINK

- Mira

- un montón

- Baja

- inferior

- Fabricantes

- max-ancho

- personalizado

- significa

- multiplataforma

- Conoce a

- se une a la

- misión

- mezcla

- modelo

- modelado

- modelización

- múltiples

- ¿ Necesita ayuda

- Nuevo

- no

- nodos

- ahora

- número

- obtener

- of

- on

- ONE

- , solamente

- habiertos

- abierto

- óptimo

- optimización

- Opciones

- or

- paquetes

- Papel

- Paralelo

- actuación

- los libros físicos

- Platón

- Inteligencia de datos de Platón

- PlatónDatos

- Publicación

- industria

- predecir

- presentation

- en costes

- Producto

- Perfiles

- perfecta

- protocolos

- proporciona un

- proporcionando

- publicado

- rápidamente

- en comunicarse

- Leer

- recientemente

- Requisitos

- Requisitos

- Recursos

- Resultados

- reutilizables

- Riesgo

- escenarios

- ver

- seleccionar

- set

- ajustes

- Configure

- Varios

- significativamente

- Silicio

- Silicon Valley

- simplificado

- simulación

- circunstancias

- So

- Software

- a medida

- Soluciones

- especificación

- velocidades

- pasar

- estándar

- estándares de salud

- fortalezas

- riguroso

- ESTUDIO

- tal

- Summit

- te

- equipo

- plantillas

- esa

- La

- Ahí.

- ellos

- así

- equipo

- a

- tradicional

- tráfico

- Formación

- tipos

- Universal

- us

- utilizan el

- usado

- usando

- Valle

- variaciones

- Verificación

- muy

- vía

- debilidades

- WELL

- que

- seguirá

- Actividades:

- escrito

- Usted

- zephyrnet