En proyectos de diseño de chips grandes, el esfuerzo de verificación de la lógica puede ser mayor que el esfuerzo de diseño, ocupando hasta el 70 % del tiempo del proyecto según los datos del 2022 Grupo de Investigación Wilson recomendaciones. Lamentablemente, la tasa de éxito del primer silicio ha bajado del 31 % a solo el 24 % en los últimos 8 años, lo que provocó otro giro para corregir las fallas, costó a las empresas el tiempo perdido en el mercado y, sin duda, perjudicó sus planes de ingresos. Una mejor verificación sin duda mejoraría el éxito del primer silicio, pero es más fácil decirlo que hacerlo.

Algunas otras cifras aleccionadoras del estudio de Wilson Research Group:

- ASIC: 24 % de éxito a la primera, 36 % de finalización a tiempo

- FPGA: el 16 % logra cero escapes de errores, el 30 % termina a tiempo

La verificación del diseño tiene muchas tareas difíciles: depuración, creación de pruebas y luego ejecución de motores, desarrollo de banco de pruebas y planificación de pruebas. Idealmente, su equipo quiere minimizar los tiempos de respuesta, llegar al cierre de la verificación con la menor cantidad de personas y recursos informáticos, cumplir con el cumplimiento de la seguridad y saber cuándo la calidad del diseño es lo suficientemente alta como para dejar de verificar, mientras cumple con el cronograma del proyecto.

Recientemente recibí una actualización del experto en verificación de diseño Darron May en Siemens EDA para escuchar algo que se acaba de anunciar, llamado CI de verificación de Questa. Su enfoque tiene que ver con la verificación basada en datos formada en torno al uso de la trazabilidad, la colaboración y el análisis impulsado por AI/ML. Los análisis tradicionales proporcionaron una productividad y una perspectiva limitadas con solo describir y diagnosticar el comportamiento lógico, mientras que los análisis basados en big data que utilizan IA/ML ofrecen acciones predictivas y prescriptivas para la verificación. Los equipos de software y hardware se están volviendo más productivos al colaborar mediante el uso de CI (Integración continua), Agil Modelo de , ALM (Administración del ciclo de vida de la aplicación), diseño basado en la nube y aplicación de técnicas AI/ML. Las industrias críticas para la seguridad necesitan trazabilidad entre los requisitos, la implementación y la verificación, tal como se define en los estándares de la industria como ISO 26262 y DO-254.

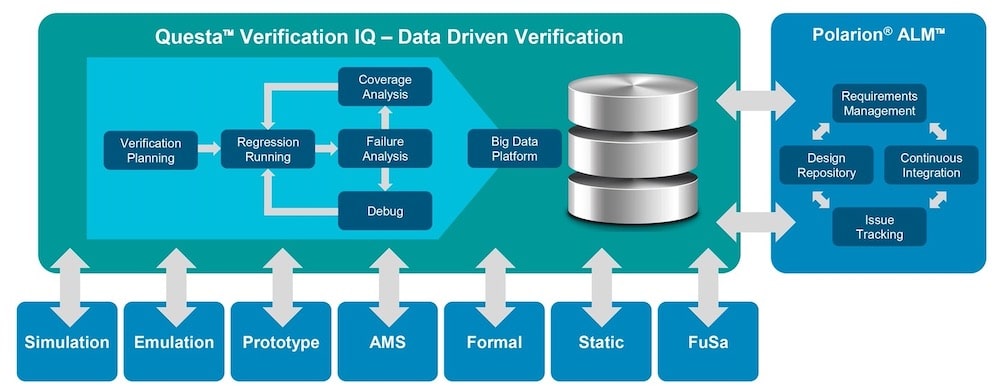

Este es el panorama general de cómo Quest Verification IQ conecta todos los datos de varios motores de verificación en un flujo basado en datos, junto con una herramienta ALM.

Los datos de cobertura se obtienen de la simulación lógica (Este), emulación y creación de prototipos (Veloce), AM (Sympony), Formal (Un giro), Estática y FuSa. La función ML analiza todos estos datos para predecir patrones y revelar cualquier agujero, señalar las causas raíz y luego prescribir acciones para mejorar la cobertura. El ALM que se muestra es polarión de Siemens, aunque podría usar otro ALM, al igual que puede usar sus motores de verificación favoritos.

Questa Verification IQ es un marco basado en navegador que incluye una guía de procesos para que pueda crear un flujo crítico de seguridad utilizando la gestión del ciclo de vida para planificar y realizar un seguimiento de todos los requisitos. El navegador de regresión le permite a su equipo crear y ejecutar pruebas, monitorear los resultados y tener un historial de verificación completo. Con el analizador de cobertura, sabe qué tan completa es su cobertura para código, bloques funcionales y planes de prueba. Finalmente, el análisis de datos presentado le brinda una plataforma métrica, utilizando paneles de proyectos y proporcionando análisis cruzados.

El marco basado en la web se adapta a cualquier tamaño de proyecto de electrónica, y no tendrá que instalar ningún software ni preocuparse por mantener su sistema operativo actualizado. También admite configuraciones de nube pública, privada o híbrida. Con la aplicación de AI/ML, el proceso de cierre de verificación se acelera, mientras que el esfuerzo de depuración se acelera a medida que el análisis de causa raíz ayuda a identificar dónde mejorar.

Le hice a Darron May algunas preguntas aclaratorias.

P: ¿Puedo combinar Questa Verification IQ con cualquier herramienta de proveedor de EDA y ALM?

A: Questa Verification IQ admite herramientas y motores ALM a través de un enfoque basado en estándares. Se conecta con las herramientas de ALM mediante Open Services for Lifecycle Collaboration (OSLC), por lo que se puede utilizar cualquier herramienta compatible con el estándar, como Doors next o Siemens Polarion y Teamcenter. Cualquier motor puede ser lanzado por Questa Verification IQ y nuevamente tenemos soporte para cobertura a través del Estándar de Interoperabilidad de Cobertura Unificada (UCIS).

P: ¿Cómo se compara este enfoque con Synopsys DesignDash?

A: Synopsys DesignDash se centra en ML para datos de diseño, mientras que Questa Verification IQ se centra en la verificación basada en datos mediante análisis, incluido ML, para acelerar el cierre de la verificación, reducir los tiempos de respuesta y proporcionar la máxima eficiencia del proceso. Questa Verification IQ proporciona las aplicaciones necesarias para la gestión de verificación colaborativa basada en equipos en un marco basado en navegador con acceso centralizado a los datos.

P: ¿Cómo se compara este enfoque con Cadence Verisium?

A: Cadence Verisium se enfoca solo en la verificación asistida por ML. En comparación, Siemens Questa Verification IQ proporciona una solución completa de verificación basada en datos con tecnología de análisis, colaboración y trazabilidad. Verification Management se proporciona en una herramienta basada en navegador con aplicaciones creadas en torno a Collaboration. Coverage Analyzer trae la primera herramienta de cierre de cobertura colaborativa de la industria que utiliza navegación analítica asistida por ML. Question Verification IQ interactúa con Siemens Polarion mediante OSLC y proporciona una trazabilidad de subprocesos digital estricta con la gestión del ciclo de vida de la aplicación sin cambios en el contexto de la interfaz de usuario, lo que lleva el poder de ALM a la verificación de hardware.

Resumen

Siempre estoy impresionado con las nuevas herramientas EDA que facilitan una tarea compleja al trabajar de manera más inteligente, sin requerir que los ingenieros dediquen más horas de esfuerzo manual. Con los primeros respaldos de Questa Verification IQ de compañías familiares como Arm y Nordic Semiconductor, parece que Siemens EDA ha agregado algo convincente para que los equipos de verificación consideren mirar.

Blogs relacionados

Comparte esta publicación a través de:

- Distribución de relaciones públicas y contenido potenciado por SEO. Consiga amplificado hoy.

- Platoblockchain. Inteligencia del Metaverso Web3. Conocimiento amplificado. Accede Aquí.

- Fuente: https://semiwiki.com/eda/324031-achieving-faster-design-verification-closure/

- a

- Nuestra Empresa

- acelerar

- de la máquina

- Acceso a los datos

- Lograr

- el logro de

- la columna Acción

- acciones

- adicional

- AI / ML

- Todos

- Aunque

- hacerlo

- análisis

- Pruebas analíticas

- Analytics

- análisis

- y

- anunció

- Otra

- Aplicación

- aplicaciones

- aplicada

- La aplicación de

- enfoque

- ARM

- en torno a

- Automatización

- basado

- cada vez

- "Ser"

- mejores

- entre

- Big

- En el gran esquema del universo

- Bloques

- Trayendo

- Trae

- Error

- build

- construido

- Cadencia

- , que son

- Causar

- causas

- causando

- centralizado

- ciertamente

- el cambio

- chip

- cierre

- Soluciones

- código

- colaborar

- colaboración

- colaboración

- Empresas

- comparar

- comparación

- irresistible

- completar

- integraciones

- compliance

- Calcular

- preocupado

- conecta

- Considerar

- contexto

- continuo

- podría

- cobertura

- Para crear

- Creamos

- crítico

- Cruz

- datos

- Data Analytics

- basada en datos

- Diseño

- Desarrollo

- difícil

- digital

- puertas

- impulsados

- Temprano en la

- más fácil

- eficiencia

- esfuerzo

- Electrónica

- permite

- Avales

- Motor

- certificados

- motores

- suficientes

- ejecutar

- experto

- familiar

- más rápida

- Favoritos

- Feature

- pocos

- Finalmente

- Nombre

- primer vez

- defectos

- de tus señales

- centrado

- se centra

- formal

- formado

- Marco conceptual

- en

- funcional

- Grupo procesos

- guía

- Materiales

- ayuda

- Alta

- historia

- Agujeros

- HORAS

- Cómo

- HTTPS

- Híbrido

- nube híbrida

- implementación

- impresionado

- mejorar

- in

- incluye

- Incluye

- industrias

- energético

- estándares de la industria

- de la industria

- penetración

- instalar

- integración

- las interfaces

- Interoperabilidad

- ISO

- IT

- acuerdo

- Saber

- mayores

- lanzado

- Limitada

- mirando

- MIRADAS

- para lograr

- Management

- manual

- muchos

- Mercado

- Match

- max-ancho

- máximas

- Conoce a

- reunión

- métodos

- métrico

- ML

- Monitorear

- más,

- Navegación

- Navigator

- ¿ Necesita ayuda

- Nuevo

- Next

- números

- LANZAMIENTO

- habiertos

- solicite

- OS

- Otro

- pasado

- .

- Personas

- por ciento

- imagen

- plan

- planificar

- jubilación

- plataforma

- Platón

- Inteligencia de datos de Platón

- PlatónDatos

- punto

- Publicación

- industria

- alimentado

- predecir

- prescribir

- presentó

- privada

- productivo

- productividad

- proyecto

- proyecta

- prototipado

- proporcionar

- previsto

- proporciona un

- proporcionando

- público

- poner

- calidad

- búsqueda

- pregunta

- Preguntas

- Rate

- en comunicarse

- recientemente

- reducir

- regresión

- Requisitos

- la investigación

- grupo de investigacion

- Recursos

- Resultados

- género

- ingresos

- raíz

- correr

- Safety

- Said

- escamas

- programa

- semiconductor

- Servicios

- mostrado

- Siemens

- Silicio

- simulación

- Tamaño

- más inteligente

- So

- Software

- a medida

- algo

- Girar

- estándar

- estándares de salud

- Detener

- ESTUDIO

- comercial

- SOPORTE

- Apoyar

- soportes

- toma

- Tarea

- equipo

- equipos

- técnicas

- test

- pruebas

- El

- su

- A través de esta formación, el personal docente y administrativo de escuelas y universidades estará preparado para manejar los recursos disponibles que derivan de la diversidad cultural de sus estudiantes. Además, un mejor y mayor entendimiento sobre estas diferencias y similitudes culturales permitirá alcanzar los objetivos de inclusión previstos.

- equipo

- veces

- a

- juntos

- del IRS

- Trazabilidad

- seguir

- tradicional

- ui

- unificado

- Actualizar

- actualizado

- utilizan el

- diversos

- vendedor

- Verificación

- verificando

- vía

- Basado en la Web

- mientras

- Wikipedia

- Wilson

- trabajando

- se

- años

- tú

- zephyrnet

- cero