Από το ντεμπούτο του στη δεκαετία του 1980 με κοινόχρηστα LAN 10 Mbps μέσω ομοαξονικών καλωδίων, το Ethernet έχει δει σταθερές εξελίξεις, τώρα με τη δυνατότητα να υποστηρίζει ταχύτητες έως και 1.6 Tbps. Αυτή η εξέλιξη επέτρεψε στο Ethernet να εξυπηρετεί ένα ευρύτερο φάσμα εφαρμογών, όπως ζωντανή ροή, δίκτυα πρόσβασης ραδιοφώνου και βιομηχανικό έλεγχο, τονίζοντας τη σημασία της αξιόπιστης μεταφοράς πακέτων και της ποιότητας της υπηρεσίας. Με το τρέχον εύρος ζώνης του Διαδικτύου να κυμαίνεται στα ~500 Tbps, υπάρχει μια αυξανόμενη ζήτηση για βελτιωμένο χειρισμό κίνησης εντός του κέντρου δεδομένων back-end. Παρόλο που μεμονωμένοι διακομιστές δεν λειτουργούν ακόμη σε επίπεδα Terabit-per-second, η συνολική κίνηση των κέντρων δεδομένων πλησιάζει σε αυτήν την κλίμακα, ωθώντας την ομάδα 802.3dj της IEEE να αναλάβει προσπάθειες τυποποίησης και απαιτώντας ισχυρούς ελεγκτές Ethernet και SerDes για τη διαχείριση της διευρυνόμενης ροής δεδομένων. Μέσα σε αυτό το σκηνικό των κλιμακούμενων απαιτήσεων, η επικοινωνία μεταξύ των επεξεργαστών ωθεί ήδη σε αυτές τις ταχύτητες.

Η επικοινωνία μεταξύ των επεξεργαστών είναι αιχμή του δόρατος στην ανάγκη για ρυθμούς 1.6Τ με ελάχιστο λανθάνοντα χρόνο. Ενώ οι μεμονωμένες συσκευές περιορίζονται από τις εγγενείς ικανότητες επεξεργασίας και το μέγεθος των τσιπ, ο συνδυασμός τσιπ μπορεί να επεκτείνει σημαντικά αυτές τις ικανότητες. Η πρώτη γενιά εφαρμογών αναμένεται να ακολουθηθεί από ενδοκεντρικές συνδέσεις μεταγωγής σε μεταγωγέα, επιτρέποντας τη συγκέντρωση επεξεργαστών και μνήμης υψηλής απόδοσης, ενισχύοντας την επεκτασιμότητα και την αποτελεσματικότητα στο cloud computing.

Πρωτοβουλία 802.3dj της IEEE: Προώθηση προτύπων Ethernet για διαλειτουργικότητα 1.6 Tbps

Η συμμόρφωση με τις εξελισσόμενες προσπάθειες τυποποίησης είναι ζωτικής σημασίας για την απρόσκοπτη διαλειτουργικότητα του οικοσυστήματος. Η ομάδα 802.3dj της IEEE βρίσκεται στη διαδικασία διαμόρφωσης του επερχόμενου προτύπου Ethernet, το οποίο περιλαμβάνει φυσικά επίπεδα και παραμέτρους διαχείρισης για ταχύτητες από 200G έως 1.6 Terabit ανά δευτερόλεπτο. Ο στόχος της ομάδας είναι ένας ρυθμός δεδομένων MAC Ethernet 1.6 Tbps, με στόχο ένα μέγιστο ποσοστό σφάλματος bit όχι μεγαλύτερο από 10-13 στο επίπεδο MAC. Περαιτέρω διατάξεις περιλαμβάνουν προαιρετικές διεπαφές μονάδων προσάρτησης 16 και 8 λωρίδων (AUI) κατάλληλες για διαφορετικές εφαρμογές τσιπ, αξιοποιώντας SerDes 112G και 224G. Φυσικά, η προδιαγραφή 1.6 Tbps συνεπάγεται μετάδοση μέσω 8 ζευγών χάλκινων καλωδίων twinax για έως και ένα μέτρο και 8 ζεύγη ινών για αποστάσεις μεταξύ 500 μέτρων και 2 χιλιομέτρων. Αν και η πλήρης επικύρωση του προτύπου αναμένεται την άνοιξη του 2026, το βασικό σύνολο χαρακτηριστικών προβλέπεται για την ολοκλήρωση του 2024.

Επιβάρυνση εύρους ζώνης και διόρθωση σφαλμάτων σε υποσυστήματα Ethernet 1.6T

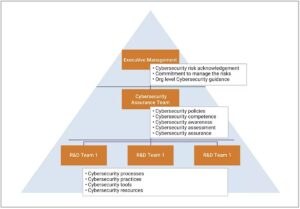

Εικ. 1: Διάγραμμα που απεικονίζει τα στοιχεία ενός υποσυστήματος Ethernet 1.6T.

Σε προηγούμενες επαναλήψεις Ethernet, το PCS επικεντρώθηκε κυρίως στην κωδικοποίηση δεδομένων για αξιόπιστη ανίχνευση πακέτων. Ωστόσο, με την κλιμάκωση στις ταχύτητες Ethernet 1.6 Τ, η ανάγκη για Διόρθωση Σφάλματος Προώθησης (FEC) γίνεται εμφανής, ιδιαίτερα για την εξουδετέρωση της υποβάθμισης του σήματος ακόμη και σε σύντομες ζεύξεις. Για το σκοπό αυτό, το 1.6T Ethernet συνεχίζει να χρησιμοποιεί το Reed-Solomon FEC. Αυτή η προσέγγιση δημιουργεί μια κωδική λέξη που περιλαμβάνει 514 σύμβολα 10-bit κωδικοποιημένα σε ένα μπλοκ συμβόλων 544, με αποτέλεσμα μια επιβάρυνση εύρους ζώνης 6%. Αυτές οι κωδικές λέξεις FEC κατανέμονται στους φυσικούς συνδέσμους AUI, έτσι ώστε κάθε φυσικός σύνδεσμος (8 για 1.6T Ethernet) να μην φέρει ολόκληρη κωδική λέξη. Αυτή η μέθοδος όχι μόνο παρέχει πρόσθετη προστασία από εκρήξεις σφαλμάτων, αλλά επιτρέπει επίσης την παραλληλοποίηση στον αποκωδικοποιητή μακρινών άκρων, μειώνοντας έτσι την καθυστέρηση.

Το Physical Medium Attachment (PMA), που διαθέτει κιβώτιο ταχυτήτων και SerDes, φέρνει το σήμα Ethernet στα εκπεμπόμενα κανάλια. Για 1.6T Ethernet, αυτό περιλαμβάνει 8 κανάλια το καθένα που τρέχουν στα 212 Gbps, αντιστοιχώντας σε 6% επιβάρυνση FEC. Η τεχνική διαμόρφωσης που χρησιμοποιείται είναι η Διαμόρφωση πλάτους παλμών 4 επιπέδων (PAM-4), η οποία κωδικοποιεί δύο bit δεδομένων για κάθε σύμβολο μετάδοσης, διπλασιάζοντας έτσι αποτελεσματικά το εύρος ζώνης όταν αντιπαρατίθεται με την παραδοσιακή προσέγγιση Μηδενικού Μηδενικού Επιστροφής (NRZ). Ο μηχανισμός μετάδοσης βασίζεται στη μετατροπή ψηφιακού σε αναλογικό, ενώ στο άκρο λήψης μια μετατροπή αναλογικού σε ψηφιακό σε συνδυασμό με DSP εξασφαλίζει ακριβή εξαγωγή σήματος.

Επιπλέον, είναι σημαντικό να σημειωθεί ότι το Ethernet PCS εισάγει ένα "εξωτερικό FEC" που εκτείνεται από άκρο σε άκρο σε μια σύνδεση Ethernet. Για την ενίσχυση των καναλιών μεγαλύτερης προσέγγισης, ένα πρόσθετο επίπεδο διόρθωσης σφαλμάτων για μεμονωμένες φυσικές γραμμές είναι στα σκαριά, πιθανότατα υιοθετώντας έναν κωδικό hamming FEC. Αυτή η διόρθωση αναμένεται να βρει την κύρια εφαρμογή της σε μονάδες οπτικού πομποδέκτη όπου μια τέτοια διόρθωση είναι επιτακτική.

Εικ. 2: Διάγραμμα που δείχνει πρόσθετο γενικό κόστος που προστίθεται όταν χρησιμοποιείται ένα συνενωμένο FEC για εκτεταμένη προσέγγιση.

Στο παράδειγμα του συστήματος που απεικονίζεται στο σχήμα 2, το MAC και το PCS συνδέονται μέσω μιας οπτικής μονάδας και ενός τεντώματος ινών. Το PCS έχει ποσοστό σφάλματος bit 10-5 στη σύνδεση της οπτικής μονάδας, συν τα σφάλματα από την ίδια την οπτική σύνδεση. Η χρήση ενός μοναδικού RS-FEC από άκρο σε άκρο δεν θα αρκούσε για την επίτευξη του 10-13 Πρότυπο Ethernet, καθιστώντας τη σύνδεση αναξιόπιστη. Μια επιλογή θα ήταν μια τριπλή εφαρμογή ξεχωριστού RS FEC σε κάθε hop, αυξάνοντας σημαντικά το κόστος και την καθυστέρηση. Μια πιο αποτελεσματική λύση είναι η ενσωμάτωση ενός συνδυασμένου κώδικα Hamming FEC ειδικά για την οπτική ζεύξη, καλύπτοντας τα τυπικά τυχαία σφάλματα των οπτικών συνδέσεων. Αυτό το εσωτερικό επίπεδο FEC δημιουργεί μια πρόσθετη επέκταση του ρυθμού γραμμής από 212 Gbps σε 226 Gbps, επομένως είναι σημαντικό το SerDes να μπορεί να υποστηρίξει αυτόν τον ρυθμό γραμμής.

Προκλήσεις καθυστέρησης σε συστήματα Ethernet 1.6T

Εικ. 3: Διαδρομή καθυστέρησης για υποσύστημα Ethernet 1.6T.

Διάφορα στοιχεία συμβάλλουν στον λανθάνοντα χρόνο Ethernet: η ουρά μετάδοσης, η διάρκεια μετάδοσης, ο μέσος χρόνος διέλευσης και αρκετοί χρόνοι επεξεργασίας και λήψης. Για να το οπτικοποιήσετε, σκεφτείτε το σχήμα 3, το οποίο εμφανίζει ένα ολοκληρωμένο υποσύστημα Ethernet 1.6T. Ενώ η καθυστέρηση μπορεί να επηρεαστεί από τον χρόνο αντίδρασης της εφαρμογής μακρινών άκρων, αυτός ο παράγοντας είναι εξωτερικός του Ethernet και επομένως συχνά αποκλείεται κατά την ανάλυση λανθάνουσας κατάστασης. Η ελαχιστοποίηση του λανθάνοντος χρόνου στη διεπαφή Ethernet απαιτεί κατανόηση των συγκεκριμένων περιστάσεων. Για παράδειγμα, η καθυστέρηση μπορεί να μην αποτελεί πρωταρχικό μέλημα για τις συνδέσεις κορμού μεταξύ διακοπτών λόγω εγγενών καθυστερήσεων σε πιο αργές συνδέσεις πελατών. Η απόσταση παίζει επίσης ρόλο. μεγαλύτερα μήκη εισάγουν περισσότερο λανθάνοντα χρόνο. Φυσικά, αυτό δεν σημαίνει ότι πρέπει να παραβλέπουμε την καθυστέρηση σε άλλα σενάρια, η μείωση της καθυστέρησης είναι πάντα ένας στόχος.

Η καθυστέρηση μετάδοσης συνδέεται εγγενώς με τον ρυθμό Ethernet και το μέγεθος του πλαισίου. Συγκεκριμένα, για ένα σύστημα Ethernet 1.6 Τ, η μετάδοση ενός πακέτου ελάχιστου μεγέθους απαιτεί 0.4 ns – ουσιαστικά, ένα πλαίσιο Ethernet ανά tick ενός ρολογιού 2.5 GHz. Από την άλλη πλευρά, η μετάδοση ενός τυπικού πλαισίου μέγιστου μεγέθους διαρκεί 8 ns, επεκτείνοντας τα 48 ns για τα Jumbo Frames. Το επιλεγμένο μέσο υπαγορεύει περαιτέρω την καθυστέρηση. Για παράδειγμα, η οπτική ίνα τυπικά παρουσιάζει καθυστέρηση 5 ns ανά μέτρο, ενώ η καλωδίωση από χαλκό είναι οριακά ταχύτερη στα 4 ns ανά μέτρο.

Ένα σημαντικό τμήμα της συνολικής καθυστέρησης βασίζεται στον ελεγκτή του δέκτη. Ο αποκωδικοποιητής RS FEC εισάγει εγγενώς λανθάνουσα κατάσταση. Για να ξεκινήσει η διόρθωση σφαλμάτων, το σύστημα πρέπει να λάβει 4 κωδικές λέξεις, οι οποίες, στα 1.6 Tbps, ανέρχονται σε 12.8 ns. Οι επόμενες δραστηριότητες, συμπεριλαμβανομένης της διόρθωσης σφαλμάτων και της αποθήκευσης στην προσωρινή μνήμη, ενισχύουν αυτόν τον λανθάνοντα χρόνο. Ενώ η διάρκεια αποθήκευσης κωδικών λέξεων FEC παραμένει σταθερή, η καθυστέρηση κατά τη λήψη του μηνύματος εξαρτάται από τη συγκεκριμένη υλοποίηση. Ωστόσο, η καθυστέρηση μπορεί να βελτιστοποιηθεί χρησιμοποιώντας σχολαστικές στρατηγικές ψηφιακού σχεδιασμού.

Στην ουσία, υπάρχει μια εγγενής, αναπόφευκτη καθυστέρηση λόγω του μηχανισμού FEC και της φυσικής απόστασης ή του μήκους του καλωδίου. Πέρα από αυτούς τους παράγοντες, η τεχνογνωσία του σχεδιασμού παίζει καθοριστικό ρόλο για την ελαχιστοποίηση της καθυστέρησης του ελεγκτή Ethernet. Η αξιοποίηση μιας ολοκληρωμένης λύσης που ενσωματώνει και βελτιστοποιεί τα MAC, PCS και PHY, ανοίγει το δρόμο για την πιο αποτελεσματική εφαρμογή με χαμηλό λανθάνοντα χρόνο.

Χαρακτηριστικά

Εικ. 4: Επιτυχία πυριτίου πρώτης διέλευσης για το Synopsys 224G Ethernet PHY IP σε διαδικασία 3nm που παρουσιάζει εξαιρετικά γραμμικά μάτια PAM-4.

Το Ethernet 1.6 Tbps είναι προσαρμοσμένο για τις πιο απαιτητικές εφαρμογές εύρους ζώνης και τις πιο ευαίσθητες σε καθυστέρηση εφαρμογές. Με την εμφάνιση της τεχνολογίας 224G SerDes, σε συνδυασμό με τις εξελίξεις στο MAC και το PCS IP, είναι πλέον διαθέσιμες ολοκληρωμένες λύσεις που συμμορφώνονται συνεχώς με τα εξελισσόμενα πρότυπα Ethernet 1.6T. Επιπλέον, λόγω της εγγενούς καθυστέρησης του πρωτοκόλλου και των μεθόδων διόρθωσης σφαλμάτων, η ψηφιακή και αναλογική σχεδίαση IP πρέπει να δημιουργηθεί επιμελώς από ειδικούς σχεδιαστές για να αποφευχθεί η εισαγωγή περιττής καθυστέρησης στη διαδρομή δεδομένων.

Η επίτευξη κορυφαίων επιδόσεων για σχέδια SoC 1.6T απαιτεί μια αποτελεσματικά βελτιστοποιημένη αρχιτεκτονική και σχολαστικές πρακτικές σχεδιασμού για κάθε στοιχείο τσιπ. Αυτό δίνει έμφαση στην εξοικονόμηση ενέργειας και ελαχιστοποιεί το αποτύπωμα πυριτίου, κάνοντας πραγματικότητα τους ρυθμούς δεδομένων 1.6 Τ. Αποδεδειγμένη με πυρίτιο Synopsys 224G Ethernet PHY IP έχει δημιουργήσει τη βάση για τον ελεγκτή 1.6T MAC και PCS. Χρησιμοποιώντας πρωτοποριακές τεχνικές σχεδίασης, ανάλυσης, προσομοίωσης και μέτρησης, η Synopsys συνεχίζει να παρέχει εξαιρετική ακεραιότητα σήματος και απόδοση jitter, με ολοκληρωμένη λύση Ethernet συμπεριλαμβανομένου MAC+PCS+PHY.

- SEO Powered Content & PR Distribution. Ενισχύστε σήμερα.

- PlatoData.Network Vertical Generative Ai. Ενδυναμώστε τον εαυτό σας. Πρόσβαση εδώ.

- PlatoAiStream. Web3 Intelligence. Ενισχύθηκε η γνώση. Πρόσβαση εδώ.

- PlatoESG. Ανθρακας, Cleantech, Ενέργεια, Περιβάλλον, Ηλιακός, Διαχείριση των αποβλήτων. Πρόσβαση εδώ.

- PlatoHealth. Ευφυΐα βιοτεχνολογίας και κλινικών δοκιμών. Πρόσβαση εδώ.

- πηγή: https://semiengineering.com/latency-considerations-for-1-6t-ethernet-designs/

- :έχει

- :είναι

- :δεν

- :που

- $UP

- 1

- 12

- 16

- 2024

- 2026

- 212

- 220

- 362

- 500

- 8

- a

- πρόσβαση

- προσιτός

- Λογιστήριο

- ακριβής

- Κατορθώνω

- απέναντι

- δραστηριοτήτων

- προστιθέμενη

- Πρόσθετος

- Επιπλέον

- υιοθετώντας

- εξελίξεις

- προχωρώντας

- κατά

- Στοχεύω

- επιτρέπεται

- ήδη

- Επίσης

- Αν και

- πάντοτε

- ενδιάμεσα

- Ποσά

- ενισχύουν

- an

- ανάλυση

- και

- Πρόβλεψη

- Εφαρμογή

- εφαρμογές

- πλησιάζω

- αρχιτεκτονική

- ΕΙΝΑΙ

- AS

- At

- αποφύγετε

- Πίσω μέρος

- φόντο

- εύρος ζώνης

- BE

- γίνεται

- μεταξύ

- Πέρα

- Κομμάτι

- Αποκλεισμός

- μαξιλάρα

- ενίσχυση

- Φέρνει

- Χτίζει

- αλλά

- by

- καλώδιο

- καλώδια

- CAN

- ικανότητες

- κουβαλάω

- προκλήσεις

- κανάλια

- τσιπ

- τσιπ

- επιλέγονται

- περιστάσεις

- πελάτης

- ρολόι

- Backup

- cloud computing

- κωδικός

- σε συνδυασμό

- συνδυάζοντας

- Επικοινωνία

- πλήρης

- ολοκλήρωση

- συστατικό

- εξαρτήματα

- περιεκτικός

- που περιλαμβάνει

- χρήση υπολογιστή

- Ανησυχία

- συνδυασμό

- συνδεδεμένος

- Διασυνδέσεις

- ΔΙΑΤΗΡΗΣΗ

- Εξετάστε

- θεωρήσεις

- συνεπής

- συνεχίζεται

- συνεχώς

- συμβάλλει

- έλεγχος

- ελεγκτής

- Μετατροπή

- Χαλκός

- πυρήνας

- Δικαστικά έξοδα

- αντενεργώ

- πορεία

- δημιουργημένο

- δημιουργεί

- Ρεύμα

- ημερομηνία

- Datacenter

- ντεμπούτο

- καθυστερήσεις

- παραδώσει

- Ζήτηση

- απαιτητικές

- απαιτήσεις

- που απεικονίζει

- Υπηρεσίες

- σχεδιαστές

- σχέδια

- Ανίχνευση

- Συσκευές

- υπαγορεύει

- διαφορετικές

- ψηφιακό

- επιμελώς

- οθόνες

- απόσταση

- διανέμονται

- Όχι

- διπλασιασμό

- δυο

- διάρκεια

- κατά την διάρκεια

- κάθε

- Νωρίτερα

- οικοσύστημα

- Αποτελεσματικός

- αποτελεσματικά

- αποδοτικότητα

- αποτελεσματικός

- αποτελεσματικά

- προσπάθειες

- εμφάνιση

- τονίζει

- δίνοντας έμφαση

- μισθωτών

- απασχολώντας

- δίνει τη δυνατότητα

- ενεργοποίηση

- περιλαμβάνει

- τέλος

- από άκρη σε άκρη

- εξασφαλίζει

- Ολόκληρος

- σφάλμα

- λάθη

- κλιμάκωση

- ουσία

- ουσιώδης

- κατ 'ουσίαν,

- Αιθέρας (ΕΤΗ)

- Even

- Κάθε

- εμφανές

- εξελίσσεται

- παράδειγμα

- εξαιρετικός

- εξαιρούνται

- Επέκταση

- επέκταση

- αναμένεται

- εμπειρογνώμονας

- εξειδίκευση

- επεκτείνουν

- επέκταση

- εξωτερικός

- εξαγωγή

- μάτια

- παράγοντας

- παράγοντες

- μακριά

- γρηγορότερα

- Χαρακτηριστικά

- Χαρακτηρίζοντας

- Εικόνα

- Εύρεση

- Όνομα

- Πρώτη γενιά

- ροή

- επικεντρώθηκε

- ακολουθείται

- Ίχνος

- Για

- διατύπωση

- Προς τα εμπρός

- ΠΛΑΙΣΙΟ

- από

- περαιτέρω

- γενεά

- δίνει

- μεγαλύτερη

- Group

- Ομάδα

- Μεγαλώνοντας

- χέρι

- Χειρισμός

- Ψηλά

- υψηλή απόδοση

- υψηλά

- Ωστόσο

- HTML

- HTTPS

- επιτακτικός

- εκτέλεση

- σπουδαιότητα

- σημαντικό

- βελτιωθεί

- in

- Σε άλλες

- περιλαμβάνουν

- Συμπεριλαμβανομένου

- αύξηση

- ατομικές

- βιομηχανικές

- επηρεάζονται

- συμφυής

- εκ φύσεως

- κινήσει

- Πρωτοβουλία

- παράδειγμα

- Ενσωματώνει

- ολοκλήρωση

- ακεραιότητα

- περιβάλλον λειτουργίας

- διεπαφές

- Internet

- Διαλειτουργικότητα

- σε

- εσωτερικός

- εισαγάγει

- Εισάγει

- εισάγοντας

- περιλαμβάνει

- IP

- IT

- επαναλήψεις

- ΤΟΥ

- εαυτό

- jpg

- Lane

- Αφάνεια

- στρώμα

- στρώματα

- Μήκος

- επίπεδα

- μόχλευσης

- Πιθανός

- γραμμή

- γραμμές

- LINK

- ΣΥΝΔΕΣΜΟΙ

- ζω

- πλέον

- Χαμηλός

- mac

- Κατασκευή

- διαχείριση

- διαχείριση

- max-width

- ανώτατο όριο

- Ενδέχεται..

- εννοώ

- μέτρηση

- μηχανισμός

- medium

- Μνήμη

- μήνυμα

- μέθοδος

- μέθοδοι

- λεπτολόγος

- ελάχιστος

- ελαχιστοποίηση

- ελαχιστοποιεί

- ελαχιστοποιώντας

- ενότητα

- ενότητες

- περισσότερο

- πλέον

- πρέπει

- πλησιάζοντας

- Ανάγκη

- δίκτυα

- παρ 'όλα αυτά

- Όχι.

- σημείωση

- τώρα

- σκοπός

- of

- συχνά

- on

- ONE

- αποκλειστικά

- λειτουργίας

- βελτιστοποιημένη

- Βελτιστοποιεί

- Επιλογή

- or

- ΑΛΛΑ

- επί

- φόρμες

- ζεύγη

- παράμετροι

- ιδιαίτερα

- μονοπάτι

- υπολογιστές

- για

- επίδοση

- παραστάσεις

- φυσικός

- Φυσικώς

- αγωγού

- πιλοτικές

- Πλάτων

- Πληροφορία δεδομένων Plato

- Πλάτωνα δεδομένα

- παίζει

- συν

- δυναμικού

- δύναμη

- πρακτικές

- πρωτίστως

- πρωταρχικός

- διαδικασια μας

- μεταποίηση

- επεξεργαστές

- εξέλιξη

- προβλέπεται

- προστασία

- πρωτόκολλο

- σφυγμός

- σκοπός

- Δραστήριος

- ποιότητα

- Ραδιόφωνο

- τυχαίος

- σειρά

- Τιμή

- Τιμές

- φθάσουν

- φθάνοντας

- αντίδραση

- Πραγματικότητα

- λαμβάνω

- λήψη

- υποδοχή

- μείωση

- αξιόπιστος

- λείψανα

- απόδοση

- Απαιτεί

- περιορισμένος

- με αποτέλεσμα

- εύρωστος

- Ρόλος

- ριζωμένος

- τρέξιμο

- Απεριόριστες δυνατότητες

- Κλίμακα

- σενάρια

- αδιάλειπτη

- Δεύτερος

- δει

- τμήμα

- ευαίσθητος

- ξεχωριστό

- εξυπηρετούν

- υπηρεσία

- σειρά

- διάφοροι

- Shared

- Κοντά

- θα πρέπει να

- ανάδειξη

- Σήμα

- σημαντικά

- Πυρίτιο

- προσομοίωση

- Μέγεθος

- So

- λύση

- Λύσεις

- εκτείνεται

- πρωταγωνιστή

- συγκεκριμένες

- ειδικά

- προσδιορισμός

- ταχύτητες

- άνοιξη

- Στάδιο

- πρότυπο

- τυποποίηση

- πρότυπα

- χώρος στο δίσκο

- στρατηγικές

- ροής

- μεταγενέστερος

- ουσιώδης

- επιτυχία

- τέτοιος

- κατάλληλος

- υποστήριξη

- σύμβολο

- σύστημα

- επειξειργασμένος από ραπτήν

- παίρνει

- τεχνική

- τεχνικές

- Τεχνολογία

- από

- ότι

- Η

- τους

- Εκεί.

- εκ τούτου

- επομένως

- Αυτοί

- αυτό

- Μέσω

- Ετσι

- τσιμπούρι

- Δεμένος

- ώρα

- φορές

- προς την

- κορυφή

- παραδοσιακός

- ΚΙΝΗΣΗ στους ΔΡΟΜΟΥΣ

- μεταφορά

- μεταδίδουν

- Τριπλούς

- δύο

- τυπικός

- συνήθως

- αναπόφευκτος

- κατανόηση

- αναλαμβάνουν

- μονάδα

- ανερχόμενος

- επάνω σε

- χρησιμοποιώντας

- χρησιμοποιώ

- μέσω

- φαντάζομαι

- Τρόπος..

- we

- πότε

- Ποιό

- ενώ

- ευρύτερο

- με

- εντός

- θα

- ακόμη

- zephyrnet

- μηδέν