Den var ind igen 1991 at Cadence først annoncerede Virtuoso-produktnavnet, og her er vi 32 år senere, og produktet lever og klarer sig ganske godt. Steven Lewis fra Cadence gav mig en opdatering om noget nyt, som de kalder Virtuos Studio, og det handler om tilpasset IC-design til den virkelige verden. I de 32 år har vi set halvlederprocessen marchere langs Moores lov fra 600nm ved hjælp af plan CMOS, nedskaleret til FinFET-æraen under 22 nm, og nået GAA ved 3nm-knuden. Det er klart, at EDA-værktøjskravene har ændret sig, efterhånden som mindre knudepunkter medførte nye fysiske effekter, som skulle modelleres og simuleres for at sikre første siliciumsucces.

Fokus for Cadence Virtuoso Studio er at hjælpe IC-designere med at tage nutidens udfordringer op gennem seks områder:

- Øget proceskompleksitet

- Håndtering af 10,000-vis af kredsløbssimuleringer

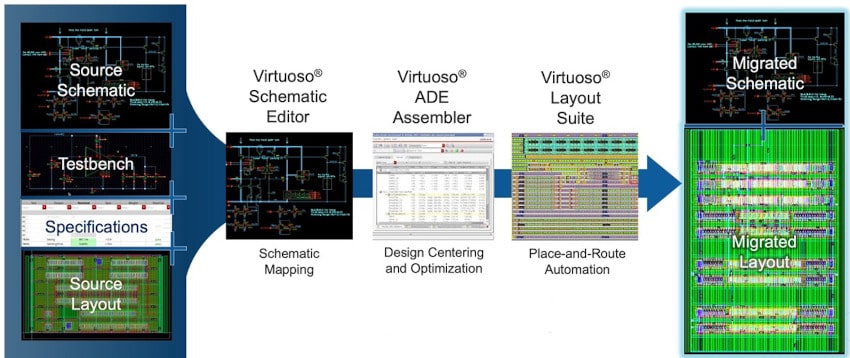

- Designautomatisering og kredsløbsmigrering

- Heterogen integration

- AI

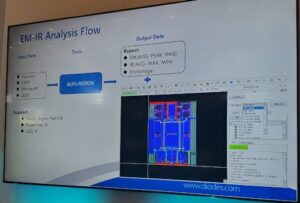

- Sign-off, in-design verifikation og analyse

Virtuos ADE (Analog Design Environment) giver kredsløbsingeniører mulighed for at udforske deres analoge, blandede signal- og RFIC-design gennem skematisk indfangning og kredsløbssimulering. Arkitekturen i Virtuoso ADE er blevet fornyet til bedre jobkontrol, reduceret RAM-forbrug og fremskyndet simuleringer ved at bruge skyen. For et eksempel blev den RAM, der kræves for at køre Spectre på 10,000-vis af simuleringer, reduceret fra 420 MB ned til kun 18 MB til simuleringsovervågning, mens udtryksevalueringer faldt fra 420 MB RAM til kun 280 MB.

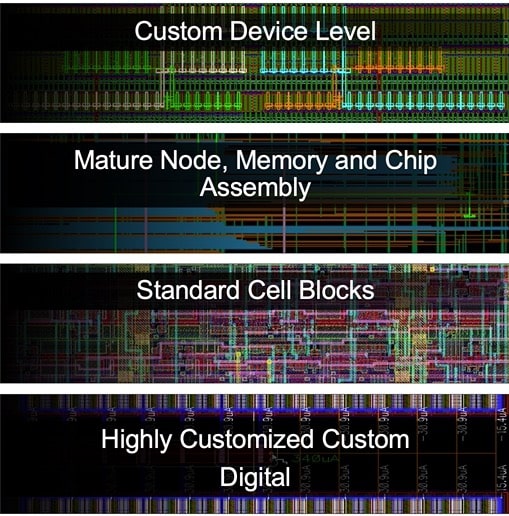

Opdateringer til Virtuos Layout Suite omfatter fire valg af sted- og ruteteknologi, som hver er egnet til den unikke opgave, der er ved hånden gennem det virtuose miljø:

Fire P&R-teknologier

DRC- og LVS-kørsler er en del af fysisk verifikation, og at køre disse i batch-tilstand, fiksering og gentagelse, fører til lange udviklingsplaner. In-design-verifikation tillader interaktiv brug af DRC og LVS, mens der arbejdes på et IC-layout, så feedback om, hvad der skal ændres, bliver hurtigt fremhævet, hvilket accelererer produktiviteten. En layoutdesigner, der bruger Virtuoso Layout Suite, drager fordel af in-design-verifikation ved hjælp af Pegasus DRC og LVS teknologi.

Chiplets, 2.5D og 3D emballage spænder over de traditionelt adskilte områder af PCB, pakke og IC design domæner. Virtuoso Studio muliggør co-design og verifikation af pakker, moduler og IC'er ved at:

Ser du ind i den nærmeste fremtid, kan du forvente at se detaljer dukke op om, hvordan AI bliver anvendt til automatisk at gå fra en analog skematisk til layout baseret på maskinlæring og specifikationer. Disse autogenererede prøvelayouts vil yderligere fremskynde en meget arbejdskrævende proces. Et andet udviklingsområde for AI, der skal anvendes, er problemet med at migrere tilpasset analog IP til en ny procesknude. Bliv hængende.

Tidlige kunder hos Virtuoso Studio inkluderer analoge enheder til co-design af IC og pakke, førende IC-forbrugerdesign hos MediaTek og AI-baseret procesmigrering hos Renesas.

Resumé

Virtuoso Studio har udgivet 23.1 nogle imponerende nye funktioner, som IC-designteams kan begynde at bruge for at blive mere produktive. Den virtuose infrastruktur har ændret sig for at imødekomme udfordringerne i Moores lov, simuleringer med 10,000 kredsløbssimuleringer er praktiske, RFIC og modul 2.5D/3D co-design er understøttet, in-design DRC/LVS-verifikation tager meget kortere tid, og AI er anvendes til at automatisere analoge opgaver.

Relaterede blogs

Del dette opslag via:- SEO Powered Content & PR Distribution. Bliv forstærket i dag.

- Platoblokkæde. Web3 Metaverse Intelligence. Viden forstærket. Adgang her.

- Udmøntning af fremtiden med Adryenn Ashley. Adgang her.

- Kilde: https://semiwiki.com/eda/327556-whats-new-with-cadence-virtuoso/

- :har

- :er

- $OP

- 1

- 10

- 3d

- a

- Om

- accelererende

- AI

- Alle

- tillader

- sammen

- ,

- annoncerede

- anvendt

- arkitektur

- ER

- OMRÅDE

- områder

- AS

- At

- automatisere

- automatisk

- Automation

- tilbage

- baseret

- BE

- været

- være

- jf. nedenstående

- fordele

- Bedre

- bragte

- by

- kadence

- ringe

- CAN

- fange

- udfordringer

- lave om

- valg

- tydeligt

- Cloud

- forbruger

- kontrol

- skik

- Kunder

- dag

- krav

- Design

- Designer

- designere

- designs

- detaljer

- Udvikling

- Enheder

- gør

- Domæner

- ned

- hver

- effekter

- muliggør

- Ingeniører

- sikre

- Miljø

- Era

- evalueringer

- eksempel

- forvente

- udforske

- Funktionalitet

- tilbagemeldinger

- Fornavn

- Fokus

- Til

- fire

- fra

- yderligere

- fremtiden

- Go

- hånd

- Have

- hjælpe

- link.

- Fremhævet

- Hvordan

- HTML

- HTTPS

- ICS

- imponerende

- in

- omfatter

- Infrastruktur

- interaktiv

- IP

- Job

- jpg

- arbejdskraft

- Lov

- Layout

- Leads

- læring

- Lewis

- Lang

- maskine

- machine learning

- Marts

- max-bredde

- Mød

- migration

- tilstand

- modul

- Moduler

- overvågning

- mere

- navn

- I nærheden af

- behov

- Ny

- Nye funktioner

- node

- noder

- of

- on

- ONE

- pakke

- pakker

- emballage

- del

- fysisk

- Place

- plato

- Platon Data Intelligence

- PlatoData

- Indlæg

- Praktisk

- præsentere

- Problem

- behandle

- Produkt

- produktiv

- produktivitet

- sætte

- hurtigt

- RAM

- nå

- ægte

- virkelige verden

- Reduceret

- reducere

- frigive

- påkrævet

- R

- Kør

- kører

- skalering

- Anden

- se detaljer

- halvleder

- adskille

- Silicon

- simulation

- SIX

- mindre

- So

- nogle

- noget

- span

- specifikationer

- Spectrum

- hastighed

- starte

- forblive

- Studio

- succes

- suite

- Understøttet

- Tag

- tager

- Opgaver

- opgaver

- hold

- Teknologier

- at

- deres

- Disse

- Gennem

- tid

- til

- værktøj

- traditionelt

- retssag

- enestående

- Opdatering

- Brug

- brug

- Verifikation

- via

- GODT

- Hvad

- mens

- vilje

- med

- arbejder

- world

- år

- zephyrnet