I det hurtigt udviklende landskab af kunstig intelligens (AI) og dataintensive applikationer har efterspørgslen efter højtydende sammenkoblingsteknologier aldrig været mere kritisk. Selv 100G Interconnect er allerede ikke hurtig nok til infrastrukturapplikationer. AI-applikationer med deres massive datasæt og komplekse algoritmer driver behovet for hidtil usete dataoverførselshastigheder. 224G Serializer/Deserializer (SerDes) står i spidsen for højhastighedsdatakommunikationsrevolutionen og indvarsler en ny æra med hidtil uset ydeevne og tilpasningsevne.

Alphawave erkender dette markedsbehov og adresserer det direkte med sine avancerede 200G-sammenkoblingsteknologier. Det er et vidnesbyrd om virksomhedens forpligtelse til at være på forkant med datakurven og give industrier den hastighed og effektivitet, der er nødvendig for at drive kunstig intelligens og højtydende computere ind i fremtiden.

For nylig var virksomheden vært for et webinar om dette emne og delte resultater fra deres AthenaCORE 224G SerDes TestChip. Dette indlæg tager et kig på Alphawaves bestræbelser på at frigøre 1.6T-økosystemet med dets omfattende tilbud, herunder dets 200G-sammenkoblingsteknologi.

Udnyttelse af Alphawaves 112G SerDes-succes til at levere robuste 224G SerDes

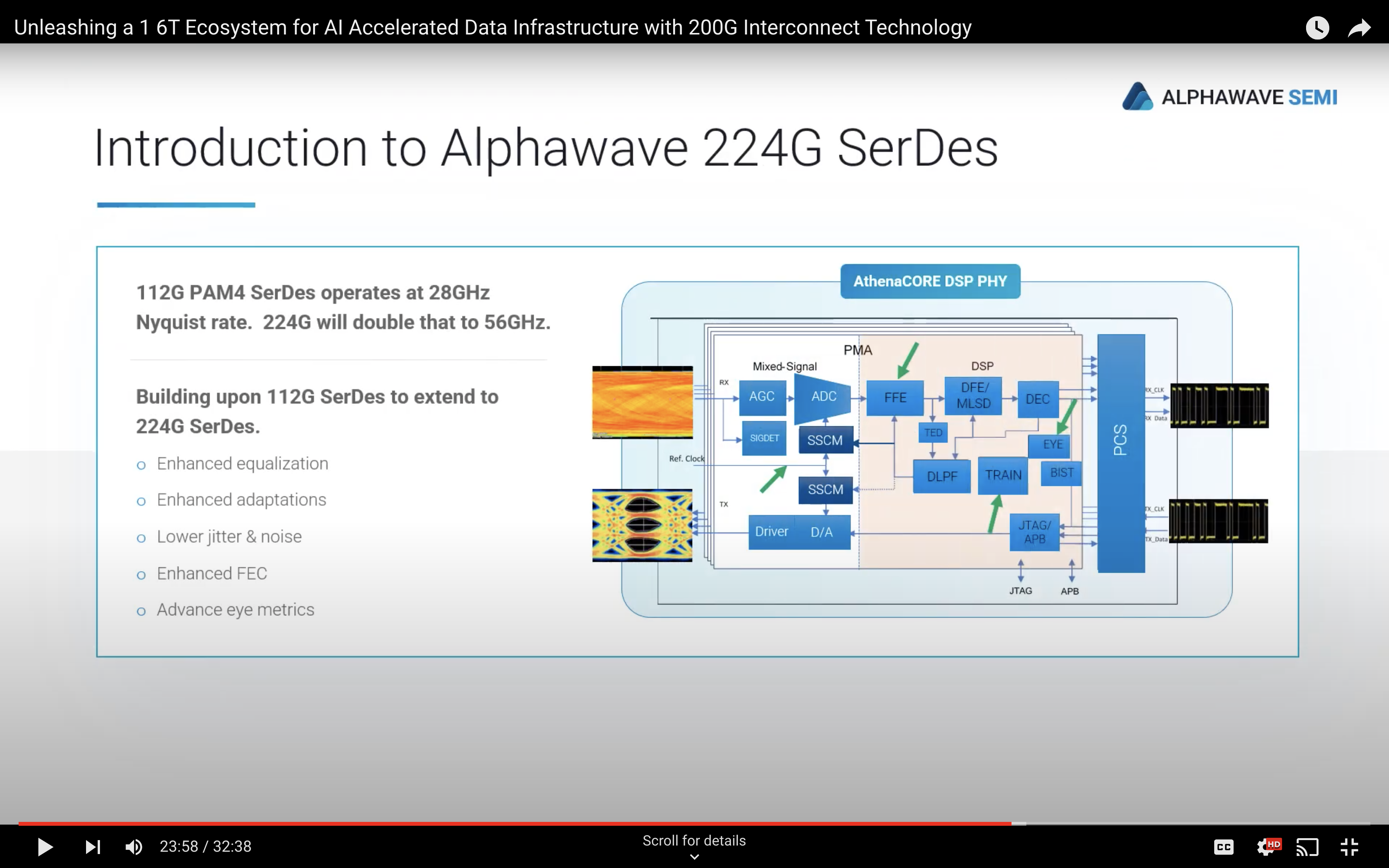

Ved at udvide sine gennemprøvede 112G SerDes til at understøtte en bemærkelsesværdig 224Gbps, har Alphawave ikke kun fordoblet datahastigheden, men har også låst op for nye muligheder for dataintensive applikationer, især inden for kunstig intelligens (AI) og avanceret databehandling. At overvinde de tilknyttede udfordringer og kompleksiteter ved 200G Interconnect krævede en kombination af avancerede teknologier, innovative designtilgange og samarbejdsbestræbelser inden for industrien. Alphawave har bygget videre på denne 112G SerDes-succes for at levere de endnu strengere krav til en 224G SerDes.

Den AlphaCORE DSP-baserede Serializer/Deserializer (SerDes)-arkitektur er konstrueret til at levere alsidige højhastighedsdatakommunikationsløsninger med en konfigurerbar 112G Digital Signal Processor (DSP). Konfigurerbarheden af DSP-arkitekturen muliggør tilpasning til forskellige applikationer og ydeevnekrav, hvilket giver et plug-and-play modulært design til udskiftelighed og nem integration. Med en datahastighed på 112 gigabit pr. sekund (112G), er arkitekturen på linje med kravene til moderne datakommunikation inden for områder som datacentre, netværk og højtydende databehandling. Med vægt på applikationstilpassede løsninger, fleksibilitet og tilpasningsevne kan SerDes skræddersyes til specifikke brugssituationer, hvilket viser dens evne til at optimere ydeevnen til forskellige applikationer og miljøer. Inkluderingen af en DSP understreger dens betydning i opgaver som udligning, fejlkorrektion og signalkonditionering. Arkitekturen er designet til nem integration og kan tilpasses forskellige Plug and Play-moduler og sikrer problemfri kompatibilitet med forskellige komponenter og funktionaliteter. Som en højhastighedskommunikationsløsning opfylder arkitekturen de skiftende krav til datahastigheder og stemmer overens med fremskridt inden for kommunikationsstandarder, hvilket gør den velegnet til dynamiske og fremtidsorienterede kommunikationsmiljøer.

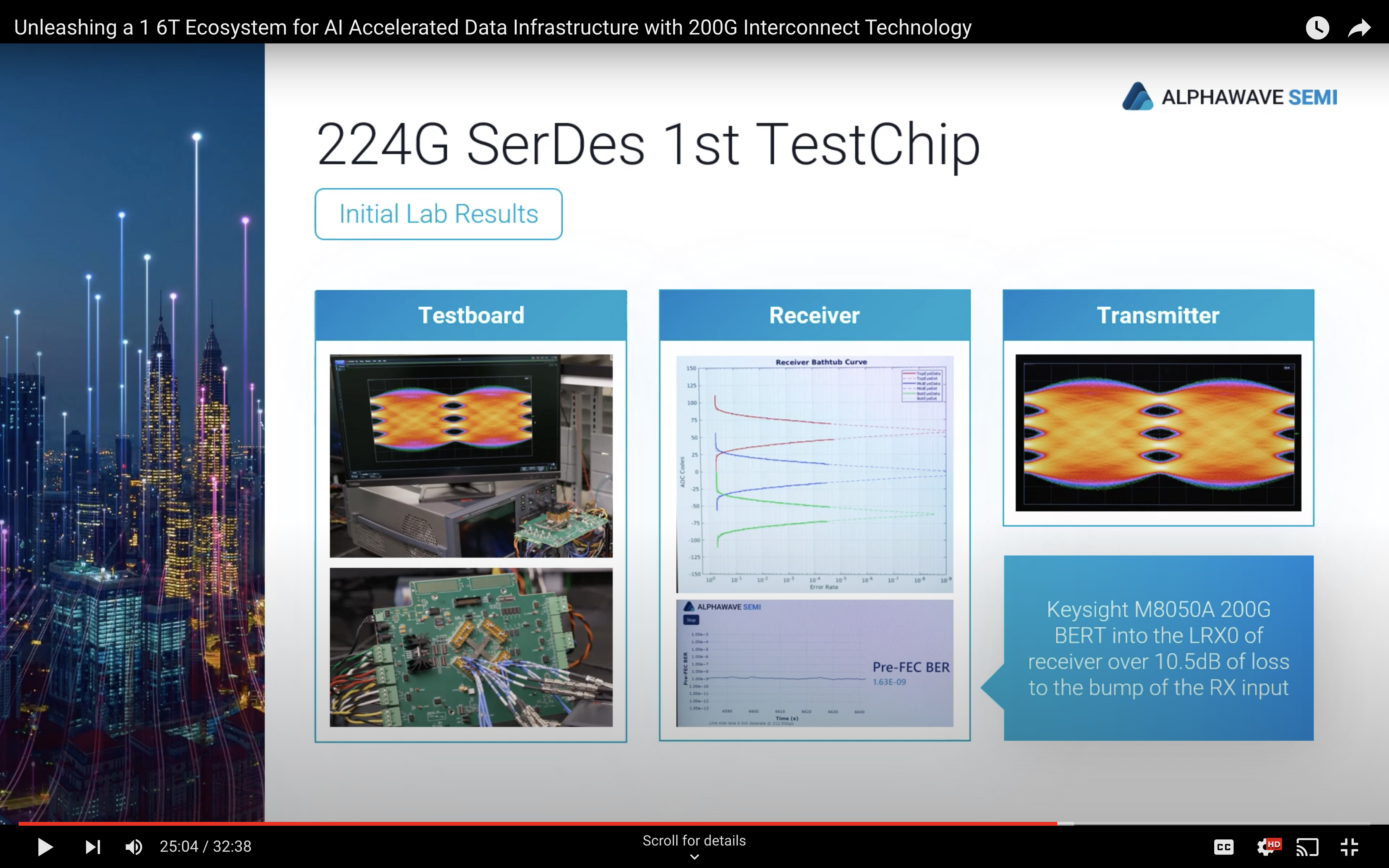

AthenaCORE 224G SerDes TestChip resultater

Alphawaves innovative udviklingsindsats

Alphawaves 200G sammenkoblingsteknologier handler ikke kun om hastighed, men også om effektivitet og pålidelighed. 200G-sammenkoblingsudfordringerne omfatter signalintegritetsproblemer, krydstale og spredning. Virksomheden investerer i avancerede modulationsordninger, såsom PAM4 (Pulse Amplitude Modulation 4), som gør det muligt at kode flere bits i et enkelt symbol, hvilket effektivt øger datahastigheden. Alphawave anvender også avancerede DSP-teknikker og adaptive fejlkorrektionsskemaer for at forbedre pålideligheden og ydeevnen af datatransmission ved 200G-hastigheder.

Avancerede DSP-teknikker

Maximum Likelihood Sequence Detectors (MLSD) repræsenterer en sofistikeret digital signalbehandlingsteknik (DSP) anvendt i kommunikationssystemer, især effektiv i scenarier med intersymbolinterferens (ISI). I modsætning til konventionelle metoder, der sigter mod at eliminere ISI, udnytter MLSD entydigt energien inden for interferens for at øge signalstyrken og optimere symbolsekvensdetektion. Dens matematisk optimale tilgang involverer en udtømmende søgning over alle mulige symbolsekvenser, hvilket minimerer middelkvadratfejl for at identificere den transmitterede sekvens. Anerkendt for sin kapacitet til at forbedre systemets ydeevne betydeligt, anvendes MLSD især i højhastighedsdatakommunikation og optisk kommunikation, og adresserer bekymringer relateret til signalforvrængning på grund af ISI. Mens MLSD's beregningsmæssige krav rejser kompleksitetsovervejelser, understreger teknikkens tilpasningsevne til forskellige kanalforhold dens effektivitet i dynamiske kommunikationsmiljøer.

Forward Error Correction (FEC)-strategier

Alphawave omfavner adaptive Forward Error Correction (FEC)-strategier, der giver mulighed for dynamiske justeringer baseret på kanalforhold i realtid. Denne fleksibilitet sikrer optimal ydeevne uden at gå på kompromis med båndbreddeeffektiviteten. FEC giver systemer mulighed for at etablere højere Bit Error Rate (BER) mål på elektriske links, hvilket giver en tærskel for at tolerere og rette fejl. Adaptiv FEC justerer dynamisk fejlkorrektionsstyrke, balanceringskorrektion og båndbreddeeffektivitet baseret på kanalforhold i realtid. Stigningen af adaptive og dynamiske FEC-strategier forbedrer systemets tilpasningsevne, mens integration med avancerede moduleringsskemaer optimerer ydeevnen, især i højhastigheds- og optiske kommunikationssystemer.

Alsidige muligheder for at understøtte 1.6T-økosystemet

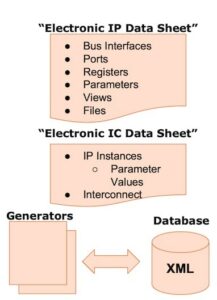

Alphawave giver alsidige muligheder for switch-ASIC'er (Application-Specific Integrated Circuits) i 1.6T-økosystemet. Dette inkluderer muligheden for at holde sig til 512 × 100G-links eller udnytte 256 x 200G-links i en 1RU – 32 Port Switch-konfiguration, der tilbyder skalerbarhed og fleksibilitet til forskellige implementeringsscenarier. Virksomhedens UCle-aktiverede chiplets åbner op for nye muligheder for modularitet og skalerbarhed på chipniveau for at imødekomme højhastighedshukommelses- og computerkrav til infrastrukturapplikationer. Med sin 2.5D/3D-emballage og applikationsoptimerede IP navigerer virksomheden i den delikate balance mellem kompleksitet og ydeevne for at levere avancerede løsninger.

Interoperabilitet mellem flere leverandører

Tilskyndelse til innovation spænder interoperabilitet over forskellige dimensioner, herunder formfaktorer, SerDes-grænseflader og administrationssoftware, med det ultimative mål at opnå systemkompatibilitet. Interoperabilitet mellem flere leverandører er en kritisk faktor for indførelse og succes af nye teknologier. Tidlige brugere drager fordel af et bredere udvalg af kompatible produkter, mens downstream-implementere udnytter interoperabilitet til at strømline udvikling, hvilket reducerer tid og omkostninger. Ved at sætte præstationsstandarder sikrer interoperabilitet, at brugerne kan forudse, hvordan forskellige komponenter vil fungere sammen i et system. Dette fremmer hurtigere adgang til billigere teknologi, drevet af konkurrence i et mangfoldigt økosystem af interoperable løsninger.

Arbejde med standardiseringsorganer

Alphawave forstår vigtigheden af interoperabilitet mellem flere leverandører og engagerer sig aktivt med industristandardorganer som OIF (Optical Internetworking Forum) og IEEE 802.3 for at bidrage til udviklingen af 200G-signalstandarder. Dette samarbejde sikrer interoperabilitet og sætter scenen for den sømløse integration af Alphawaves teknologier i det bredere økosystem. Alphawaves robuste specifikationer og overholdelse af industristandarder sikrer, at dets 200G-sammenkoblingsteknologier problemfrit integreres med en række forskellige systemer.

Resumé

Ved aktivt at bidrage til industristandarder, investere i avancerede teknologier og levere alsidige løsninger er Alphawave en vigtig aktør i at gøre 1.6T-økosystemet til mainstream for æraen med kunstig intelligens. Alphawave tilbyder en omfattende suite af løsninger designet til højtydende tilslutningsmuligheder. Deres High-Performance Connectivity IP spænder over afgørende områder som PCIe/CXL, Ethernet og HBM/DDR, og opfylder kravene til højhastighedsdatakommunikation. Inkorporeringen af chiplet-teknologi, især ved at udnytte UCle, indikerer en forpligtelse til sømløs chiplet-sammenkobling. De specifikke chiplettyper – IO, Memory og Compute – understreger en modulær tilgang, der tillader forskellige chiplets at fungere harmonisk sammen.

I takt med at dataintensive applikationer fortsætter med at udvikle sig, positionerer Alphawaves forpligtelse til innovation det som en nøglemuligator for fremtidens højhastigheds-, pålidelige og skalerbare AI-datainfrastruktur. I det væsentlige er Alphawave en nøglespiller i at muliggøre fleksibilitet, skalerbarhed og innovation for det kommende 1.6T-økosystem.

For at lytte til webinaret, besøg her.

Læs også:

Disaggregerede systemer: Muliggør computing med UCIe Interconnect og chiplet-baseret design

Interface IP i 2022: 22 % år-til-vækst stadig datacentreret

Alphawave Semi Besøg på #60DAC

Del dette opslag via:

- SEO Powered Content & PR Distribution. Bliv forstærket i dag.

- PlatoData.Network Vertical Generative Ai. Styrk dig selv. Adgang her.

- PlatoAiStream. Web3 intelligens. Viden forstærket. Adgang her.

- PlatoESG. Kulstof, CleanTech, Energi, Miljø, Solenergi, Affaldshåndtering. Adgang her.

- PlatoHealth. Bioteknologiske og kliniske forsøgs intelligens. Adgang her.

- Kilde: https://semiwiki.com/ip/alphawave/339080-unleashing-the-1-6t-ecosystem-alphawave-semis-200g-interconnect-technologies-for-powering-ai-data-infrastructure/

- :har

- :er

- :ikke

- $OP

- 1

- 1.

- 2022

- 32

- a

- evne

- Om

- adgang

- opnå

- tværs

- aktivt

- tilpasning

- adaptive

- adresse

- adresser

- adressering

- adhærens

- justeringer

- adoptanter

- Vedtagelse

- fremskreden

- fremskridt

- forude

- AI

- AI -data

- sigte

- algoritmer

- Justerer

- Alle

- tillade

- tillader

- allerede

- også

- an

- ,

- foregribe

- applikationer

- anvendt

- tilgang

- tilgange

- arkitektur

- ER

- områder

- kunstig

- kunstig intelligens

- Kunstig intelligens (AI)

- AS

- opstigning

- Asics

- forbundet

- At

- Balance

- afbalancering

- båndbredde

- baseret

- BE

- været

- gavner det dig

- mellem

- Bit

- organer

- boost

- bredere

- bygget

- men

- by

- kaldet

- CAN

- Kapacitet

- tilfælde

- catering

- Centers

- udfordringer

- Kanal

- samarbejde

- kollaborativ

- kombination

- engagement

- Kommunikation

- kommunikationssystemer

- Kommunikation

- selskab

- Selskabs

- kompatibilitet

- kompatibel

- konkurrence

- komplekse

- kompleksiteter

- kompleksitet

- komponenter

- omfattende

- at gå på kompromis

- beregningsmæssige

- Compute

- computing

- Bekymringer

- betingelser

- Konfiguration

- Connectivity

- overvejelser

- fortsæt

- bidrage

- bidrager

- konventionelle

- Omkostninger

- kritisk

- afgørende

- skøger

- banebrydende

- data

- datacentre

- datainfrastruktur

- datasæt

- levere

- Efterspørgsel

- krav

- implementering

- udruller

- Design

- konstrueret

- Detektion

- Udvikling

- forskellige

- digital

- størrelse

- Spredning

- forskelligartede

- fordoblet

- drevet

- kørsel

- grund

- dynamisk

- dynamisk

- Tidligt

- tidlige adoptører

- lette

- let

- økosystem

- Effektiv

- effektivt

- virkningsfuldhed

- effektivitet

- indsats

- eliminere

- Omfavnelser

- vægt

- selvstændige

- bemyndigelse

- bemyndiger

- muliggør

- muliggør

- muliggør

- energi

- indgreb

- manipuleret

- forbedre

- Forbedrer

- nok

- sikre

- sikrer

- miljøer

- Era

- fejl

- fejl

- Essensen

- etablere

- Endog

- udvikle sig

- udviklende

- strækker

- faktor

- faktorer

- FAST

- Med

- Fields

- Fleksibilitet

- Til

- forkant

- formular

- forum

- Videresend

- Fosters

- fra

- funktion

- funktionaliteter

- fremtiden

- mål

- Vækst

- link.

- Høj ydeevne

- højere

- hostede

- Hvordan

- HTTPS

- identificere

- IEEE

- betydning

- vigtigt

- in

- omfatter

- omfatter

- Herunder

- inklusion

- stigende

- angiver

- industrier

- industrien

- industristandarder

- Infrastruktur

- Innovation

- innovativ

- integrere

- integreret

- integration

- integritet

- Intelligens

- grænseflader

- interferens

- Interoperabilitet

- interoperable

- ind

- investere

- investerer

- involverer

- IP

- spørgsmål

- IT

- ITS

- Nøgle

- nøglespiller

- landskab

- Leverage

- løftestang

- ligesom

- sandsynlighed

- links

- Se

- Mainstream

- Making

- ledelse

- Marked

- massive

- matematisk

- max-bredde

- betyde

- opfylder

- Hukommelse

- metoder

- minimering

- Moderne

- modulær

- Moduler

- mere

- flere

- Navigerer

- Behov

- behov

- netværk

- aldrig

- Ny

- Nye teknologier

- især

- of

- tilbyde

- tilbud

- Tilbud

- on

- kun

- åbner

- drift

- optimal

- Optimer

- Optimerer

- optimering

- Indstillinger

- or

- i løbet af

- overvinde

- emballage

- især

- per

- ydeevne

- plato

- Platon Data Intelligence

- PlatoData

- Leg

- spiller

- stik

- plug and play

- positioner

- muligheder

- mulig

- Indlæg

- magt

- strømforsyning

- forarbejdning

- Processor

- Produkter

- Fremdrive

- gennemprøvet

- giver

- leverer

- puls

- hurtigere

- rejse

- rækkevidde

- hurtigt

- Sats

- priser

- Læs

- realtid

- rige

- anerkendt

- anerkender

- reducere

- relaterede

- pålidelighed

- pålidelig

- bemærkelsesværdig

- repræsentere

- Krav

- Resultater

- revolution

- robust

- Skalerbarhed

- skalerbar

- scenarier

- ordninger

- sømløs

- problemfrit

- Søg

- Anden

- Semi

- Sequence

- sæt

- indstilling

- delt

- fremvisning

- Signal

- betydning

- betydeligt

- enkelt

- Software

- løsninger

- Løsninger

- sofistikeret

- spændvidder

- specifikke

- specifikationer

- hastighed

- hastigheder

- firkant

- Stage

- standarder

- står

- opholder

- Stick

- Stadig

- strategier

- strømline

- styrke

- stringent

- succes

- sådan

- suite

- support

- Kontakt

- symbol

- systemet

- Systemer

- skræddersyet

- tager

- mål

- opgaver

- teknik

- teknikker

- Teknologier

- Teknologier

- testamente

- at

- Fremtiden

- deres

- denne

- tærskel

- tid

- til

- sammen

- i morgen

- emne

- mod

- overførsel

- ultimativ

- understregninger

- forstår

- entydigt

- udløsningen

- I modsætning til

- uden fortilfælde

- kommende

- på

- brug

- brugere

- varsler

- række

- forskellige

- Varierende

- alsidige

- via

- Besøg

- webinar

- som

- mens

- vilje

- med

- inden for

- uden

- X

- zephyrnet