Med et stigende antal virksomheder, der er interesseret i enheder baseret på RISC-V ISA, og et voksende antal kerner, acceleratorer og infrastrukturkomponenter, der gøres tilgængelige, enten kommercielt eller i open source-form, står slutbrugere over for en stadig sværere udfordring med at sikre, at de træffer de bedste valg.

Hver bruger vil sandsynligvis have et sæt behov og bekymringer, der næsten svarer til fleksibiliteten i RISC-V-tilbuddene, og strækker sig langt ud over traditionelle PPA-målinger til sikkerheds- og sikkerhedshensyn eller kvalitetsovervejelser. Det kunne omfatte tilpasningsevnen af verifikationssikkerheden, som gør det muligt for den arkitektoniske udvidelse og den nødvendige verifikation at følge med.

Traditionelt er tre niveauer af prototyping blevet implementeret - virtuelle prototyper, emulering og FPGA-prototyper, inklusive hybrider mellem dem. Hver platform bruges derefter til en række formål, herunder softwareverifikation, arkitektonisk validering, funktionel verifikation af hardwaren, ydeevneanalyse og meget mere.

Mens design- og softwareøkosystemerne til RISC-V er ved at blive etableret, er konfigurations- og verifikationsøkosystemerne bagud og kræver, at ny teknologi bygges. Det er selve fleksibiliteten ved RISC-V, der skaber enorme udfordringer for verifikation, ud over hvad der kræves for verifikation af faste processorer. Det gør også hardware-software co-udvikling ikke kun mulig, men nødvendig.

Samudvikling

Tidligere blev hardware udvalgt og derefter udviklet software til at køre på det. Med RISC-V er hardwaren ofte drevet af software. "Det første, du skal vælge, er, hvilke standard RISC-V-muligheder du ønsker," siger Simon Davidmann, grundlægger og administrerende direktør for Imperas software. “RISC-V-funktionssættet har i øjeblikket 200 eller 300 muligheder. Hvordan ved du, om din algoritme ville have gavn af en flydende komma-enhed eller SIMD, hardwaremultiplikatorer eller endda en vektormotor? Du skal finde ud af de hardwarefunktioner, du har brug for, og har råd til, til den type applikation eller det job, du ønsker, at processoren skal udføre. Det bliver i sig selv lidt af en udfordring.”

Der kræves prototyper for at lave den slags afvejninger. "Hvis designerens mål er at evaluere ydeevne og egnet til formålet, så er virtuel prototyping det eneste levedygtige valg," siger Steve Roddy, CMO hos Quadric. "At bygge hardwareprototyper er mere end 10 til 50 gange mere tidskrævende end at skabe en SystemC-model af et undersystem eller hele SoC. Den virtuelle SystemC-prototype kører generelt hurtigt nok til at besvare præstationsspørgsmål, såsom hvor mange frames per sekund af gennemløb kan jeg få med denne processorkerne, eller hvad er peak- og gennemsnitsbåndbreddekravet for funktion X inden for en acceptabel nøjagtighedsramme."

Det kan være svært at få den rigtige nøjagtighed. "Det handler om nøjagtighed og din evne til at spinde en model meget hurtigt," siger Frank Schirrmeister, vicepræsident for løsninger og forretningsudvikling hos Arteris IP. “Den rigtige nøjagtighed er defineret af, hvad end dit spørgsmål kræver, og det er ikke trivielt at generere dem. Hvis du er en ASIP-udbyder, vil du være i stand til at generere dem fra den skabelon, du har. Afhængigt af spørgsmålet kan du have brug for pipeline-nøjagtighed, du kan have brug for hukommelsesnøjagtighed, det behøver ikke at være helt nøjagtigt, men når du har en CAD-afdeling involveret, er de for bange for at svare på det forkerte spørgsmål.”

Men nøjagtighed er en afvejning mod hastighed. "Selvom nogle virtuelle prototyper er cykluspræcise, kører disse ofte for langsomt til at kunne have den nødvendige softwaregennemstrømning," siger Imperas' Davidmann. "De højeste ydeevne virtuelle prototyper er ikke ydeevnemotorer, fordi de ikke modellerer processorpipelines. De ser på det fra et softwaresynspunkt, hvor du kan kompilere det og køre det på hardware, og du kan se omtrentlig ydeevne ved at se på instruktionstællinger eller omtrentlige timingestimater. Dette burde være nok til at træffe denne form for arkitektonisk beslutning."

Det kræver ofte flere prototyper. "Vi prototyper generelt af to årsager," siger Venki Narayanan, seniordirektør for software- og systemudvikling i Microchip Technologys FPGA-forretningsenhed. "Den ene er for arkitektonisk validering for at sikre, at vi opfylder alle præstationsmålinger og krav og funktionel validering. Den anden grund er indlejret software og firmwareudvikling. Vi bruger forskellige niveauer af prototyping-teknikker, hvor det mest almindelige er at bruge vores egne FPGA'er til at udvikle en emuleringsplatform til både arkitektonisk og funktionel validering. Vi bruger også arkitektoniske modeller som QEMU til at bygge virtuelle platforme til både præstationsvalidering og indlejret softwareudvikling."

Antallet af muligheder vokser. "Der er mange måder, hvorpå virksomheder laver prototyper med RISC-V i dag," siger Mark Himelstein, CTO for RISC-V International. “Disse spænder fra enkeltkortcomputere på producentniveau til LINUX-kompatible kort til virksomheder. Emuleringsmiljøer (som QEMU) giver udviklere mulighed for at udvikle sig med software, før deres hardware er færdig, og der er hyldevaredele overalt fra indlejrede SoC'er (fra virksomheder som Espressif og Telink), til FPGA'er (fra virksomheder som Microsemi) til det kommende Horse Creek board fra Intel og SiFive."

Det kommer tilbage til afvejningen mellem ydeevne/nøjagtighed. "Fysiske prototyper kræver langt mere designindsats, fordi du forbinder og syntetiserer ægte RTL, men de leverer langt større nøjagtighed og gennemløb," siger Quadrics Roddy. "En fysisk prototype i et FPGA-system, hvad enten det er hjemmelavet eller fra de store EDA-virksomheder, kræver en indsats at bringe op. Men den kan køre en størrelsesorden hurtigere end en SystemC-model og flere størrelsesordener hurtigere end simulering på fuld gateniveau. Designteams vil typisk pivotere fra C-baserede modeller under IP-udvælgelsesprocessen til fysiske modeller til både verifikation af det faktiske design efter IP-valg og som en system-softwareudviklingsplatform."

Når du ved, hvilket funktionssæt du vil have i hardwaren, kan du se, om nogen allerede har skabt en løsning, der opfylder de fleste af dine behov. "Chancerne er, at med alle de leverandører derude, vil der være en kommerciel løsning, der vil have den type ting, du leder efter," siger Davidmann. "Men med RISC-V behøver du ikke at acceptere den løsning, som den er. En væsentlig del af værdien med RISC-V er friheden til at ændre den, modificere den og tilføje forskellige ting, som du ønsker."

Valg af implementering

Der er mange måder at implementere et sæt funktioner på, såsom antallet af pipeline-trin eller spekulative eksekveringsfunktioner. Hver vil have en anden afvejning mellem kraft, ydeevne og område. "ISA-smag, hvad enten det er RISC-V, Arm, Cadence's Xtensa, Synopsys' ARC, påvirker ikke rigtig modellering og prototyping-mål og -afvejninger," siger Roddy. "En systemarkitekt skal besvare spørgsmål om SoC-designmål uanset processormærket. På et teknisk niveau er RISC-V-vognen virkelig i en stabil position på markedet i forhold til værktøjsstøtte til modellering og ydeevneanalyse. Der er adskillige konkurrerende kerneleverandører, hver med forskellige implementeringer og processorfunktioner. Som en hovedsystem-CPU har den ikke en arms levetid, og derfor har færre økosystemaktører i EDA-verdenen bredt valideret, klar-til-brug-modelleringsunderstøttelse for hyldevare RISC-V-kerner fra sorten af RISC-V-leverandører. Som en konfigurerbar, modificerbar kerne halter RISC-V-verdenen i niveauet for instruktionssæt-automatisering, som Tensilica har brugt 25 år på at bygge. Således har RISC-V mindre modelleringsstøtte som en færdigbygget byggeklods og mindre automatisering til brug som platform for instruktionssæt-eksperimentering."

Men det er kun et aspekt af en implementering, der skal vurderes. Hvad er kvaliteten af det? Hvis du vil ændre det, hvordan genvaliderer du det så?

Ydeevne er den nemmeste af disse at vurdere. "Dette er ikke anderledes end at gå til en hvilken som helst traditionel processorleverandør," siger Davidmann. "De vil fortælle dig, at denne kerne giver dig så mange Dhrystones pr. watt, de vil give dig de typiske processoranalytiske data, som siger, at det er så hurtigt denne mikroarkitektur kører. De har alle disse data, og enhver, der licenserer en processorkerne, vil være bekendt med disse data og vil tale med dem og få den information. De vil sandsynligvis have mange valgbare muligheder i deres datablad, og de vil sige, 'Hvis du slår denne mulighed til, får du dette eller hint.' Du kan se det på databladet, på leverandørernes hjemmesider.”

På dette niveau har du sandsynligvis brug for cyklusnøjagtighed. "Jeg ser, at de fleste mennesker pumper det ind i en emulator og kører nok data igennem det til at træffe en rimelig beslutning," siger Schirrmeister. "Jeg kan ikke se, at det går op til virtuelle prototyper lige foreløbig. Nogle virksomheder taler om FPGA-prototyper, hvor du har din egen single board-løsning. Afhængigt af det spørgsmål, du skal besvare, kan du beslutte at konfigurere det, generere det og derefter pumpe det ind i en FPGA for at køre flere data igennem det med de relevante softwarerutiner ovenpå. Industrien har tilstrækkelig hurtige adgangsveje til emulatorer og prototyper til at gøre dette muligt. Det grundlæggende problem er, at du vil tage denne beslutning baseret på så nøjagtige data som du kan, men du har måske ikke de præcise data på det tidspunkt, hvor du vil træffe den beslutning."

Mange af disse prototyper skal omfatte mere end blot processoren. "Virtuelle platforme giver mulighed for at integrere med andre eksterne fysiske hardwarefunktioner, såsom hukommelse og sensorer, der fungerer i et virkeligt miljø," siger Microchips Narayanan. “Hybride systemer kan samle virtuelle platforme med fysiske prototyper til andre eksterne funktioner. FPGA-emulering og prototyping hjælper med at finde timing-relaterede fejl, såsom løbsforhold, da dette er mere cykluspræcis og eksterne funktioner kører med hastighed."

Verifikation

Fordi processordesign har været internt i lang tid, er der ikke noget offentligt verifikationsøkosystem til at bygge en processor, og funktionerne i RISC-V kræver en meget mere fleksibel verifikationsløsning, end der nogensinde har eksisteret tidligere. Skabelsen af dette er lige begyndt at ske.

"Der er industrimålinger som Dhrystones eller CoreMark, så folk kan sammenligne ydeevne," siger Davidmann. "Men hvordan kan du sammenligne verifikationskvalitet? Der skal være lige vilkår, så hver leverandør kan sige: 'Sådan gør vi det.' Vi har brug for nogle kvalitetsmålinger med verifikation at gøre."

Det er her, open source-bevægelsen kan hjælpe. "Hvis du ser på RISC-V-økosystemet, har du et stort antal meget erfarne processorudviklere," siger Schirrmeister. "Der er to yderpunkter. Den ene er, at jeg får en kerne fra en leverandør, og hvis det ikke virker, har du et problem med dem. På den anden ende har jeg total frihed og gør alting selv. En ligevægt er ved at udvikle sig et sted mellem disse to yderpunkter. Du får noget, hvor en vis mængde verifikation leveres af din leverandør, og så er udvidelserne dit eget ansvar."

Og det er her, metrics kommer ind i billedet. "ISA-kompatibilitet er kun det første trin i en stige fuld af kompleksitet, som kun få virksomheder har klatret op på," siger Dave Kelf, CEO for Breker Verification Systems. "Prototyping er muligvis den eneste måde til fuldt ud at sikre pålidelig processordrift, men at udnytte reelle arbejdsbelastninger til at drive disse prototyper ridser overfladen af reel processordækning. Dette er i modstrid med konkurrencebestræbelserne fra en åben ISA, der driver fremskyndet udvikling og tid til markedsproblemer."

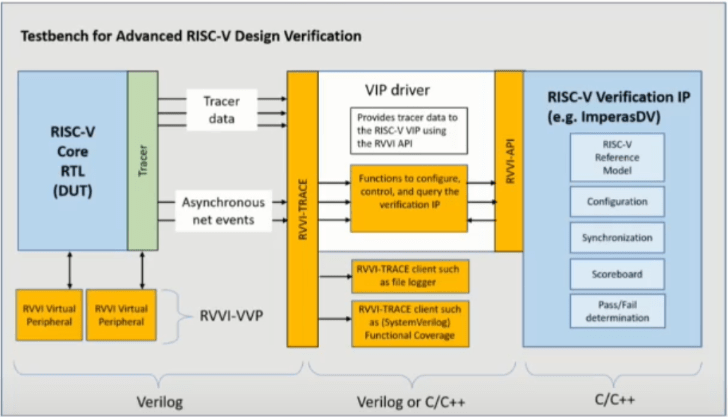

Men hvad er disse målinger? "I OpenHW-kvalitetsgruppen forsøger vi at finde ud af, hvad disse målinger skal være," siger Davidmann. “Det inkluderer ting som funktionel dækning, for det er ikke bare simple instruktioner. For en processor af høj kvalitet har du brug for meget mere end det. Du skal have en metode til verifikation, hvor der er tillid til, at dine sammenligninger med en reference dækker alt. Funktionel dækning viser bare, at du har testen, men det skal kombineres med en metode, der sammenligner med en form for kendt reference. Vi kommer til at tilføje fejlinjektionsteknologi, så det bliver muligt at finde ud af, om din testbænk faktisk opdager problemer.”

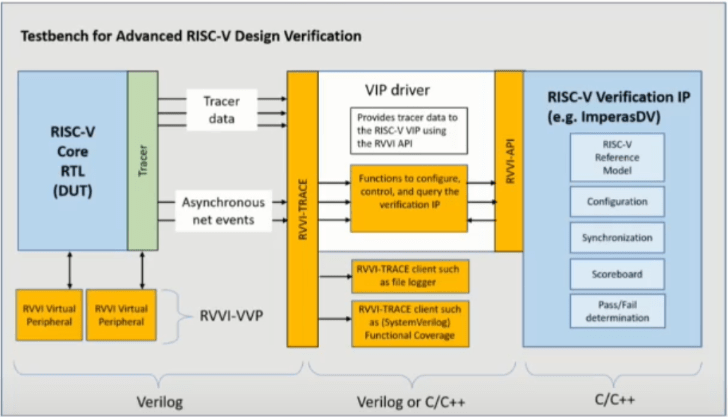

Fig. 1: Definition af arkitekturen for en RISC-V-verifikationsløsning. Kilde: Imperas

Det kræver en række værktøjer. "Efterhånden som RISC-V-økosystemet modnes, begynder kommercielle implementeringer at understøtte definerede markedssegmenter," siger Ashish Darbari, grundlægger og administrerende direktør for Axiomise. "Vi ser støtte til markeder, såsom bilindustrien, der kræver overholdelse af funktionel sikkerhed. Vi ser understøttelse af IoT, der kræver sikkerhed. RISC-V-leverandører investerer i avancerede verifikationsteknikker, herunder virtuel prototyping til arkitektonisk modellering og ydeevne. Værktøjer er nu tilgængelige til tidlig vedtagelse af formelle metoder til at beskære fejl tidligt i designprocessen og undgå fejlindsættelse, da designere kæmper for at fange hjørne-case-fejl med simulering på processor-hukommelsesgrænsefladen."

Et af de værktøjer, der vil være nødvendige, er evnen til at generere testcases baseret på en funktionsliste eller et sæt af muligheder. "Den automatiserede generering af testindhold til at drive prototyper, der tager højde for verifikationskompleksiteter i tide, er nøglen," siger Breker's Kelf. "Disse generationsmekanismer begynder nu at dukke op på markedet."

Konklusion

Et økosystem er kun så godt som dets svageste komponent, og for RISC-V er det EDA-værktøjskæden. Årsagerne til dette er todelte. For det første var der indtil for nylig ikke noget kommercielt marked for processorverifikationsværktøjer. Mens de eksisterede i fortiden, var de alle enten forsvundet eller blevet opløst i de gamle forarbejdningsvirksomheder. For det andet skaber fleksibiliteten af RISC-V ISA en ny optimeringstilgang på systemniveau, der kræver et nyt sæt værktøjer. Det tager tid for denne mulighed at blive forstået og for kommercielle værktøjer at dukke op, som adresserer den korrekt.

Relaterede

En minimal RISC-V

Er der plads til en endnu mindre version af en RISC-V-processor, der kunne erstatte 8-bit mikrocontrollere?

RISC-V skubber ind i hovedstrømmen

Open source-processorkerner begynder at dukke op i heterogene SoC'er og pakker.

Effektiv sporing i RISC-V

Sådan arbejder du med den nye RISC-V fejlretningsstandard.

Hvor sikre er RISC-V-chips?

Open source i sig selv garanterer ikke sikkerhed. Det kommer stadig ned til det grundlæggende i design.

- SEO Powered Content & PR Distribution. Bliv forstærket i dag.

- Platoblokkæde. Web3 Metaverse Intelligence. Viden forstærket. Adgang her.

- Kilde: https://semiengineering.com/selecting-the-right-risc-v-core/

- 1

- 10

- a

- evne

- I stand

- Om

- over

- accelereret

- acceleratorer

- Acceptere

- acceptabel

- Konto

- nøjagtighed

- præcis

- faktisk

- adresse

- Vedtagelse

- fremskreden

- Efter

- mod

- algoritme

- Alle

- allerede

- beløb

- analyse

- Analytisk

- ,

- og infrastruktur

- besvare

- vises

- Anvendelse

- tilgang

- passende

- Arc

- arkitektonisk

- arkitektur

- OMRÅDE

- ARM

- udseende

- vurderes

- Automatiseret

- Automation

- automotive

- til rådighed

- gennemsnit

- tilbage

- båndbredde

- baseret

- grundlæggende

- fordi

- bliver

- blive

- før

- Begyndelse

- være

- gavner det dig

- BEDSTE

- mellem

- Beyond

- Big

- Bit

- Bloker

- board

- brand

- bringe

- bredt

- Bug

- bugs

- bygge

- Bygning

- bygget

- virksomhed

- forretningsudvikling

- CAD

- kapaciteter

- stand

- brydning

- Direktør

- vis

- udfordre

- udfordringer

- odds

- lave om

- Chips

- valg

- valg

- Vælg

- klatrede

- CMO

- Collateral

- Kom

- kommerciel

- kommercielt

- Fælles

- Virksomheder

- sammenligne

- kompatibilitet

- konkurrerende

- konkurrencedygtig

- fuldføre

- kompleksiteter

- Compliance

- komponent

- komponenter

- computere

- Bekymringer

- betingelser

- tillid

- Konfiguration

- Tilslutning

- overvejelser

- indhold

- Core

- kunne

- koblede

- dækning

- dækker

- CPU

- oprettet

- skaber

- Oprettelse af

- skabelse

- Creek

- CTO

- For øjeblikket

- data

- Dave

- beslutning

- definere

- levere

- krav

- Afdeling

- Afhængigt

- indsat

- Design

- designproces

- designere

- udvikle

- udviklet

- udviklere

- udvikling

- Udvikling

- Enheder

- forskellige

- svært

- Direktør

- Er ikke

- Dont

- ned

- køre

- drevet

- kørsel

- i løbet af

- hver

- Tidligt

- nemmeste

- økosystem

- økosystemer

- indsats

- indsats

- enten

- indlejret

- muliggør

- Engine (Motor)

- Engineering

- Motorer

- nok

- sikre

- sikring

- Enterprise

- Hele

- indrejse

- Miljø

- miljøer

- Lig

- Equilibrium

- etableret

- skøn

- evaluere

- Endog

- NOGENSINDE

- at alt

- udførelse

- erfarne

- strækker

- udvidelse

- udvidelser

- ekstern

- ekstremer

- Ansigtet

- bekendt

- Mode

- FAST

- hurtigere

- Feature

- Funktionalitet

- få

- felt

- Fig

- Finde

- finde

- Fornavn

- passer

- fast

- Fleksibilitet

- fleksibel

- formular

- formel

- grundlægger

- Stifter og CEO

- FPGA

- Frihed

- fra

- fuld

- fuldt ud

- funktion

- funktionel

- funktioner

- Fundamentals

- generelt

- generere

- generere

- generation

- få

- få

- Giv

- giver

- Go

- Mål

- gå

- godt

- større

- gruppe

- Dyrkning

- garanti

- ske

- Hardware

- hjælpe

- hjælper

- høj kvalitet

- hjemmeavlede

- hest

- Hvordan

- HTTPS

- kæmpe

- KIMOs Succeshistorier

- gennemføre

- implementering

- in

- omfatter

- omfatter

- Herunder

- stigende

- stigende

- industrien

- oplysninger

- Infrastruktur

- anvisninger

- integrere

- Intel

- interesseret

- grænseflade

- internationalt

- investere

- involverede

- tingenes internet

- IP

- spørgsmål

- IT

- selv

- Job

- Nøgle

- Venlig

- Kend

- kendt

- stigen

- stor

- Legacy

- Niveau

- niveauer

- løftestang

- Licenser

- Sandsynlig

- linux

- Liste

- Lang

- lang tid

- levetid

- Se

- leder

- lavet

- Main

- lave

- maker

- maerker

- mange

- markere

- Marked

- Markeder

- modnes

- max-bredde

- Mød

- Hukommelse

- Metode

- metoder

- Metrics

- mindste

- model

- modellering

- modeller

- ændre

- mere

- mest

- bevægelse

- flytning

- nødvendig

- Behov

- behov

- Ny

- nummer

- talrige

- objektiv

- Odds

- tilbud

- ONE

- åbent

- open source

- drift

- drift

- Opportunity

- optimering

- Option

- Indstillinger

- ordrer

- ordrer

- Andet

- egen

- pakker

- del

- dele

- forbi

- Peak

- Mennesker

- ydeevne

- fysisk

- pipeline

- Pivot

- perron

- Platforme

- plato

- Platon Data Intelligence

- PlatoData

- spillere

- spiller

- Punkt

- Synspunkt

- position

- muligheder

- mulig

- magt

- præsident

- sandsynligvis

- Problem

- problemer

- behandle

- Processor

- processorer

- Progress

- korrekt

- prototype

- prototyper

- prototyping

- give

- forudsat

- udbyder

- offentlige

- pumpe

- pumpning

- formål

- formål

- kvalitet

- spørgsmål

- Spørgsmål

- Løb

- rækkevidde

- færdiglavet

- ægte

- virkelige verden

- grund

- rimelige

- årsager

- for nylig

- Uanset

- pålidelig

- erstatte

- kræver

- påkrævet

- krav

- Krav

- Kræver

- ansvar

- Værelse

- Kør

- kører

- Sikkerhed

- Sikkerhed og sikkerhed

- Anden

- sikker

- sikkerhed

- segmenter

- valgt

- udvælgelse

- valg

- senior

- sensorer

- sæt

- flere

- bør

- Vis

- Shows

- signifikant

- Simon

- Simpelt

- simulation

- enkelt

- langsomt

- mindre

- So

- Software

- softwareudvikling

- løsninger

- Løsninger

- nogle

- Nogen

- noget

- et eller andet sted

- Snart

- Kilde

- hastighed

- brugt

- Spin

- stabil

- etaper

- standard

- Starter

- Steve

- Stadig

- Kamp

- sådan

- suite

- support

- overflade

- systemet

- Systemer

- Tag

- tager

- Tal

- taler

- hold

- Teknisk

- teknikker

- Teknologier

- skabelon

- prøve

- deres

- derfor

- ting

- ting

- tre

- Gennem

- kapacitet

- tid

- tidskrævende

- gange

- timing

- til

- i dag

- sammen

- også

- værktøjer

- top

- I alt

- spore

- traditionelle

- TUR

- typisk

- typisk

- forstået

- enhed

- kommende

- brug

- Bruger

- brugere

- valideret

- validering

- værdi

- række

- sælger

- leverandører

- Verifikation

- udgave

- levedygtig

- Vice President

- Specifikation

- Virtual

- virtuelle platforme

- ønsker

- måder

- websites

- Hvad

- Hvad er

- hvorvidt

- som

- mens

- vilje

- inden for

- Arbejde

- træning

- world

- ville

- Forkert

- X

- år

- Din

- zephyrnet