Et nyt teknisk papir med titlen "Non-Traditional Design of Dynamic Logics using FDSOI for Ultra-Efficient Computing" blev udgivet af forskere ved University of Stuttgart, UC Berkeley, Indian Institute of Technology Kanpur og TU München, med finansiering fra den tyske forskningsfond .

Abstrakt

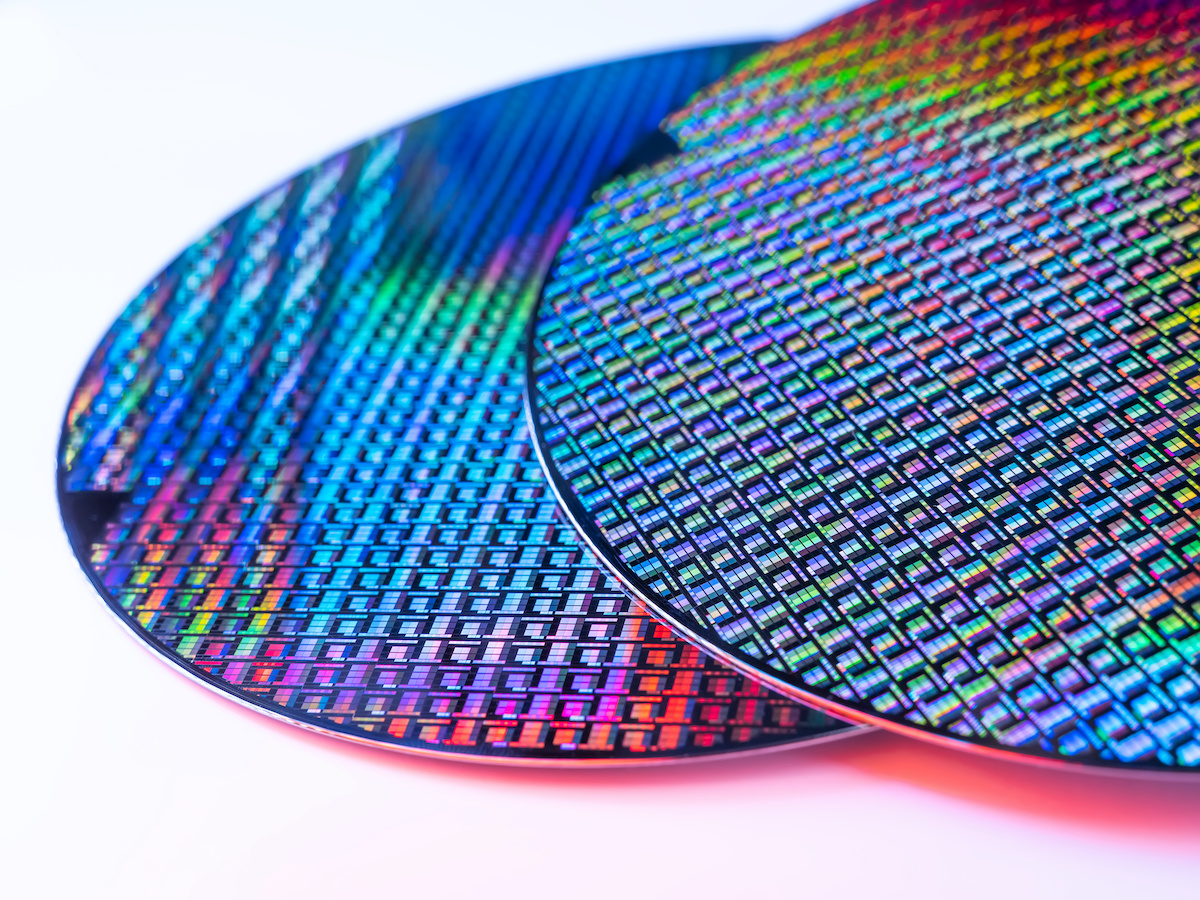

"I dette papir foreslår vi et ikke-traditionelt design af dynamiske logiske kredsløb, der bruger fuldt udtømt silicium på isolator (FDSOI) FET'er. FDSOI FET tillader tærskelspændingen (Vt ) for at være justerbar (dvs. lav-Vt- og høj-Vt-tilstande) ved at bruge back gate bias. Vores design bruger front- og bagportene på en FDSOI FET som inputterminaler og foreslår de dynamiske logiske porte (som; NAND, NOR, AND, OR, XOR og XNOR) og kredsløb (som; halv adder og fuld adderer). Det kræver færre transistorer at bygge dynamiske logiske porte og opnår høj ydeevne med lavt effekttab sammenlignet med konventionelle dynamiske logiske designs. Den kompakte industrielle model af FDSOI FET (BSIM-IMG) er blevet brugt til at simulere dynamiske logiske porte og er fuldt kalibreret til at reproducere 14nm FDSOI FET teknologi node data. Kalibrering udføres for både elektriske egenskaber og procesvariationer. Simuleringsresultaterne viser en gennemsnitlig forbedring i transistorantal, udbredelsesforsinkelse, effekt og effektforsinkelsesprodukt på henholdsvis 23.43 %, 57.16 %, 47.05 % og 77.29 % sammenlignet med de konventionelle designs. Yderligere reducerer vores design ladningsdelingseffekten, hvilket påvirker køreegenskaberne af de dynamiske logiske porte. Derudover har vi analyseret virkningen af processen, forsyningsspænding og belastningskapacitansvariationer på udbredelsesforsinkelsen af den dynamiske logikfamilie i detaljer. Resultaterne viser, at disse variationer har en mindre indvirkning på udbredelsesforsinkelsen af de foreslåede FDSOI-baserede dynamiske logiske porte sammenlignet med de konventionelle dynamiske logiske porte."

Find teknisk papir her. Udgivet april 2023.

S. Kumar, S. Chatterjee, CK Dabhi, YS Chauhan og H. Amrouch, "Non-Traditional Design of Dynamic Logics using FDSOI for Ultra-Efficient Computing," i IEEE Journal on Exploratory Solid-State Computational Devices and Circuits, doi: 10.1109/JXCDC.2023.3269141. Åbn Accesss.

- SEO Powered Content & PR Distribution. Bliv forstærket i dag.

- PlatoAiStream. Web3 Data Intelligence. Viden forstærket. Adgang her.

- Udmøntning af fremtiden med Adryenn Ashley. Adgang her.

- Køb og sælg aktier i PRE-IPO-virksomheder med PREIPO®. Adgang her.

- Kilde: https://semiengineering.com/non-traditional-design-of-dynamic-logic-gates-and-circuits-with-fdsoi-fets/

- :har

- :er

- 10

- 2023

- 23

- 77

- a

- opnår

- Desuden

- justerbar

- tillader

- an

- ,

- april

- AS

- At

- gennemsnit

- tilbage

- BE

- været

- Berkeley

- skævhed

- både

- bygge

- by

- karakteristika

- afgift

- sammenlignet

- computing

- konventionelle

- data

- forsinkelse

- Design

- designs

- detail

- Enheder

- dynamisk

- e

- effekt

- familie

- FET

- færre

- Til

- Foundation

- forsiden

- fuld

- fuldt ud

- finansiering

- yderligere

- Gates

- Tysk

- Halvdelen

- Have

- Høj

- HTTPS

- i

- IEEE

- KIMOs Succeshistorier

- in

- indiske

- industrielle

- indgang

- Institut

- IT

- tidsskrift

- ligesom

- belastning

- logik

- Lav

- mindre

- model

- München

- Ny

- node

- of

- on

- or

- vores

- Papir

- ydeevne

- plato

- Platon Data Intelligence

- PlatoData

- magt

- behandle

- Produkt

- foreslå

- foreslog

- foreslår

- offentliggjort

- reducerer

- Kræver

- forskning

- forskere

- henholdsvis

- Resultater

- s

- deling

- Vis

- Silicon

- simulation

- Stater

- forsyne

- Teknisk

- Teknologier

- at

- Disse

- denne

- tærskel

- titlen

- til

- universitet

- anvendte

- ved brug af

- udnytter

- Spænding

- var

- we

- som

- med

- zephyrnet