Fuzzing er til softwareverifikation, hvad randomisering er hardwareverifikation. Kan en uklar tilgang forbedre hardwaresikkerhedstestning? Paul Cunningham (GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, iværksætter, tidligere Synopsys CTO) og jeg fortsætter vores serie om forskningsidéer. Som altid er feedback velkommen.

Innovation

Denne måneds valg er HyperFuzzing til SoC-sikkerhedsvalidering. Forfatterne præsenterede dette papir på ICCAD 2020. De er fra IIT Kanpur.

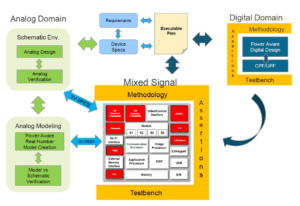

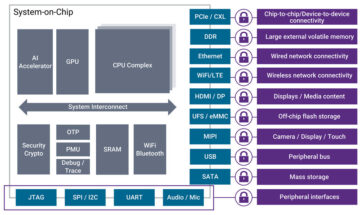

Dette er en spændende tilgang til fuzzing, tilpasset specifikt til moderne SoC-design. Det bygger på hyper-ejendom indtjekning af dynamiske simuleringer. Disse hyperegenskaber ræsonnerer om adfærd over sæt spor, en tilgang, der er velegnet til sikkerhedskontrol. Forfatterne tilbyder som eksempler informationsflowtjek (privilegerede data kan f.eks. ikke lække fra A til B) og ikke-interferenstjek (modstridende handlinger må ikke forstyrre beregningsflowet). Sikkerheden kontrolleres derefter ved at sammenligne bundter af simuleringsspor med og uden manipulation.

Ændring i denne tilgang kan modellere forskellige typer sårbarheder til upålidelige kilder. Ved at randomisere firmware-instruktioner, skriv instruktioner fra en komponent til NoC eller bit-flips i en hukommelse. Forfatterne foreslår også flere nye dækningsmålinger. Disse er designet til at guide iterationer til manipulation omkring sager, der er mest påvirket af tidligere manipulationskørsel.

Deres testcase er en lille, men repræsentativ SoC (detaljer i GitHub) kører firmwaretest mod kryptografiske blokke, kontrollerer for ikke-interferens og andre sårbarheder. De kører også sikker opstart med datablokkontrol. De fandt flere sikkerhedsbrud i kryptoblokkene, undtagen hvor blokering inkluderer ECC-beskyttelse.

Pauls syn

Sikkerhedsverifikation er et så vigtigt emne, og der er meget arbejde i gang her både i den akademiske verden og i industrien. Dette papir samler på en fin måde randomiseret mutationsbaseret dækning med "hyperegenskaber" over sæt af simuleringsspor for at skabe en innovativ løsning, der er både skalerbar og effektiv til at demonstrere sikkerhedsfejl.

Nogle sikkerhedsegenskaber kan formelt kun defineres over et sæt simuleringsspor. For eksempel betyder "ikke-interferens", at en hacker ikke kan forstyrre visse beskyttede beregninger i et design. For at demonstrere interferens skal du sammenligne to spor, identiske i inputstimulus bortset fra tilstedeværelsen af nogle angriberhandlinger i ét spor. Hvis nogen beskyttede beregninger i det angrebne spor adskiller sig fra dem i det gyldne spor, så har der været interferens.

Forfatterne skaber deres egen specielle smag af sprog til påstande over flere spor og bruger det til at formulere sikkerhedsegenskaber for ikke-interferens og fortrolighed. De bygger et brugerdefineret flow til tilfældigt at manipulere med simuleringer og kontrollere deres sikkerhedsegenskaber mellem manipulerede og ikke-manipulerede simuleringer. Deres tilfældige manipulationsalgoritme har også en elegant dækningsbaseret læringsheuristik til at guide den til mere effektivt at finde sikkerhedsfejl.

Ideen med påstande over flere simuleringer er meget kraftfuld. Jeg spekulerer på, om det ville være muligt rent at udvide SystemVerilog til at understøtte denne slags påstande. Dette kunne åbne døren til nogle overbevisende native udvidelser til kommerciel simulering og formelle værktøjer. En anden mulighed kunne være at udvide den nye Portable Stimulus Standard (PSS) til at omfatte påstande, der spænder over flere genererede tests.

Dette papir er let og behageligt at læse, selvom jeg ønsker nogle flere detaljer om resultaterne. Forfatterne hævder, at deres løsning finder sikkerhedshuller i deres open source SoC-testcase, men der er ingen detaljer om, hvad disse huller er, eller hvordan deres tilgang sammenlignes med andre tilgange i litteraturen, der kunne anvendes til at finde de samme huller.

Raúls syn

Jeg vil først se på dette fra en teknologisk modenhedsvinkel. Jeg kan godt lide ideen generelt, en meget interessant tilgang til at vurdere sikkerhed i et design. Når det er sagt, kræver hvert design, at designere leverer frøtest, manipulationer og sikkerhedsspecifikationer i et nyt påstandssprog. For mig binder dette tilgangen stærkt til det akademiske domæne for nu. Fantastisk til afhandlinger og papirer, endnu ikke i nærheden af noget, der kunne tage springet til kommerciel anvendelse.

Jeg tager min investorhat på til den anden udfordring. Sikkerhed er et vigtigt emne, ingen tvivl. Men uden for nogle få domæner kender vi allerede – for eksempel rumfart, forsvar, betalingssystemer og processorer/servere. Det er stadig ikke et eksistentielt problem for de fleste OEM'er og komponentbyggere. De er villige til at markere en boks, hvis det generelt forventes. Men kun hvis indvirkningen på omkostninger eller time to market er lille. Fordi deres kunder generelt ikke betaler mere for sikkerheden. Hvilket efterlader sikkerhed for de fleste markeder stadig afhængig af nøglefærdig IP, såsom hardware roots of trust og brugervenlige apps. Løsninger pakket på en af disse måder vil kunne investeres, ellers ikke så meget.

Min udsigt

Paul og Raúl dækkede det meste af det, jeg kunne have foreslået. Jeg kan godt lide Pauls idé om at udvide SVA, i det mindste for at tilskynde til eksperimenter med hyperegenskaber. Dette skal åbne en ny klasse af interessante tests, der i sidste ende fører til nye bundtede verifikationsmetoder.

Del dette opslag via: Kilde: https://semiwiki.com/eda/299391-fuzzing-to-validate-soc-security-innovation-in-verification/

- 100

- 2020

- 2021

- Luftfart

- algoritme

- Anvendelse

- apps

- omkring

- forfattere

- Bit

- Boks

- bygge

- kadence

- tilfælde

- udfordre

- kontrol

- Kontrol

- kommerciel

- komponent

- fortsæt

- krypto

- CTO

- Kunder

- data

- Forsvar

- Design

- Domæner

- Effektiv

- Entrepreneur

- udvidelser

- fund

- Fornavn

- fejl

- flow

- Generelt

- GM

- stor

- vejlede

- Hardware

- link.

- Hvordan

- HTTPS

- idé

- IEEE

- billede

- KIMOs Succeshistorier

- industrien

- oplysninger

- Innovation

- investor

- IP

- IT

- hoppe

- Sprog

- førende

- lække

- læring

- litteratur

- Marked

- Markeder

- Metrics

- model

- tilbyde

- åbent

- Andet

- Papir

- Betal

- betaling

- Betalingssystemer

- foreslå

- beskyttelse

- Tilfældigt

- forskning

- Resultater

- Kør

- kører

- sikkerhed

- sikkerhedstest

- frø

- Series

- sæt

- simulation

- lille

- So

- Software

- Løsninger

- stimulus

- support

- Systemer

- Teknologier

- Test

- tests

- tid

- Stol

- Verifikation

- Sårbarheder

- Arbejde