Multi-die-systemer er opbygget af flere specialiserede funktionelle dies (eller chiplets), der er samlet i samme pakke for at skabe det komplette system. Multi-die-systemer er for nylig dukket op som en løsning til at overvinde opbremsningen af Moores lov ved at give en vej til at skalere funktionaliteten i den pakkede chip på en måde, der kan fremstilles med godt udbytte.

Derudover muliggør multi-die-systemer produkt-SKU-fleksibilitet med hensyn til ydeevneskalering for at matche behovene i forskellige markedssegmenter, optimering af procesknudepunktet pr. funktion ved at blande og matche forskellige procesknudepunkter i samme produkt, hurtigere time to market og lavere risiko.

For at muliggøre højere die-to-die routingtæthed og understøtte højere båndbreddetrafik mellem dies, har pakketeknologi udviklet sig til at skabe nye, avancerede pakker, baseret på silicium interposers (med TSV'er) eller siliciumbroer og, for nyligt, redistribution layers (RDL) , fanouts og HD-substrater.

Et nøgleaspekt for succesen af multi-die-systemer er evnen til at sikre testbarhed af systemet i forskellige faser af fremstilling og montering, samt at sikre pålidelig drift i marken. Ved at bruge ekstra monteringstrin og mere komplekse stød- og emballeringsteknologier kræver multi-die-systemer test- og pålidelighedsprocedurer, der går ud over, hvad der var state-of-the-art for monolitiske designs.

De nøgne matricer, og selve pakken, bør testes på forhånd for at sikre, at alle defekte matricer eller pakker opdages, før de samles i en pakke. Hvis en defekt matrice først opdages efter montering, skal hele multi-matrice-systemet skrottes med alvorlig indvirkning på omkostningerne. Processen med at teste nøgne matricer kaldes Known Good Die (KGD) test.

Selve monteringsprocessen varierer med den valgte emballageteknologi. For eksempel tillader chip-first-teknologier, hvor matricer placeres først, og sammenkobling er bygget oven på dem, ikke "kendt-god-pakke"-testning, hvilket potentielt kan resultere i skrotning af gode dies, hvis sammenkoblingen er defekt. På den anden side, i chip-last teknologier, hvor sammenkoblingen er bygget separat, og matricer er samlet oven på den, muliggør prætestning af pakken før samling, hvilket reducerer sandsynligheden for, at gode matricer bliver skrottet.

Multi-die system testbarhed løsning kan opdeles i flere aspekter:

- Test dækning af individuelle blokke i matricen

- Testdækning af de enkelte dies (nøgne dies)

- Test af det samlede system (med die-to-die dækning)

- Adgang til teststoffet i nøgne matricer

- Hierarkisk adgang til teststof efter montage

Denne artikel beskriver fordelene ved en omfattende testbarhedsløsning, der udnytter UCIe IP til at sikre multi-die-systempålidelighed.

DFT til UCIe-grænsefladen

En løsning med høj testdækning til UCIe-grænsefladen opnås ved at implementere omfattende testbarhedsfunktioner i UCIe IP'et for at udsende defekte dies i testfasen med nøgne matricer. Nogle af funktionerne omfatter:

- Scan kæder, der dækker alle syntetiserede digitale kredsløb

- Dedikeret blokspecifik BIST-funktionalitet

- Loopback indbygget selvtest (BIST) funktionalitet, der dækker hele signalkæden op til IO-pinden

- Programmerbare pseudorandom binære sekvenser (PRBS) og brugerdefinerede testmønstergeneratorer og brikker

- Fejlindsprøjtning for at eliminere falske gennemløb

Derudover kan funktionalitet til at udvide dækningen til dør-til-matrice-forbindelsen efter pakkesamling hjælpe med at opnå et højt niveau af testdækning, herunder:

- Fjernside (die-to-die) BIST loopback-funktionalitet

- Die-to-die link BIST

- 2D øjenmarginering til at analysere marginaliteter

- Pr. bane test og reparationsfunktionalitet

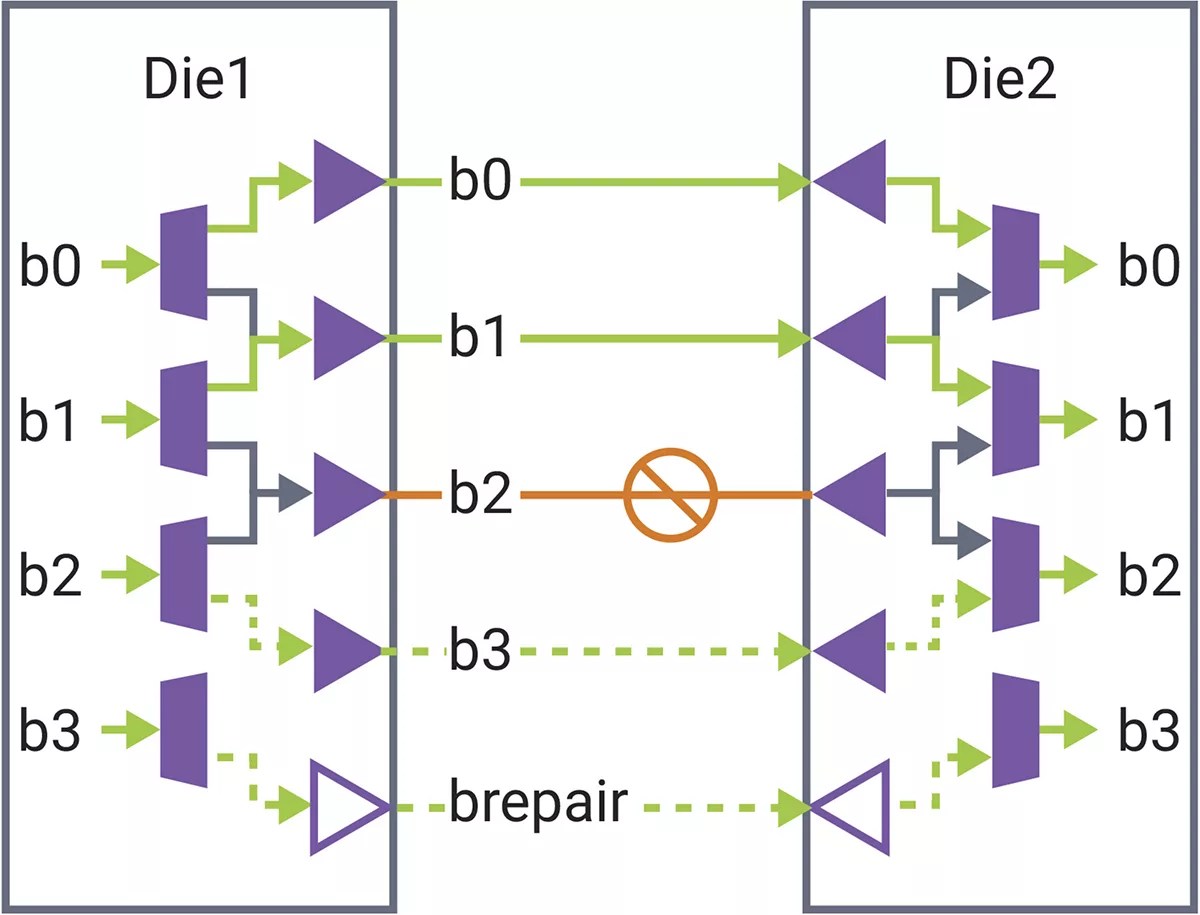

UCIe test og reparation

Avancerede pakker muliggør routing med høj tæthed med mikrobumping med fin pitch og routing på silicium- eller RDL-interposere. Under monteringsprocessen er nogle mikro-bump-forbindelser muligvis ikke godt dannet og kan gå i stykker. UCIe giver mulighed for at teste og reparere disse forbindelser efter montering på en måde, der genvinder det potentielle udbyttetab.

UCIe-test og reparation udføres under produktionstest og ved linkinitialisering. I testfasen kontrolleres hvert enkelt led for defekter ved lav hastighed. Defekte links repareres ved at omdirigere data til reservelinks, der er foruddefineret af UCIe-standarden.

UCIe-konfigurationer rettet mod avancerede pakker inkluderer op til 8 reserveben pr. retning (TX og RX) for at muliggøre reparation af alle de funktionelle links:

- Fire reservestifter til reparation af datastifter, 2 ben til hver gruppe på 32 datastifter

- En reservestift til ur og ure og sporstiftreparation

- Tre ekstra ben, hver til gyldig pin, sidebånd data pin og ur data pin reparation

Test- og reparationsudførelsen finder sted, når der ikke er nogen gyldig trafik på die-to-die-linket. Efter at reparationen er afsluttet, og linket er initialiseret, antages det at være godt, og at trafik kan passeres uden problemer. Den resulterende PHY-konfiguration, kaldet PHY-reparationssignaturen, er gemt i interne registre i begge ender af linket.

Nedbrydning på grund af ældning eller andet af mikrobump-karakteristika under drift kan påvirke linkets ydeevne. Dette vil blive detekteret på protokolniveau ved en stigning i bitfejlfrekvens (BER) eller værste af data, der går tabt. I så fald forventes forbindelsen at blive afbrudt og et nyt test- og reparationstrin udført.

Nogle applikationer har dog strenge krav med hensyn til kontinuitet i trafikken på die-to-die-forbindelsen - de kan ikke tolerere afbrydelse af trafikken under drift. I disse tilfælde tilføjer en testbarhedsløsning Signal Integrity Monitors (SIM) til hver UCIe-modtagerpin.

Fig. 1: Link reparation ved hjælp af indbyggede reserveled.

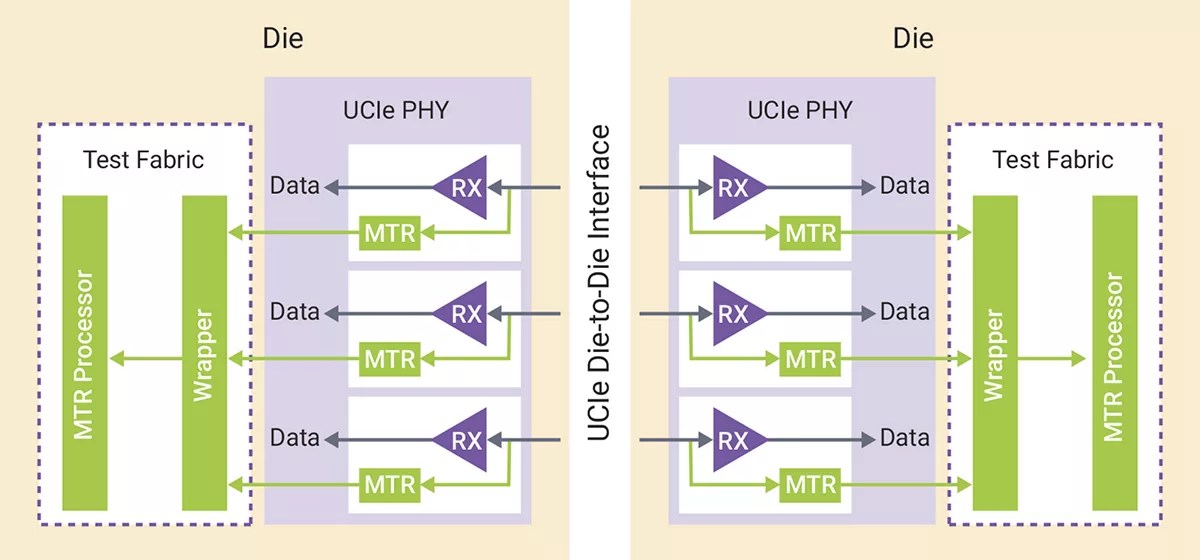

Signalintegritetsmonitorer

SIM-skærme er små blokke indlejret på modtageren. De registrerer konstant signalet på modtagerens ben under normal drift for at identificere variationer i signalegenskaberne, som kan påvirke linkets ydeevne eller indikere, at linket ikke længere er sundt og kan gå i stykker i den nærmeste fremtid.

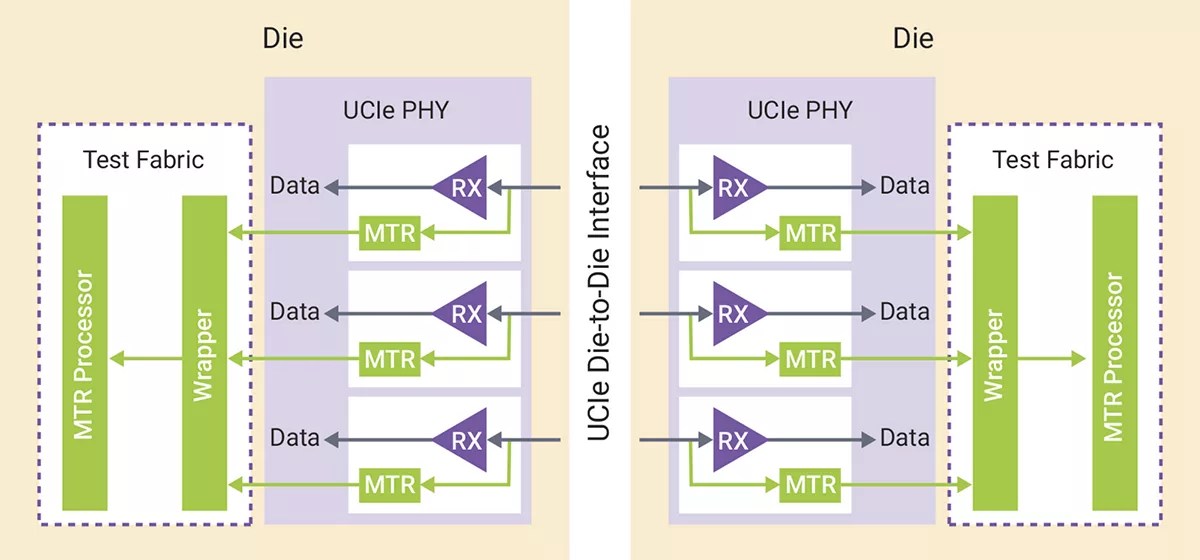

De data, der indsamles af de individuelle sensorer, indsamles i en overvågnings-, test- og reparationscontroller (MTR) uden for grænsefladen til videre behandling. Aggregering af data fra flere UCIe-links kan give øjeblikkelig indsigt i multi-die-systemets tilstand og muliggøre forudsigelig vedligeholdelse af links.

Hvis et specifikt link forudsiges at være i risiko for funktionsfejl gennem denne procedure, kan det deaktiveres og data omdirigeres til et af reservelinkene ved at udnytte UCIe PHY-reparationsmekanismen, selv uden trafikafbrydelse.

Fig. 2: Sundhedsovervågningsløsning til UCIe-links.

Accelererer vækningstid

Mens trafikmønsteret for de fleste die-to-die-brugerfladebrug, for eksempel ved serveropdeling eller -skalering, antages at være stabilt under drift, kan trafik i nogle tilfælde udvise en eksplosionsagtig adfærd. I sådanne tilfælde er det ønskeligt at bringe grænsefladen i en laveffekttilstand for at spare strøm, mens der ikke er trafik. Geninitialisering af link kan fremskyndes ved at undgå test- og reparationsprocessen og stole på UCIe PHY-reparationssignaturen, der blev oprettet under den tidligere PHY-initialisering.

Dette koncept kan udvides yderligere til situationer, hvor matricen er helt slukket. I disse tilfælde hentes PHY-reparationssignaturen fra PHY'en og gemmes på en permanent hukommelse på matricen (eFuse eller flash). Hukommelsen kan muligvis lagre flere signaturer, der dækker forskellige anvendelsestilfælde eller betingelser, hvilket muliggør yderligere brugerfleksibilitet.

Accelererer matricetestning med UCIe

Testtid er en dyr vare. Det er muligt at fremskynde testtiden ved at opdele teststrategien hierarkisk for at køre test af forskellige matricer parallelt. Hierarkiet kan udvides på tværs af flere matricer i et multi-die-system ved at forbinde testinfrastrukturen for de to dies hierarkisk. En sådan tilgang giver adgang til alle matricerne i multi-matrice-systemet fra en enkelt JTAG (eller lignende) testgrænseflade i hovedmatricen.

Ofte er begrænsningen af testtiden tiden til at indlæse eller læse testvektorerne i matricerne. JTAG-grænseflader kan blive en hastighedsflaskehals. For at overvinde denne begrænsning kan designere bruge eksisterende højhastighedsgrænseflader såsom PCI Express (PCIe) eller USB osv. som grænseflader til testudstyret. Testvektorer og kommandoer pakkes til denne grænseflade og afpakkes på matricen under produktionstestfasen.

Mange dyser har ikke en højhastighedsgrænseflade, dog kan UCIe die-to-die-grænsefladen bruges under test til at transportere store testvektorer og kommandoer mellem dyser ved høj hastighed. UCI-die-to-die-grænsefladen udvider højhastigheds-DFT-adgangen på tværs af hele multi-die-systemet uden at øge antallet af ben, hvilket er særligt vigtigt for IO og områdebegrænsede dies.

Resumé

Udover UCIe die-to-die-grænsefladen, er fællesnævneren, der muliggør alle disse test- og pålidelighedsforbedringsfunktioner, et test-, reparations- og overvågningsstof, der kan forbinde alle de interne blokke. Test-, reparations- og overvågningsstoffet spænder over de forskellige matricer i multi-die-systemet, hvilket giver en struktureret hierarkisk infrastruktur, der opnår følgende vigtige funktioner:

- Styrer testningen af de enkelte matricer i multi-die systemet

- Optimerer testplanlægning for at reducere testtid

- Understøtter højhastighedstestadgang på tværs af matricerne via UCIe-grænsefladen

- Indsamler information fra sundhedsovervågningsgrænseflader, der er indlejret i UCIe-grænsefladen og muliggør yderligere behandling på systemniveau

- Styrer lagringen af PHY reparationssignaturen i en ikke-flygtig hukommelse

- Og mere

Synopsys leverer en omfattende og skalerbar multi-die-systemløsning, inklusive EDA og IP, til hurtig heterogen integration. For en sikker og pålidelig die-to-die-forbindelse tilbyder Synopsys en komplet UCIe Controller, PHY og Verification IP-løsning. Som en del af Synopsys SLM & Test Family er en komplet UCIe Monitoring, Test and Repair (MTR) løsning tilgængelig sammen med STAR Hierarchical System (SHS) løsning. MTR-løsningen inkluderer signalintegritetsmonitor til måling af signalkvalitet på UCIe-banerne, BIST til selvtest og reparationslogik til redundant vognbaneallokering, mens SHS-løsningen fungerer som forbindelsesstrukturen, der understøtter industristandarden IEEE 1687, IEEE 1149.1 og IEEE 1838 grænseflader. Denne komplette løsning muliggør effektiv og omkostningseffektiv sundhedsovervågning af UCIe i alle faser af siliciums livscyklus, hvilket er afgørende for pålidelig drift af multi-die-systemer.

Ressourcer:

- SEO Powered Content & PR Distribution. Bliv forstærket i dag.

- PlatoAiStream. Web3 Data Intelligence. Viden forstærket. Adgang her.

- Udmøntning af fremtiden med Adryenn Ashley. Adgang her.

- Køb og sælg aktier i PRE-IPO-virksomheder med PREIPO®. Adgang her.

- Kilde: https://semiengineering.com/from-known-good-die-to-known-good-system-with-ucie-ip/

- :har

- :er

- :ikke

- :hvor

- $OP

- 1

- 8

- a

- evne

- fremskynde

- accelereret

- adgang

- opnå

- opnået

- opnår

- tværs

- Desuden

- Yderligere

- Tilføjer

- fremskreden

- Efter

- Aging

- Alle

- allokering

- tillade

- tillader

- sammen

- an

- analysere

- ,

- applikationer

- tilgang

- ER

- artikel

- AS

- udseende

- aspekter

- samlet

- Assembly

- antaget

- At

- til rådighed

- undgå

- båndbredde

- baseret

- BE

- bliver

- før

- være

- fordele

- mellem

- Beyond

- Bloker

- Blocks

- både

- Pause

- broer

- bringe

- bygget

- indbygget

- by

- kaldet

- CAN

- kan ikke

- tilfælde

- tilfælde

- kæde

- kæder

- karakteristika

- afkrydset

- chip

- ur

- Ure

- råvare

- Fælles

- fuldføre

- fuldstændig

- komplekse

- omfattende

- Konceptet

- betingelser

- Konfiguration

- Tilslut

- Tilslutning

- Tilslutninger

- Connectivity

- konstant

- controller

- Koste

- omkostningseffektiv

- kunne

- dækning

- dækker

- skabe

- oprettet

- kritisk

- data

- definerede

- tæthed

- designere

- designs

- opdaget

- Die

- forskellige

- digital

- retning

- deaktiveret

- Divided

- do

- ned

- grund

- i løbet af

- hver

- effektiv

- eliminere

- indlejret

- opstået

- muliggøre

- muliggør

- muliggør

- ender

- ekstraudstyr

- sikre

- sikring

- udstyr

- etc.

- Ether (ETH)

- Endog

- udviklet sig

- eksempel

- udførelse

- udstille

- eksisterende

- forventet

- dyrt

- Express

- udvide

- omfattende

- ekstra

- øje

- stof

- falsk

- familie

- FAST

- hurtigere

- defekt

- Funktionalitet

- felt

- ende

- Fornavn

- Blink

- Fleksibilitet

- efter

- Til

- dannet

- fra

- funktion

- funktionel

- funktionalitet

- funktioner

- yderligere

- fremtiden

- indsamlede

- generatorer

- Go

- godt

- gruppe

- hånd

- Have

- Helse

- sund

- hjælpe

- hierarki

- Høj

- højere

- Men

- HTTPS

- identificere

- IEEE

- if

- KIMOs Succeshistorier

- gennemføre

- vigtigt

- in

- omfatter

- omfatter

- Herunder

- Forøg

- stigende

- angiver

- individuel

- industrien

- oplysninger

- Infrastruktur

- indsigt

- øjeblikkelig

- integration

- integritet

- grænseflade

- grænseflader

- interne

- afbrudt

- ind

- IP

- IT

- selv

- Nøgle

- kendt

- Lane

- stor

- Lov

- lag

- Niveau

- Udnytter

- løftestang

- livscyklus

- begrænsning

- LINK

- links

- belastning

- logik

- længere

- off

- tabte

- Lav

- lavet

- Main

- vedligeholdelse

- Marked

- Match

- matchende

- max-bredde

- Kan..

- måling

- mekanisme

- Hukommelse

- tilstand

- Overvåg

- overvågning

- skærme

- Monolithic

- mere

- mest

- MTR

- flere

- skal

- I nærheden af

- behov

- Ny

- ingen

- node

- noder

- normal

- nummer

- of

- Tilbud

- on

- ONE

- kun

- drift

- optimering

- or

- Andet

- ud

- uden for

- Overvind

- pakke

- emballeret

- pakker

- emballage

- Parallel

- del

- især

- Bestået

- sti

- Mønster

- mønstre

- ydeevne

- permanent

- fase

- fyr

- Pitch

- plato

- Platon Data Intelligence

- PlatoData

- mulig

- eventuelt

- potentiale

- potentielt

- magt

- strøm

- forudsagde

- tidligere

- Forud

- sandsynlighed

- problemer

- procedurer

- behandle

- forarbejdning

- Produkt

- produktion

- protokol

- give

- giver

- leverer

- kvalitet

- Sats

- Læs

- for nylig

- Genopretter

- reducere

- reducere

- registre

- pålidelighed

- pålidelig

- reparere

- kræver

- Krav

- resulterer

- Risiko

- routing

- Kør

- RX

- samme

- Gem

- skalerbar

- skalering

- planlægning

- sikker

- segmenter

- valgt

- sensorer

- Sequence

- alvorlig

- tjener

- flere

- bør

- side

- Signal

- Underskrifter

- Silicon

- JA

- lignende

- enkelt

- situationer

- langsom

- langsommere

- lille

- løsninger

- nogle

- spændvidder

- specialiserede

- specifikke

- hastighed

- stabil

- standard

- Stjerne

- state-of-the-art

- Trin

- Steps

- opbevaring

- butik

- opbevaret

- Strategi

- struktureret

- succes

- sådan

- support

- Støtte

- systemet

- Systemer

- rettet mod

- Teknologier

- Teknologier

- vilkår

- prøve

- Test

- tests

- at

- Them

- derefter

- Der.

- Disse

- de

- denne

- Gennem

- tid

- til

- top

- spor

- Trafik

- transport

- to

- TX

- usb

- brug

- anvendte

- Bruger

- ved brug af

- forskellige

- Verifikation

- via

- var

- Vej..

- WebP

- GODT

- Hvad

- hvornår

- som

- mens

- vilje

- med

- inden for

- uden

- Værst

- Udbytte

- zephyrnet