Plasmaætsning er måske den mest essentielle proces i halvlederfremstilling og muligvis den mest komplekse af alle fab-operationer ved siden af fotolitografi. Næsten halvdelen af alle fantastiske trin er afhængige af et plasma, en energisk ioniseret gas, for at udføre deres arbejde.

På trods af stadigt krympende transistor- og hukommelsesceller fortsætter ingeniører med at levere pålidelige ætsningsprocesser.

"For på en bæredygtig måde at skabe chips med præcision på nanoskalaniveau og den rigtige omkostningsstruktur, er producenter af waferfabrikker nødt til at skubbe grænserne for plasmafysik, materialeteknik og datavidenskab for at levere de nødvendige udstyrsløsninger," siger Thomas Bondur, corporate vice president for Etch Product Group marketing hos Lam Research. Ingen steder er dette mere tydeligt end i plasmaætsning, som arbejder hånd i hånd med litografi for at skabe krævende, gentagelige funktioner på wafers.

Denne rapport undersøger vigtige ætsningstrin i 3D NAND, DRAM, nanosheet FET'er og sammenkoblinger med et fremadrettet blik på 2D-enheder og lavbudget-backend-behandling. Industrien forfølger også mere bæredygtig ætsningskemi for at reducere tilsvarende CO2 emissioner fra dets fabrikker.

For mange værktøjsmagere spiller procesmodellering en central rolle i udviklingen af etch-processer. Målet er at forkorte tiden til markedet og samtidig reducere omkostningerne til wafer og maske.

"Etch-procesoptimering på nogle af de vanskeligste trin kan tage et år eller mere at fuldføre," sagde Barrett Finch, senior marketingdirektør hos Lam Research. "Vi afsluttede for nylig noget processimuleringsarbejde på tre uger, som forventedes at tage tre måneder ved hjælp af typisk siliciumbaseret test og udvikling."

Dette kan beløbe sig til hundredtusindvis eller endda millioner af dollars, bare for maske- og waferomkostningerne for en enhedsproducent.

Grundlæggende om ætsning

Ætseprocessen arbejder hånd i hånd med litografi. Ætsning er typisk forudgået af aflejring af en film (ved epitaksi, kemisk eller fysisk dampaflejring osv.). Typisk, a CVD film er belagt med fotoresist og derefter eksponeret gennem en mønstret net (maske) ved hjælp af optisk litografi (248nm eller 193nm UV, 13.5nm EUV). Modstå udvikling afslører så mønsteret. I et plasmaætsekammer med enkelt wafer bombarderer og fjerner ætsekemikalierne og ionerne typisk CVD-filmen, hvor fotoresisten mangler (i positiv toneresist). Efter ætsning, modstå askning, våd kemisk rengøring og/eller vådætsning fjern rester.

Plasmaætsningsprocesser kan groft grupperes som dielektriske, silicium- eller lederætsninger. Dielektriske stoffer som siliciumdioxid og siliciumnitrid ætses bedst ved hjælp af fluorerede gasser, mens silicium- og metallag reagerer bedst med klorkemi. Der er i det væsentlige tre tørætsningstilstande - reaktiv ionætsning, plasmaætsning og sputterætsning (ionstråle). Ætsningsprocesser handler alle om de komplekse vekselvirkninger mellem de kemiske reaktanter, plasma og wafermaterialer. Når RF-bias påføres en reaktiv gas, bombarderer elektroner og positivt ladede ioner waferen for fysisk at fjerne (ætse) materiale, mens de kemiske arter og frie radikaler reagerer med det eksponerede materiale for at danne flygtige biprodukter. Ætsning kan enten være isotrop (reagerer lige lodret og vandret), anisotropisk (kun lodret) eller et sted midt imellem.

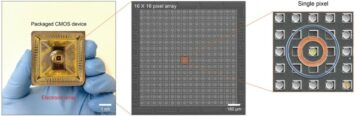

Fig. 1: Overgang fra finFET til GAA driver kritiske isotropiske selektive ætsningskrav. Kilde: Lam Research

De målinger, ætsningsingeniører bekymrer sig mest om, er ætsningshastighed, profilkontrol, ensartethed (på tværs af waferen) og ætseselektivitet, fordi disse påvirker udbytte og produktivitet. Ætseselektivitet er simpelthen forholdet mellem fjernelse af det materiale, du ønsker at ætse i forhold til dets underlag – for eksempel SiO2 på silicium. Under ætsning er det også fordelagtigt ikke at fjerne for meget fotoresist. Men når det er tilfældet, overføres ofte mønsteret til en hård maske (siliciumdioxid, siliciumnitrid, SiOC, TiN), før det overføres til den underliggende film.

Selektivitetsspecifikationerne varierer fra 2:1 til op til 1,000:1 (meget selektiv ætsning). Med hver ny node bliver disse specifikationer strammere. "Når EUV med høj NA begynder at erstatte almindelig EUV inden for de næste fire år, er fokus meget lavere, så du ikke længere kan eksponere tyk fotoresist - og med tyk mener jeg 30 nanometer," sagde Philippe Bézard, tørætsnings R&D-ingeniør hos imec. "Men du skal stadig mønstre den samme filmtykkelse nedenfor. Så nu beder du om meget højere selektivitet i den forstand, at vi i stedet for 2:1 skal nå mere som 10:1, hvilket er en pludselig 4X til 5X selektivitetsforbedring."

Fra proof of concept (POC) til high-volume manufacturing (HVM)

Bézard beskriver tre faser af etch-procesudvikling:

- Bestemmelse af, hvilken ætser, gasser, hjælpelag osv., der er nødvendige for at udføre ætsningen;

- Demonstrer ydeevne ved fuldstændig fjernelse af film inden for specifikationerne med procesensartethed på tværs af en wafer, og

- Bestemmelse af, hvordan processen kan gentages på tværs af tusindvis af wafere i HVM med højt udbytte og lille drift.

Typisk håndterer dygtige ætse- og integrationsingeniører de to første udviklingsfaser. Den tredje fase kan igen bruge ingeniørekspertise, men maskinlæring kan hjælpe.

"Maskinlæring og dataanalyse generelt er kun nyttig i den tredje fase," sagde han. "Det er meget kraftfuldt, fordi det har adgang til et væld af data og kan give mening ud af en million små, enkle ting, der alle interagerer. Så for en menneskelig hjerne at prøve at finde ud af dette er meget svært, men det er mere overskueligt for et computerprogram. Men i tilfælde, hvor du har en ny applikation, nyt materiale, der bliver ætset eller en ny integration, viser det ikke nogen forbedring i forhold til mennesker."

ML-brug vedrører også fremstillingsomkostninger, fordi tusindvis af wafere bruges i fase tre - mindst en størrelsesorden større end der bruges i fase et og to.

Barrett Finch, seniordirektør for Etch Product Group hos Lam Research, beskriver ny processtifinding som at tage et proof-of-concept fra et nominelt procesflow og layout og udvikle en eller flere arbejdsenheder på en wafer. Denne POC overføres derefter til et produktudviklingsteam i fabrikken for at opskalere processen og forbedre udbyttet.

"Mængden af arbejde, der kræves for at omdanne et nominelt proof-of-concept til et levedygtigt produkt, er ofte undervurderet, og dette skaber et stort hul til rentabiliteten," sagde Finch. "Procesvinduemodellering søger at lukke dette hul ved at introducere fantastisk variation i de tidlige stadier af F&U-stifinding." Han foreslår, at virtuelle DOE'er og Monte Carlo-baserede analyser på tværs af en række procesparametre tester en POC ved at simulere forventet variabilitet.

"Procesvinduemodellering kan besvare spørgsmålet, 'Hvilken cd eller niveau af variabilitet skal jeg opretholde for at opnå minimumsydelse og ydeevne for enheden?' Vi har gennemført virtuelle procesvindue-tests med op mod 1 million virtuelle wafere på få dage, hvilket ville være umuligt at opnå i det virkelige liv,” sagde han.

Flere parametre påvirker ætsningshastighed, profil og selektivitet. En nøgle er temperaturen. "Indvirkningen af termiske effekter i ætsningsbehandling ses af vores kunder, da de kontrollerer ætsningshastigheder, selektiviteter og ætsede profiler. Alle disse parametre kan påvirke både enhedsudbytte og fab-produktivitet,” sagde Benjamin Vincent, senior manager for halvlederproces- og integrationsteknik hos Lam Research. Han hævder, at simulering kan være særlig nyttig, når et procestrin har flere mulige konfigurationer (procespladsen er stor), eller hvor nedstrømsresultaterne fra trinnet er meget uforudsigelige.

"Ætseprocessen er afhængig af waferens overfladetemperatur, som afhænger af adskillige varmefluxer - herunder termisk ledning, ionpåvirkningsenergier, overfladereaktioner og plasmastrålingsvarmefluxer," sagde Alex Guermouche, produktmarketingchef hos Esgee Technologies, en Lam Research Company. "Som et resultat skal plasmamodeller inkorporere alle disse fysikfunktioner for nøjagtigt at afbilde temperaturændringer på waferens overflade. Processimuleringssoftware kan modellere en række ætsningsattributter, hvilket giver os mulighed for hurtigere at få et bedre ætseresultat og accelerere kundens evne til at øge produktionen eller optimere udbyttet."

Præcis timing af ætseprocessen

Med strammere geometrier og tyndere film er der behov for at afbalancere ætsningshastigheden med stor kontrol over andre driftsparametre.

"Med krympende designregler bevæger mange ætsningsprocesser sig til meget hurtige plasmaætsningsprocestrin, der kræver meget præcis styring af alle reaktionsinputs: effekt, tryk, kemi og temperatur," sagde Finch og bemærkede, at der også er en tendens i retning af optimeret plasma pulserende adfærd for at generere et bestemt ion-til-neutralt forhold, og derefter feje biprodukter væk. "Avanceret modellering af sådanne forhold vil være afgørende for at muliggøre yderligere enhedsskalering."

Producenter af ætsningssystemer har brugt modelleringssoftware i nogen tid for at fremskynde udviklingen af næste knude eller rampeudbytte. Dette er ingen overraskelse i betragtning af den store kompleksitet af processen og alle dens variabler.

"Der er simpelthen ikke tid nok eller nok wafere til at udføre alle mulige proceseksperimenter, når der udvikles næste node-teknologier," sagde Finch. "Antallet af kombinationer af ætseudstyrsindstilling kan løbe op i millioner eller endda milliarder, og udvikling af brute force wafer ved at bruge alle procesmuligheder er simpelthen umuligt."

Selvfølgelig er alle gode modeller verificeret på faktiske chips. "En nøjagtig model bør være forudsigelig, og den bør løse det målrettede problem, som en bruger ønsker at løse," sagde Finch. "Hver gang en proces eller designændring er blevet anbefalet baseret på simuleringsarbejde, bør faktiske fab-data afspejle resultaterne af anbefalingen. I vores tilfælde har vi været i stand til præcist at forudsige effekten af procesændringer ved hjælp af modelbaserede resultater og hurtigt løse vanskelige proces- og teknologiudviklingsproblemer."

Værktøjsleverandører arbejder også på avancerede ætsningsprocesser for tættere at integrere linjer og transformere det, der engang var en proces på to maskeniveauer (to litografitrin) til én til procesforenkling og omkostningsreduktion.

"I stedet for at tilpasse eksisterende hardware for at gøre den schweiziske hærkniv endnu mere udstyret, introducerer virksomheder teknologier, der er applikationsspecifikke, såsom nye systemer til at løse tip-to-tip-problemer," sagde Bézard. Målet er at få to linjer, der vender mod hinanden, tættere på hinanden, hvilket i øjeblikket involverer et linjemønstertrin efterfulgt af en skåret maske. "Hvad Applied Materials og andre introducerer, er en måde at ætse direkte i vandret retning." Sådanne processer kan også udvides via huller.

Ætsetrin til nanoark-FET'er

Den mest kritiske ætsning træder ind nanoark processtrømme inkluderer dummy gate ætsning, anisotrop søjle ætsning, isotrop spacer ætsning og kanalfrigivelsestrinnet. [1] Profilen ætser gennem skiftende lag af silicium og SiGe er anisotropisk og bruger fluorkemi. Den indre afstandsætsning (indrykning) og kanaludløsningstrin er optimeret til at fjerne SiGe med ekstremt lavt siliciumtab.

Kanalfrigivelsestrinnet er kritisk. "Udgivelsen af nanoarket kræver ekstrem høj selektivitet," sagde Bézard. "De fleste nanoplader er silicium, derefter silicium-germanium og silicium. Du har skiftende lag, og du skal fjerne det ene uden at ændre det andet overhovedet." Nogle publikationer har diskuteret udførelse af en flertrins SiGe-ætsning for at reducere stress på strukturen induceret af et enkelt ætsningstrin.

Næste i processen er dannelsen af selvjusterede kontakter. "Her er det, vi forsøger at gøre, dybest set at ætse siliciumdioxid og ikke røre eller forsænke siliciumnitridet. Nuværende specifikationer er, lad os sige, 3nm forsænkning, men folk anmoder om nul tab,” sagde Bézard. "I dette tilfælde bruger vi ikke engang ordet selektivitet. Vi taler bare om frikvarter – og nul frikvarterer.

3D NAND

Til 3D NAND flash fortsætter antallet af lag med at vokse og nødvendiggør vedtagelsen af flere stablede niveauer i fremtiden, hvilket til sidst skaber lodrette strenge af stablede enheder. "Der er også en masse drivkraft for at skalere ordlinje-pitch eller vertikal/Z-pitch af lagene, efterhånden som antallet af lag vokser for at fortsætte med at øge bittætheden," sagde Robert Clark, seniormedlem af teknisk personale og teknologidirektør hos TEL. "Fra et procesperspektiv vil ætsnings- og deponeringsprocesser have behov for konstant forbedring for at imødekomme de stadigt højere billedformater ved stadig mindre kritiske dimensioner, som fortsat skalering kræver."

Clark beskrev fremtidige ændringer. "Hvis man ser mod avancerede noder af ladefælde-enheder med flere niveauer, vil konstruktion af gate-stakkene være påkrævet for at opnå kortere gate-længder, flere niveauer pr. celle og forbedret programmeringseffektivitet - potentielt gennem adoption af high-k-materialer. Højere ledningsevnekanaler vil sandsynligvis også være påkrævet for at erstatte poly-Si-kanaler i fremtiden," sagde han.

En af de mest kritiske ætsninger i 3D NAND involverer dyb ætsning af omkring 100 nm huller gennem flerlags oxid-nitrid stakke (200+ lag), som kan være op til 10 µm dybe. Imecs Bézard sagde, at dette ætsningstrin er et særligt dyrt.

"Vi har et fysisk fænomen, der opstår, kaldet den differentielle opladningseffekt," sagde han. "I plasmaet har vi elektroner, ioner og neutrale arter for at forenkle meget. Elektroner bevæger sig i alle retninger, men ioner accelereres vinkelret på overfladen. Så du har positiv ladning i bunden af hullet og negative ladninger i toppen, og du får et elektrisk felt, der forsøger at frastøde indkommende ioner."

Som følge heraf er høje effektniveauer nødvendige for at ætse renden fuldstændigt. "Vi forsøger at opretholde 30 til 50 gigawatt effekt uden buedannelse, og derfor skal patronen være ekstremt velpoleret og velfremstillet," sagde han.

De dybe ætsninger inducerer også spændinger, der skal minimeres, især fordi multi-tiered NAND-fabrikation efterfølgende kræver wafer-udtynding, præcis justering og hybridbinding til det næste lag.

Andre processer

Ikke alle chipproducenter producerer førende chips, der kræver EUV-litografi. Mange fabrikker udvider deres 193nm litho- og ætsningsprocesser.

"Vi har et højtemperatur-SOC-materiale, som vi for nylig er begyndt at introducere, som udvider dets mønsteregenskaber og kan modstå højere temperaturer, uanset om det bruges som underlag til et CVD-lag eller maske," sagde Brian Wilbur, direktør for halvlederprodukters diversificering hos Bryggervidenskab.

BEOL for de tætteste metallinjer forventes at gennemgå en dramatisk overgang fra dobbelte damascene-integrationsordninger til subtraktiv aflejring og ætsning af andre forbindelser end kobber. Her har to metaller - ruthenium og molybdæn - været de mest gennemarbejdede. Det er dog mere sandsynligt, at molybdæn oxiderer under ætsning, hvilket gør det mere kompatibelt med dobbelte damascene-skemaer. Ruthenium er et ædelmetal, så det har ikke de samme korrosionsproblemer, men det er dyrere.

Enhedsstrukturer er også ved at blive intolerante over for kantplaceringsfejl. Nye ordninger for selvjustering fra lag til lag og mellem vias og linjer vil være nødvendige, ifølge TELs Clark. "De første implementeringer vil sandsynligvis være for ting som nedgravede ordlinjer i DRAM og de små MOL-metallag til logik, hvor der er behov for højere termisk stabilitet såvel som lavere resistivitet eller liner-løse metaller."

Næste generations udvikling

På lang sigt vil industrien ideelt set gå over til back-end-processer med et lavere termisk budget (tættere på 300°C end 400°C) for at integrere enheder i back-end-sammenkoblingslag.

"Branchen har et reelt behov for at begynde at bygge enheder i flere lag," sagde TEL's Clark. "Det betyder, at vi har brug for hukommelses- og logikenheder bygget inden for BEOL med BEOL termiske budgetter."

Indtil videre ser enheder fremstillet ved hjælp af halvledende oxider lovende ud, både til at integrere hukommelsesenheder i et logisk BEOL-flow eller til at bygge CMOS-arrays oven på hukommelsesarrayet i DRAM'er.

Et andet væsentligt skift involverer integrationen af 2D-materialer, som forskningshuse og førende chipproducenter allerede er begyndt at teste. Ætsningsprocesser for materialer som wolframdisulfid eller molybdændisulfid overvejes. Filmene består af et enkelt lag af materiale, så det er ekstremt udfordrende at udvikle fantastiske processer til at integrere dem.

Bæredygtighed

Chipproducenter og materialeleverandører forfølger alternativ kemi for at reducere kulstofemissioner. Inden for ætsning er hovedsynderne fluorholdige gasser med et højt globalt opvarmningspotentiale.

"En grund til, at du har PFOS (perfluoroctansulfonsyre), som er problematisk, er, at molekylet er så stabilt," sagde imecs Bézard. "Lys eller kemiske reaktioner i atmosfæren er ikke tilstrækkelige til at nedbryde den."

Han sagde, at en række alternative gasblandinger med højere iltindhold er lettere dissocierede og har lavere GWP. "Men enhver kandidat skal levere lige så god eller endnu højere præstationer for at starte."

Men bæredygtighed er ikke en særlig ætsnings- eller aflejringsudfordring. Det er en holistisk brancheudfordring fra litografi til emballage, hvor virkningen af et nyt materiale påvirker hele enhedsbehandlingen.

Henvisning

1. K. Derbyshire, "Hvad er anderledes ved næste generations transistorer", Semiconductor Engineering, 20. oktober 2022.

Relaterede historier

Meget selektiv ætsning ruller ud til næste generations chips

Fremstilling af 3D-strukturer vil kræve kontrol på atomniveau af, hvad der er fjernet, og hvad der bliver på en wafer.

- SEO Powered Content & PR Distribution. Bliv forstærket i dag.

- PlatoAiStream. Web3 Data Intelligence. Viden forstærket. Adgang her.

- Udmøntning af fremtiden med Adryenn Ashley. Adgang her.

- Køb og sælg aktier i PRE-IPO-virksomheder med PREIPO®. Adgang her.

- Kilde: https://semiengineering.com/etch-processes-push-toward-higher-selectivity-cost-control/

- :har

- :er

- :ikke

- :hvor

- $OP

- 000

- 1

- 10

- 13

- 20

- 2022

- 2D

- 2D-materialer

- 30

- 3d

- 50

- a

- evne

- I stand

- Om

- fremskynde

- accelereret

- adgang

- imødekomme

- udrette

- Ifølge

- præcis

- præcist

- tværs

- faktiske

- adresse

- Vedtagelse

- fremskreden

- fordelagtige

- påvirke

- igen

- sigte

- alex

- Alle

- tillade

- allerede

- også

- alternativ

- beløb

- an

- analyse

- ,

- En anden

- besvare

- enhver

- vises

- Anvendelse

- applikationsspecifik

- anvendt

- ER

- Army

- Array

- AS

- udseende

- hjælpe

- At

- Atmosfære

- attributter

- væk

- Back-end

- Balance

- baseret

- I bund og grund

- BE

- Beam

- fordi

- blive

- været

- før

- Begyndelse

- være

- jf. nedenstående

- Benjamin

- BEDSTE

- Bedre

- mellem

- skævhed

- Big

- milliarder

- Bit

- både

- Bund

- grænser

- Brain

- Pause

- Brian

- brute force

- budget

- Budgetter

- Bygning

- bygget

- men

- by

- kaldet

- CAN

- kandidat

- kulstof

- kulstofemissioner

- hvilken

- tilfælde

- tilfælde

- CD

- Celler

- udfordre

- udfordrende

- Kammer

- lave om

- Ændringer

- Kanal

- kanaler

- afgift

- opladet

- afgifter

- opladning

- kemikalie

- kemikalier

- kemi

- Chips

- Rengøring

- Luk

- nøje

- tættere

- kombinationer

- Virksomheder

- selskab

- kompatibel

- fuldføre

- Afsluttet

- komplekse

- kompleksitet

- computer

- Konceptet

- betingelser

- ledningsevne

- dirigent

- betragtes

- konstant

- kontakter

- indhold

- fortsæt

- fortsatte

- fortsætter

- kontrol

- Kobber

- Corporate

- korrosion

- Koste

- omkostningsreduktion

- Omkostninger

- kunne

- kursus

- skabe

- skaber

- Oprettelse af

- kritisk

- Nuværende

- For øjeblikket

- Kunder

- Klip

- data

- dataanalyse

- datalogi

- Dage

- dyb

- levere

- tæthed

- afhænger

- beskrevet

- Design

- udviklet

- udvikling

- Udvikling

- enhed

- Enheder

- forskellige

- svært

- størrelse

- retning

- direkte

- Direktør

- drøftet

- diversificering

- do

- gør

- dollars

- ned

- dramatisk

- køre

- tørre

- i løbet af

- hver

- Tidligt

- nemt

- effekt

- effekter

- effektivitet

- enten

- Elektrisk

- elektroner

- Emissioner

- muliggør

- ingeniør

- Engineering

- Ingeniører

- nok

- lige

- udstyr

- udstyret

- Ækvivalent

- især

- væsentlig

- væsentlige

- etc.

- Endog

- til sidst

- Hver

- krævende

- undersøger

- udføre

- eksisterende

- forventet

- dyrt

- eksperimenter

- ekspertise

- udsat

- strækker

- ekstremt

- vender

- langt

- FAST

- hurtigere

- Funktionalitet

- få

- felt

- Figur

- Film

- film

- Fornavn

- Blink

- flow

- strømme

- Fokus

- efterfulgt

- efter

- Til

- Tving

- formular

- formation

- Videresend

- fire

- Gratis

- fra

- fuldt ud

- yderligere

- fremtiden

- kløft

- GAS

- Generelt

- generere

- få

- given

- Global

- global opvarmning

- mål

- godt

- stor

- gruppe

- Grow

- Vokser

- Halvdelen

- håndtere

- Hård Ost

- Hardware

- Have

- he

- hjælpsom

- link.

- Høj

- Højt udbytte

- højere

- stærkt

- Hole

- Huller

- holistisk

- Vandret

- huse

- Hvordan

- Men

- HTTPS

- menneskelig

- Mennesker

- Hundreder

- Hybrid

- i

- KIMOs Succeshistorier

- umuligt

- Forbedre

- forbedret

- in

- omfatter

- Herunder

- Indgående

- indarbejde

- stigende

- industrien

- indgange

- instans

- i stedet

- integrere

- Integration

- integration

- interaktion

- interaktioner

- sammenkobler

- ind

- indføre

- spørgsmål

- IT

- ITS

- jpg

- lige

- Nøgle

- Lam

- stor

- større

- lag

- lag

- Layout

- førende

- læring

- mindst

- Niveau

- niveauer

- Livet

- ligesom

- Sandsynlig

- Line (linje)

- linjer

- LITHO

- lidt

- logik

- længere

- Se

- off

- Lot

- Lav

- maskine

- machine learning

- lavet

- Main

- vedligeholde

- lave

- Makers

- Making

- leder

- fremstillet

- Fabrikant

- Produktion

- mange

- Marked

- Marketing

- Marketing Director

- maske

- materiale

- materialer

- max-bredde

- Kan..

- betyde

- midler

- medlem

- Hukommelse

- metal

- Metaller

- Metrics

- måske

- million

- millioner

- minimum

- mangler

- model

- modellering

- modeller

- modes

- MOL

- molekyle

- måned

- mere

- mest

- bevæge sig

- flytning

- meget

- flere

- næsten

- Behov

- behov

- behov

- negativ

- Neutral

- Ny

- næste

- ingen

- Noble

- node

- noder

- nu

- nummer

- oktober

- of

- tit

- on

- engang

- ONE

- kun

- drift

- Produktion

- optimering

- Optimer

- optimeret

- or

- ordrer

- Andet

- Andre

- vores

- ud

- i løbet af

- Oxygen

- emballage

- parametre

- særlig

- især

- Mønster

- Mennesker

- udføre

- ydeevne

- udfører

- måske

- perspektiv

- fase

- fænomen

- Philippe

- fysisk

- Fysisk

- Fysik

- Søjle

- Pitch

- afgørende

- Plasma

- plato

- Platon Data Intelligence

- PlatoData

- spiller

- PoC

- positiv

- muligheder

- mulig

- eventuelt

- potentiale

- potentielt

- magt

- vigtigste

- brug

- Precision

- forudsige

- præsident

- tryk

- Problem

- problemer

- behandle

- Processer

- forarbejdning

- producere

- Produkt

- produktudvikling

- produktion

- produktivitet

- Produkter

- Profil

- Profiler

- rentabilitet

- Program

- Programmering

- lovende

- bevis

- Bevis for koncept

- publikationer

- Skub ud

- spørgsmål

- hurtigt

- F & U

- Rampe

- rækkevidde

- Sats

- priser

- forholdet

- nå

- Reagerer

- reaktion

- reaktioner

- ægte

- I virkeligheden

- grund

- for nylig

- Anbefaling

- anbefales

- reducere

- reducere

- reduktion

- afspejler

- fast

- frigive

- pålidelig

- stole

- fjernelse

- Fjern

- fjernet

- fjernelse

- gentagelig

- gentaget

- erstatte

- indberette

- kræver

- påkrævet

- Krav

- Kræver

- forskning

- resultere

- Resultater

- afslører

- højre

- ROBERT

- roller

- ruller

- groft

- regler

- Kør

- Said

- samme

- siger

- Scale

- skalering

- ordninger

- Videnskab

- søger

- set

- selektiv

- halvleder

- senior

- forstand

- indstilling

- flere

- skifte

- bør

- Silicon

- Simpelt

- forenkle

- ganske enkelt

- simulation

- enkelt

- faglært

- lille

- So

- Software

- Løsninger

- SOLVE

- nogle

- et eller andet sted

- Kilde

- Space

- specifikke

- specifikationer

- specs

- hastighed

- Stabilitet

- stabil

- stablet

- Stakke

- Personale

- etaper

- starte

- påbegyndt

- Trin

- Steps

- Stadig

- stress

- struktur

- Efterfølgende

- væsentlig

- sådan

- pludselige

- tilstrækkeligt

- foreslår

- leverandører

- overflade

- overraskelse

- Bæredygtighed

- bæredygtig

- Sweep

- Schweizisk

- Systemer

- Tag

- tager

- Tal

- målrettet

- hold

- Teknisk

- Teknologier

- Teknologier

- Teknologiudvikling

- semester

- prøve

- Test

- tests

- end

- at

- Fremtiden

- deres

- Them

- derefter

- Der.

- termisk

- Disse

- de

- ting

- Tredje

- denne

- grundigt

- tusinder

- tre

- Gennem

- tier

- strammere

- tid

- timing

- til

- sammen

- Ton

- TONE

- også

- top

- mod

- overført

- Transform

- overgang

- Trend

- prøv

- to

- typisk

- typisk

- underliggende

- uforudsigelige

- på

- opad

- us

- brug

- anvendte

- Bruger

- ved brug af

- udnytte

- verificeres

- lodret

- lodret

- meget

- via

- levedygtig

- Vice President

- vincent

- Virtual

- flygtige

- ønsker

- ønsker

- var

- Vej..

- we

- uger

- GODT

- Hvad

- hvornår

- hvorvidt

- som

- mens

- Hele

- hvorfor

- vilje

- med

- inden for

- uden

- ord

- Arbejde

- arbejder

- virker

- ville

- år

- år

- Udbytte

- hvilket giver

- udbytter

- dig

- zephyrnet

- nul