Chiplets begynder at påvirke chipdesignet, selvom de endnu ikke er mainstream, og der ikke findes nogen kommerciel markedsplads for denne form for hærdet IP.

Der er løbende diskussioner om siliciums livscyklusstyring, den bedste måde at karakterisere og forbinde disse enheder på, og hvordan man håndterer sådanne problemer som ujævn aldring og termisk uoverensstemmelse. Derudover er en stor indsats i gang for at forbedre observerbarheden af chips over tid, noget der er særligt vigtigt, da disse enheder bruges i sikkerhedskritiske og missionskritiske applikationer.

Alle disse problemer skal løses for at muliggøre udbredt anvendelse, og chipindustrien har erkendt, at opbremsningen af Moores lov kombineret med faste sigtekorsstørrelser vil kræve ændringer i, hvordan chips designes, fremstilles og emballeres. Det er fysisk umuligt at passe alle de funktioner, der kræves til mange applikationer, i en enkelt SoC, og målet er nu en velordnet, forudsigelig og gentagelig tilgang til at opdele mange af disse komponenter. I teorien vil dette gøre det lettere at tilpasse enheder, fremskynde tiden til markedet og undgå dyr skalering af komponenter, der ikke kræver det, såsom analoge funktioner.

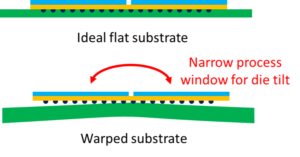

At nå dette mål vil dog kræve løsning af nogle komplekse og vanskelige problemer. For det første vil det kræve meget bedre observerbarhed, overvågning og analyse af, hvad der indgår i en pakke. Mens konceptet med at lægge flere chips i en pakke går tilbage til 1990'erne med multi-chip moduler, med chiplets er matricerne typisk mindre og tyndere, og dynamikken i, hvordan man karakteriserer, tester og observerer dem, har ændret sig betydeligt.

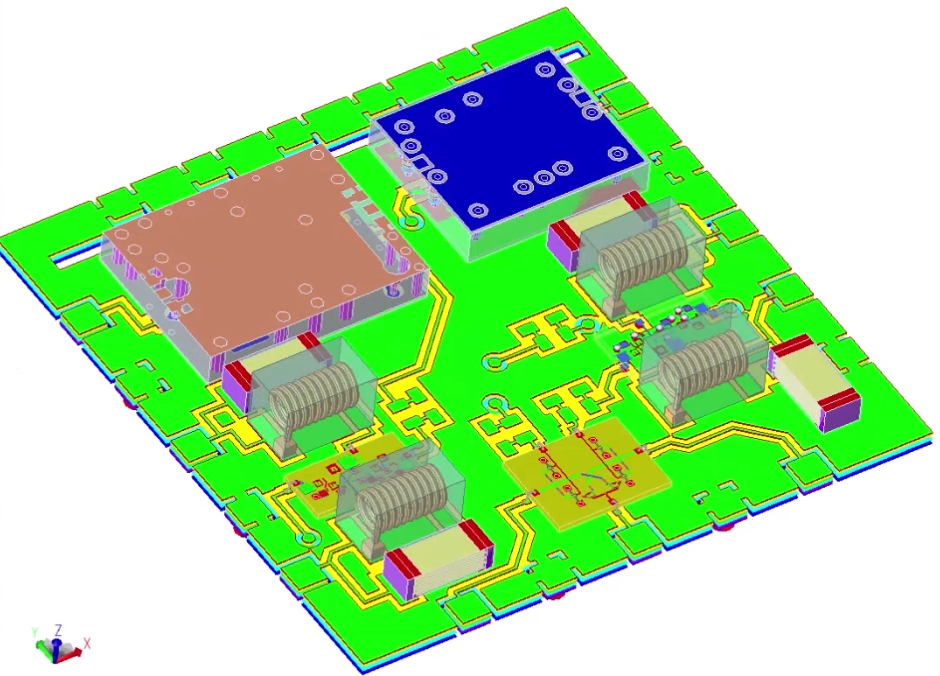

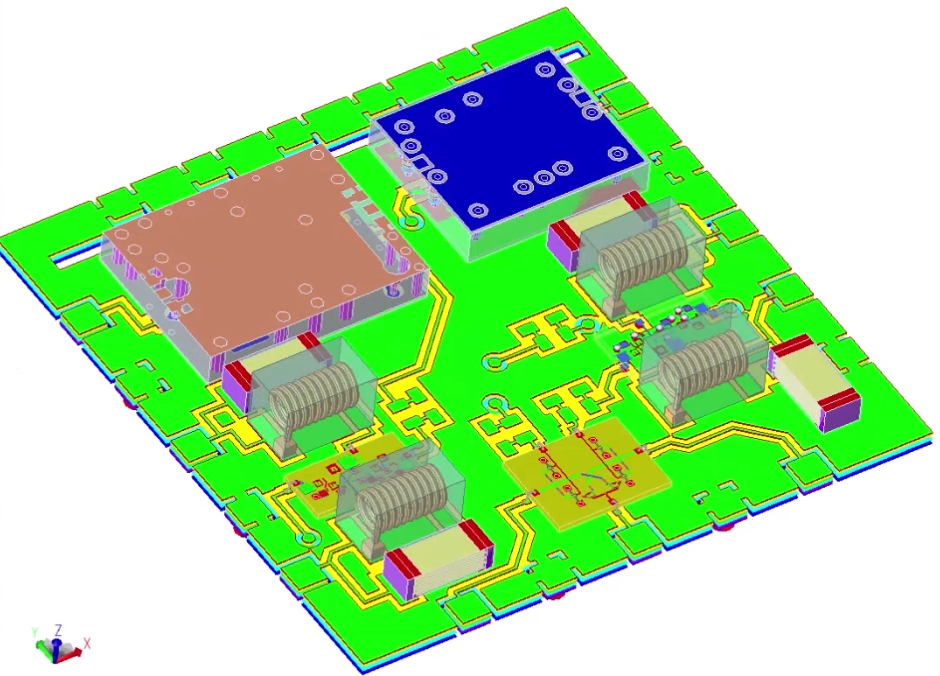

"Historisk har vi kaldt disse multi-chip-moduler, som er meget populære i den trådløse verden i dag," sagde Nilesh Kamdar, leder af RF/mikrobølge-porteføljen hos Nøglesyn. "Du tager en hvilken som helst smartphone op, og den trådløse del af smartphonen er et front-end-modul, der er 20 til 30 chips presset sammen på et lille rum, der er mindre end en fingernegl. Det er sket i branchen i mindst et årti, hvis ikke længere. Desuden har adskillige rumfarts- og andre højfrekvente problemer krævet denne form for integration, så vi har gjort dette tidligere."

Fig. 1. Multi-chip RF-modullayout vist i Keysights PathWave ADS. Kilde: Keysight

Det store skift, der nu er i gang, involverer en meget bredere anvendelse af denne tilgang, såvel som forbedringer i chiplet-designet og standardmåder til at forbinde, teste og måle, hvad der sker inde i selve chiplets, såvel som den avancerede pakke, der omgiver dem.

"Automotive er et godt eksempel på, hvad der ændrer sig," sagde Kamdar. "På en nylig konference talte en vicepræsident fra en større OEM om ikke at kunne tage et datacenter og placere det på bagsædet af en bil, fordi det er det, der skal til for at have et autonomt køretøj i dag. Hvis du laver mere integration - og hvis du på en eller anden måde får brættet til at forsvinde, og alt bliver klemt sammen - kan vi måske presse det lodret ind på bagsædet af en bil. Der er mange lignende use cases. Strømbehovet til chiplets kan være lavere, hvis du overvejer fysiske datacentre. Der er mange fordele, og det er det, der driver chiplets i dag.”

Disse ændringer er imidlertid vildledende komplekse, og industrien kan blive nødt til at gå tilbage til skolen om dette. "At bygge chiplets i stor skala er en så anderledes model, at vi alle er nødt til at revurdere vores færdigheder," sagde han. "Vi skal revurdere, hvordan organisationer er sat op, og hvordan arkitektur sker. Vi skal revurdere rollen som systemdesigner. De har måske set på tingene på en anden måde, og de kan have sagt: 'Jeg er systemdesigner. Jeg designer specifikationerne for systemerne. Jeg deler det op i komponenter på mindre niveau, individuelle IC'er og distribuerer specifikationerne. Jeg går væk og kommer tilbage seks måneder senere og ser, hvordan alle klarede det.' Måske er det ikke engang muligt. Måske er der flere systemdesignere, der skal eksistere op og ned i kæden. Det er den slags samtaler, der skal ske. Inden for de største aktører i industrierne foregår disse samtaler allerede, men ikke overalt."

Antallet af potentielle interaktioner i forbindelse med et multichiplet-design er betydeligt og i mange tilfælde designspecifikt. "Hvis du tror på multi-die, hvis du tror på chiplets, er du nødt til at tro, at det kun vil forværre hele [design og integration]-problemet," sagde Shekhar Kapoor, seniordirektør for produktlinjeledelse for Synopsys EDA Group. "Chiplets vil komme fra mange steder, mange kilder. Der vil være mange valgmuligheder, mange muligheder for alle. Det største problem er de nuværende brug omkring alt dette. Store virksomheder gør dette på en skræddersyet og tilpasset måde. Men hvis du går bredt ud med standardisering, hvordan ved du, at en chiplet, der kommer ind, vil passe ind i miljøet, i det produkt, du forsøger at bygge?"

På trods af fokus på standarder som UCIe og Bunch of Wires, er der stadig nuancerne i forhold til, hvordan de enkelte chiplets karakteriseres i et system. “Hvordan kender du egentlig profilen på det? Det er her, der vil komme endnu mere overvågning ind i billedet, hvilket næsten er som en signatur,” sagde Kapoor. "Du kan læse den og vide, om den er ideel til dit miljø. I betragtning af at industrien bevæger sig mod mere chiplet-aktivering, vil dette være en kerneovervejelse. Flere krav vil dukke op, flere standarder vil dukke op, så man kan se, om noget kommer til at passe eller ej.”

Der er også andre udfordringer at overvinde.

"Med chiplets er alle højhastighedssignaler inden for pakken, så observerbarhed er meget mere udfordrende," sagde Sue Hung Fung, produktlinjemarketingchef for UCIe hos kadence. ”Dette kan gøres gennem linkfejltjek, øjenscanninger, BiST osv. for at komme til en kendt god die (KGD). Testmetoder er alle bygget op omkring dette. Derudover ville det være værdifuldt at have gode skærme for linkets sundhed, og der er nye og anderledes forslag fra forskellige leverandører."

Nøglen er at overvåge signalkvaliteten i sammenhæng med resten af komponenterne i en pakke, hvilket bliver vanskeligere, efterhånden som flere funktioner opdeles i chiplets.

"Kan vi overvåge signalerne og kvaliteten af disse under dataoverførsel? Træningsteknikker udføres før missionstilstand for at forbedre dataoverførslens robusthed,” bemærkede Hung Fung. “Omskoling er ikke ønsket, da det kan forårsage dataafbrydelse. Vi skal løbende være i stand til at overvåge og rapportere hver vognbane og opdage eventuelle hændelser, der kan forårsage fejl, før en fejl opstår. Forebyggelse af systemfejl og reparation af disse fejl omfatter redundant banekortlægning eller andre reparationsmetoder til at opdage marginalt svigtende baner. Træning og kontinuerlig overvågning af disse interne chiplet-signaler er udfordringerne for at analysere linkadfærden."

Arbejdsgrupper for UCIe søger at standardisere noget af denne observerbarhed for at have et åbent link-økosystem. Men tilføjelse af observerbarhed og overvågning kan også variere meget efter lodret segment.

Randy Fish, direktør for produktlinjestyring for Synopsys EDA Group, forklarede, at fordi der ikke har været nogen standardtilgang og få kommercielle leverandører til observerbarhedsløsninger, er næsten alle løsningerne blevet skræddersyet. "Hvis du går ind i en af de førende semifinaler, gør de noget," sagde han. "Spørgsmålet er, er der funktioner omkring multi-die, der vil tvinge os til at standardisere for at have en sammenhængende eller sammenhængende infrastruktur til overvågning og fejlretning - dybest set for at se, hvad der foregår, især hvis du får flere dies fra flere leverandører. Nogle af multi-die-løsningerne går ind i bilindustrien, og der bekymrer de sig om ting som aldring, og hvad der sker med disse dør. Og som vi ved, er det avancerede noder. Det er ikke sådan, at du har 6 dør af modne 10 år gamle teknologier. Disse er avancerede noder, der ikke har en lang historie. Af den grund er der en række faktorer, der tvinger dette til at ske."

Chiplets introducerer også nogle interessante kontraster. Keysights Kamdar bemærkede, at under et nyligt CEO-panel sagde en af paneldeltagerne, at chiplets har en unik dikotomi. "På den ene side kunne hver chiplet være en uafhængig IP, som du kan anskaffe fra en IP-leverandør og integrere den i dit system til relativt lave omkostninger, relativt nemt. Men hele stakken, som du prøver at bygge, tvinger dig pludselig til at vide alt. Tidligere kunne du bare have sagt: 'Jeg har brug for seks ting. Jeg har tænkt mig at købe fem fra hylden fra en IP-leverandør, og de vil finde ud af, hvad den har brug for. Jeg vil fokusere på én.' Men nu får du måske ikke succes med at gøre det. Du skal måske faktisk vide, hvordan du gør alle seks, og finde ud af, hvordan alt det sker, fordi problemets kompleksitet lige er steget. Dette kan tvinge industrien til i første omgang kun at tillade de store aktører at finde ud af dette. Det kan tage meget længere tid for de mindre leverandører at være i stand til at få succes i dette miljø."

Ikke desto mindre vil det tage mere end én virksomhed at fremskynde chiplet integration og adoption.

"Keysight deltog i TSMC Symposium, som er en mere offentlig begivenhed, og som opfølgning var der en workshop med kun de partnere, der er en del af 3D Fabric Alliance," sagde Kamdar. “TSMC startede og sluttede hele dagen med at tale om, hvordan vi alle skal arbejde på dette sammen, hvilket blev gentaget af andre deltagere, inklusive AMD og Qualcomm. Talere fra begge virksomheder sagde, at ikke et eneste EDA-firma ved, hvordan man løser chiplet-problemet på egen hånd. Hele branchen skal arbejde sammen.”

Tekniske udfordringer

En anden vigtig bekymring med chiplets er varmeafledning. Dette er en del af karakteriseringen, men det er også meget afhængig af use cases, pakkevalg og den overordnede system-in-package-arkitektur.

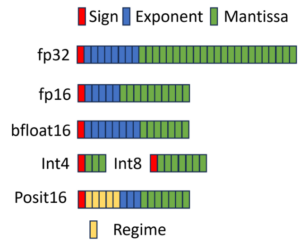

"For chiplets er marginaliteten i designet slank, givet optimal PPA (målrettet mod aggressiv pj/bit og stranddensitet), hvilket er afgørende, når man designer chiplet PHYs," sagde Rishi Chugh, vicepræsident for produktmarkedsføring, IP Group hos Cadence. "Plidelighed er nøglen, og det samme er observerbarhed for at screene KGD'en, samt få den til kommerciel operationel succes. Dataintegritetsordninger som CRC (cyklisk redundanstjek), øjenscanning, BiST og overvågningskredsløb er implementeret i designet for robusthed, og designet skal være overprovisioneret med fejlmekanismer for at sikre, at datalinjen er modstandsdygtig."

Et helt kapitel i UCIe-protokollen er dedikeret til initialisering og træning forbundet med UCIe-protokollen, som dækker observerbarhedsaspektet af protokollen, tilføjede Chugh.

Derudover er der debat om, hvorvidt det faktiske grundlag for at tilføje observerbarhed til et system er den sværeste del, eller om ændringen i tænkning omkring disse begreber er sværere.

”Det er faktisk ikke så kompliceret i modsætning til andre ting, fordi det 'bare' er endnu en blok, der skal kobles på. Der er observation, og vi har evner til at spore ting,” sagde Frank Schirrmeister, vice president for løsninger og forretningsudvikling hos Arteris IP. "Brugerne efterspørger allerede ting som at se på registrene fra et softwareperspektiv. Så nu bliver udfordringen at gøre disse registre tilgængelige i NoC. Fra et NoC-perspektiv er der selve protokollerne som CHI, ACE, AMBA, OCP eller andre, og det er sprogets mekanismer - hvordan de taler og hvordan de interagerer. Inden for NoC, med de mere komplekse protokoller, sker der ting over flere cyklusser, så du skal vente på svar, du sætter tingene i pipelinen."

Dette svarer til spekulativ udførelse i processorer. "Vi taler om disse kreditter, som hvor længe skal jeg vente på svar og så videre," forklarede Schirrmeister. "Det er alle dele af protokollerne. I NoC skal du forstå spørgsmål som hvor dybe er bufferne? Hvornår venter jeg egentlig på data? Det er til dels præstation. Derefter kan du for observerbarheden oprette forbindelse til dataene, og sensorerne kan bruge deres eget netværk, afhængigt af hvordan du vil konfigurere det. I tilfælde af on-chip skærme, skal du beslutte, om du vil sætte dette på en speciel observerbarhedsbus, for eksempel. Der er altid en diskussion om, hvor meget debug jeg egentlig har? I slutningen af dagen er det 'bare' endnu en sammenkobling af disse komponenter, og du skal beslutte, hvordan du eksporterer den ud af chippen, og så videre. Hvor meget du gemmer på chip er alt sammen et spørgsmål om, hvor meget siliciumejendom er jeg villig til at bruge for det?"

Det bliver især vigtigt, når du syr chiplets sammen. "Hvordan sikrer jeg, at jeg har plads nok til denne beregningsenhed, der bare ligner data, som faktisk ikke tilføjer nogen værdi til den umiddelbare funktion?" spørger Gajinder Panesar, chefarkitekt hos Picocom. »Jeg er måske heller ikke overvågningsekspert, men jeg ved, at jeg har brug for det. Så jeg har brug for noget, der siger: 'Bare tryk på den knap.' Du har et miljø, vi designer, og 'dette' sker. Ideelt set bør vi observere opførselen af CPU-ydeevne og derefter dynamisk tune visse aspekter af kernen for at få bedre ydeevne."

En af de stykker, der endnu ikke er udviklet, er dynamisk kontrol af enhederne og de justeringer, der kan foretages i løbet af dens levetid.

"Sig, at vi har al evnen til at modellere alt på forhånd," sagde Lee Harrison, direktør for produktmarketing i Tessent-gruppen på Siemens Digital Industries Software. "Vi har alle skærme indbygget til at gøre tingene i systemet, men det lukker sløjfen. For de nyere geometrier er der stadig en del læring, der skal gøres for virkelig at optimere, hvordan vi kan justere enhedens forskellige parametre for at udvide denne pålidelighed. Det stykke, der lukker sløjfen til in-life-systemet, er, hvor der er en enorm mængde værdi. Alligevel er der stadig arbejde at gøre.

Skiftende ansvarsroller

Kommercielle chiplets tilføjer endnu et vanskeligt problem, som er, hvem der er ansvarlig, når noget uventet observeres eller går galt.

"Hvis jeg er en chipmaker, laver jeg chippen, og jeg kan gå igennem en OSAT til test,” sagde Paul Karazuba, vicepræsident for marketing hos Expedera. ”Jeg kan godt bruge ASE som pakkehus, men jeg sælger det med mit navn og min garanti. Det bliver interessant, når vi har chiplets. På alle vores møder om chiplets bliver der altid rejst spørgsmålet om, hvem der skal have ansvaret for hvad. Lad os sige, at jeg skulle lave en AI-chiplet, og jeg sælger til et system og en pakke med seks andre virksomheders chiplets. Hvilket firma vil være garantien? Hvilket firma vil udføre servicen på det? Der er ingen reel konsensus lige nu."

Arbejdsidéen er, at virksomheden, hvis navn er på ydersiden af pakken, vil være ansvarlig, sagde Karazuba. ”Denne virksomhed bliver nok den, der har et slutansvar for servicen til sine kunder, men det bringer endnu et lag af service ind, som chipletproducenterne skal levere, og det bliver interessant. Frygten er, at omkring 2000, Intel-Microsoft-Dell trekant af alle peger fingre ad hinanden. Det er en uudtalt frygt i branchen lige nu.”

Og måske er det ikke en af chiplets. Hvad sker der, hvis et substrat eller en fysisk sammenkobling er defekt?

"Fra et testsynspunkt kan en chiplet teste udmærket," sagde Karazuba. "Men når der er et fysisk sammenkoblingsproblem, hvordan forstår chipletproducenten det i forhold til multichipmodulproducenten? Det bliver interessant. Den eneste måde at løse disse problemer på er at prøve og fejle. Vi kan designe så mange juridiske kontrakter, som vi vil som halvlederproducenter, men vi er i ukendt farvand her, og tingene bliver nødt til at blive justeret. Supportmodeller bliver nødt til at blive justeret for at afspejle den nye virkelighed med monolitisk silicium, der ikke er det primære køretøj i halvledersalget."

Synopsys' Kapoor har allerede set refleksioner i økosystemet. "Der har altid været økosystemer, men dit aktive økosystem, uanset hvor du er, var måske den næste cirkel omkring det. Hvis du laver design, vil du kun være bekymret over støberiets designregler og designregelmanualen. Det ændrer sig, når man taler om chiplets. Selv med designet tænker du nu på at teste endnu mere, end du nogensinde har gjort før. Du taler til Fordelagtigste , Teradine. Selvom du bare er designer, skal du finde ud af, hvad du skal sætte ind fra et ATPG-synspunkt, og hvordan det skal testes. Den relevante økosystemstørrelse er stigende."

Alligevel har industrien intet andet valg end at løse disse problemer. "Vi har talt om chiplet-markedspladsen. Du vil være i stand til at trække en die ud og have den klar. Det er vi stadig langt væk fra, men trinene bliver tydeligere omkring, hvad vi skal opnå. Forbindelse er grundlæggende. UCIe-standarder er et must, og med det følger protokollerne og reglerne fra et forbindelsessynspunkt, som du skal etablere. Dernæst ville være meget klart definerede modeller. De udfordringer, vi taler om, er påvirket af termik, især, og strøm. Der findes allerede nogle standarder omkring det, og vi vil gå fra tilslutning til den karakteriserede model, så vi kan bruge den mere pålideligt. Så har vi brug for en form for signatur, som er der, hvor vi fra et testbarhedssynspunkt kan se levetiden, og hvordan alle dør kommer til at ændre sig anderledes."

Input til alt dette vil komme fra chip- og systemmonitorer, som også skal være baseret på standarder.

- SEO Powered Content & PR Distribution. Bliv forstærket i dag.

- PlatoAiStream. Web3 Data Intelligence. Viden forstærket. Adgang her.

- Udmøntning af fremtiden med Adryenn Ashley. Adgang her.

- Køb og sælg aktier i PRE-IPO-virksomheder med PREIPO®. Adgang her.

- Kilde: https://semiengineering.com/chiplet-planning-kicks-into-high-gear/

- :har

- :er

- :ikke

- :hvor

- $OP

- 1

- 20

- 30

- 3d

- a

- evne

- I stand

- Om

- fremskynde

- opnå

- aktiv

- faktiske

- faktisk

- tilføje

- tilføjet

- tilføje

- Desuden

- Justeret

- justeringer

- Vedtagelse

- annoncer

- fremskreden

- Luftfart

- aggressive

- Aging

- AI

- Alle

- Alliance

- tillade

- allerede

- også

- altid

- am

- AMD

- beløb

- an

- analyse

- analysere

- ,

- En anden

- enhver

- Anvendelse

- applikationer

- tilgang

- arkitektur

- ER

- omkring

- AS

- udseende

- aspekter

- forbundet

- At

- automotive

- autonom

- autonomt køretøj

- til rådighed

- undgå

- væk

- tilbage

- baseret

- I bund og grund

- BE

- fordi

- bliver

- blive

- været

- før

- Begyndelse

- være

- Tro

- fordele

- BEDSTE

- Bedre

- Big

- Største

- Bit

- Bloker

- board

- både

- Pause

- Bringer

- bred

- bredere

- bygge

- bygget

- Bunch

- bus

- virksomhed

- forretningsudvikling

- men

- .

- købe

- by

- kadence

- kaldet

- CAN

- kapaciteter

- bil

- hvilken

- tilfælde

- tilfælde

- Årsag

- center

- Centers

- Direktør

- vis

- kæde

- udfordre

- udfordringer

- udfordrende

- lave om

- ændret

- Ændringer

- skiftende

- Kapitel

- karakterisere

- kendetegnet

- kontrollere

- Kontrol

- chef

- chip

- Chips

- valg

- valg

- Circle

- klarere

- tydeligt

- Lukker

- lukning

- SAMMENHÆNGENDE

- sammenhængende

- kombineret

- Kom

- kommer

- kommer

- kommerciel

- Virksomheder

- selskab

- komplekse

- kompleksitet

- kompliceret

- komponenter

- Konceptet

- begreber

- Bekymring

- pågældende

- Konference

- Tilslut

- tilsluttet

- Connectivity

- Konsensus

- Overvej

- overvejelse

- sammenhæng

- kontinuerlig

- kontinuerligt

- kontrakter

- kontrast

- kontraster

- kontrol

- samtaler

- Core

- Koste

- kunne

- dækker

- CPU

- CRC

- Medvirkende

- afgørende

- Nuværende

- Kunder

- tilpassede

- cykler

- data

- Data Center

- datacentre

- Datoer

- dag

- deal

- debat

- årti

- beslutte

- dedikeret

- dyb

- definerede

- tæthed

- afhængig

- Afhængigt

- Design

- konstrueret

- Designer

- designere

- designe

- ønskes

- udviklet

- Udvikling

- enhed

- Enheder

- DID

- Die

- forskellige

- svært

- digital

- Direktør

- forsvinder

- diskussion

- diskussioner

- distribuere

- do

- gør

- gør

- færdig

- Dont

- ned

- kørsel

- i løbet af

- dynamisk

- dynamisk

- dynamik

- hver

- nemt

- økosystem

- økosystemer

- indsats

- emerge

- muliggøre

- aktivering

- ende

- nok

- sikre

- Hele

- enhed

- Miljø

- fejl

- især

- etablere

- ejendom

- etc.

- Endog

- begivenhed

- begivenheder

- NOGENSINDE

- alle

- at alt

- eksempel

- udførelse

- eksisterer

- eksisterer

- dyrt

- ekspert

- forklarede

- eksport

- udvide

- øje

- stof

- faktorer

- svigtende

- Manglende

- langt

- Mode

- frygt

- få

- Fig

- Figur

- Fisk

- passer

- fast

- Fokus

- Til

- Tving

- Forces

- frem

- Foundry

- fra

- forsiden

- funktion

- funktioner

- fundamental

- Fundamentals

- Gear

- få

- få

- given

- Go

- mål

- Goes

- gå

- godt

- stor

- stærkt

- gruppe

- Gruppens

- hånd

- ske

- Happening

- sker

- Have

- have

- he

- Helse

- link.

- Høj

- Høj frekvens

- stærkt

- historie

- hus

- Hvordan

- How To

- Men

- HTTPS

- kæmpe

- i

- ICS

- idé

- ideal

- if

- umiddelbar

- KIMOs Succeshistorier

- påvirket

- implementeret

- vigtigt

- umuligt

- Forbedre

- forbedringer

- in

- omfatter

- Herunder

- stigende

- uafhængig

- individuel

- industrier

- industrien

- Infrastruktur

- i første omgang

- indgange

- integrere

- integration

- integritet

- interagere

- interaktioner

- interessant

- interne

- ind

- indføre

- IP

- spørgsmål

- spørgsmål

- IT

- ITS

- lige

- Kapoor

- Nøgle

- Kicks

- Venlig

- Kend

- kendt

- Lane

- Sprog

- stor

- senere

- Lov

- lag

- Layout

- føre

- førende

- læring

- mindst

- Lee

- Politikker

- Niveau

- livscyklus

- levetid

- levetid

- ligesom

- Line (linje)

- LINK

- Lang

- længere

- leder

- Lot

- Lav

- lavet

- Mainstream

- større

- lave

- maker

- Makers

- Making

- ledelse

- leder

- manuel

- fremstillet

- mange

- Marked

- Marketing

- markedsplads

- modne

- max-bredde

- Kan..

- måle

- mekanismer

- møder

- metoder

- måske

- Mission

- tilstand

- model

- modeller

- modul

- Moduler

- Overvåg

- overvågning

- skærme

- Monolithic

- måned

- mere

- flytning

- meget

- flere

- skal

- my

- navn

- Behov

- behov

- netværk

- Ny

- næste

- ingen

- noder

- bemærkede

- nu

- nummer

- observere

- of

- off

- on

- ONE

- igangværende

- kun

- åbent

- operationelle

- optimal

- Optimer

- Indstillinger

- or

- ordrer

- organisationer

- Andet

- Andre deltagere

- Andre

- vores

- ud

- uden for

- i løbet af

- samlet

- Overvind

- egen

- pakke

- emballeret

- emballage

- panel

- parametre

- del

- deltagere

- særlig

- især

- partnere

- dele

- forbi

- paul

- ydeevne

- perspektiv

- fysisk

- Fysisk

- pick

- billede

- stykke

- stykker

- pipeline

- Steder

- planlægning

- plato

- Platon Data Intelligence

- PlatoData

- spillere

- Punkt

- Synspunkt

- Populær

- portefølje

- mulig

- potentiale

- magt

- Forudsigelig

- præsident

- trykke

- Forebyggelse

- tidligere

- primære

- Forud

- sandsynligvis

- Problem

- problemer

- processorer

- Produkt

- Profil

- Forslag

- protokol

- protokoller

- give

- offentlige

- sætte

- Sætte

- Qualcomm

- kvalitet

- spørgsmål

- hævet

- Læs

- klar

- ægte

- fast ejendom

- Reality

- virkelig

- grund

- nylige

- anerkendt

- afspejler

- Reflektioner

- registre

- relativt

- relevant

- pålidelighed

- reparere

- gentagelig

- indberette

- kræver

- påkrævet

- Krav

- elastisk

- svar

- reaktioner

- ansvar

- ansvarlige

- REST

- højre

- robusthed

- roller

- Herske

- regler

- Said

- salg

- siger

- siger

- siger

- Scale

- skalering

- scanne

- ordninger

- Skole

- Skærm

- se

- set

- segment

- sælger

- Salg

- halvleder

- senior

- sensorer

- tjeneste

- sæt

- flere

- Hylde

- skifte

- bør

- vist

- side

- Signal

- signaler

- signifikant

- betydeligt

- Silicon

- lignende

- enkelt

- SIX

- Seks måneder

- Størrelse

- størrelser

- færdigheder

- langsommere

- lille

- mindre

- smartphone

- So

- Software

- Løsninger

- SOLVE

- Løsning

- nogle

- noget

- Kilde

- Kilder

- Space

- højttalere

- særligt

- specs

- spekulative

- hastighed

- tilbringe

- Presse

- stable

- standard

- standarder

- påbegyndt

- Steps

- Stadig

- butik

- succes

- vellykket

- sådan

- sagsøge

- leverandører

- support

- Symposium

- systemet

- Systemer

- Tag

- tager

- Tal

- taler

- rettet mod

- teknikker

- Teknologier

- vilkår

- prøve

- Test

- end

- at

- deres

- Them

- selv

- derefter

- teori

- Der.

- termisk

- Disse

- de

- ting

- ting

- Tænker

- denne

- dem

- selvom?

- Gennem

- tid

- til

- i dag

- sammen

- mod

- spore

- Kurser

- overførsel

- retssag

- prøve og fejl

- tsmc

- typisk

- forstå

- undervejs

- Uventet

- enestående

- us

- brug

- anvendte

- Værdifuld

- værdi

- forskellige

- køretøj

- sælger

- leverandører

- versus

- lodret

- lodret

- meget

- Vice President

- Specifikation

- vente

- Venter

- ønsker

- var

- Fiskevande

- Vej..

- måder

- we

- GODT

- gik

- Hvad

- Hvad er

- hvornår

- hvorvidt

- som

- mens

- WHO

- Hele

- hvis

- udbredt

- vilje

- villig

- trådløs

- med

- inden for

- Arbejde

- arbejde sammen

- arbejder

- værksted

- world

- ville

- Forkert

- endnu

- dig

- Din

- zephyrnet