Nye bump-strukturer bliver udviklet for at muliggøre højere sammenkoblingstætheder i flip-chip-emballage, men de er komplekse, dyre og stadig sværere at fremstille.

For produkter med høje pin-tal, flip-chip [1] pakker har længe været et populært valg, fordi de udnytter hele formområdet til sammenkobling. Teknologien har været i brug siden 1970'erne, startende med IBM's C4 (controlled collapse chip connection), men den kom virkelig i udbredt brug i 1990'erne.

Siden da har bump-teknologien udviklet sig til at håndtere stigende strøm- og signalforbindelsestæthed, der kræves af hukommelse, højtydende databehandling og mobile computerenheder. At imødekomme denne efterspørgsel kræver ny sammenkoblingsteknologi, der muliggør mindre bump pitches, som i øjeblikket er i produktion.

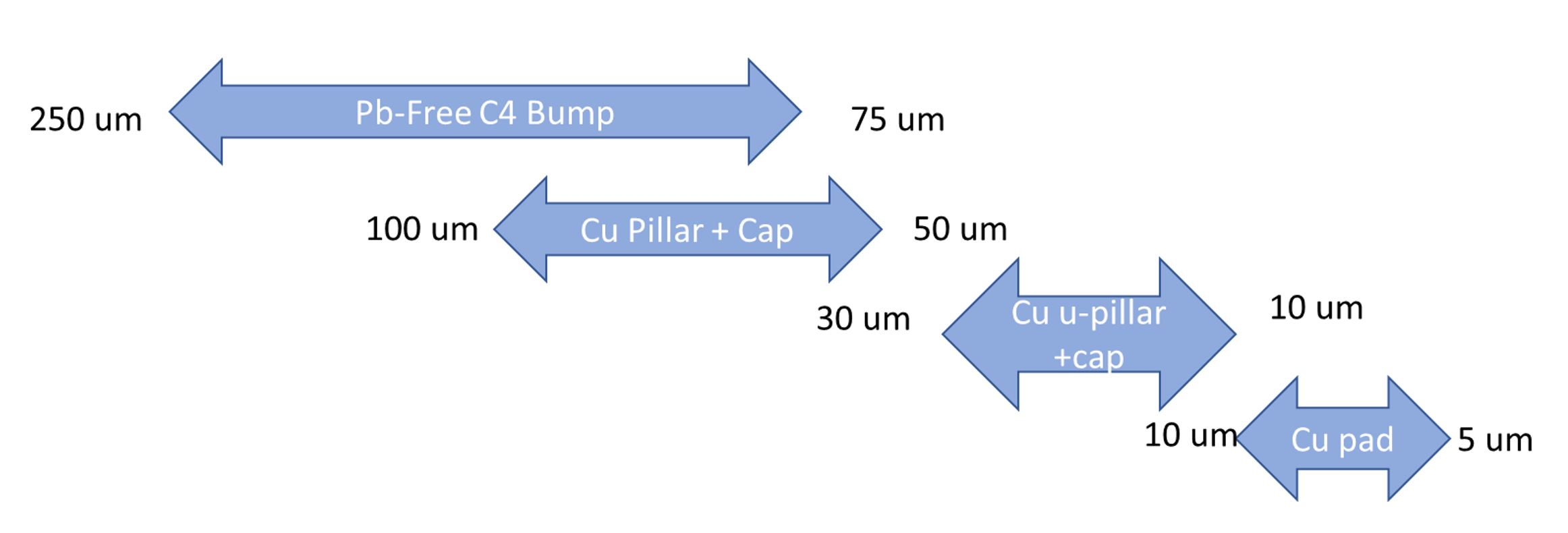

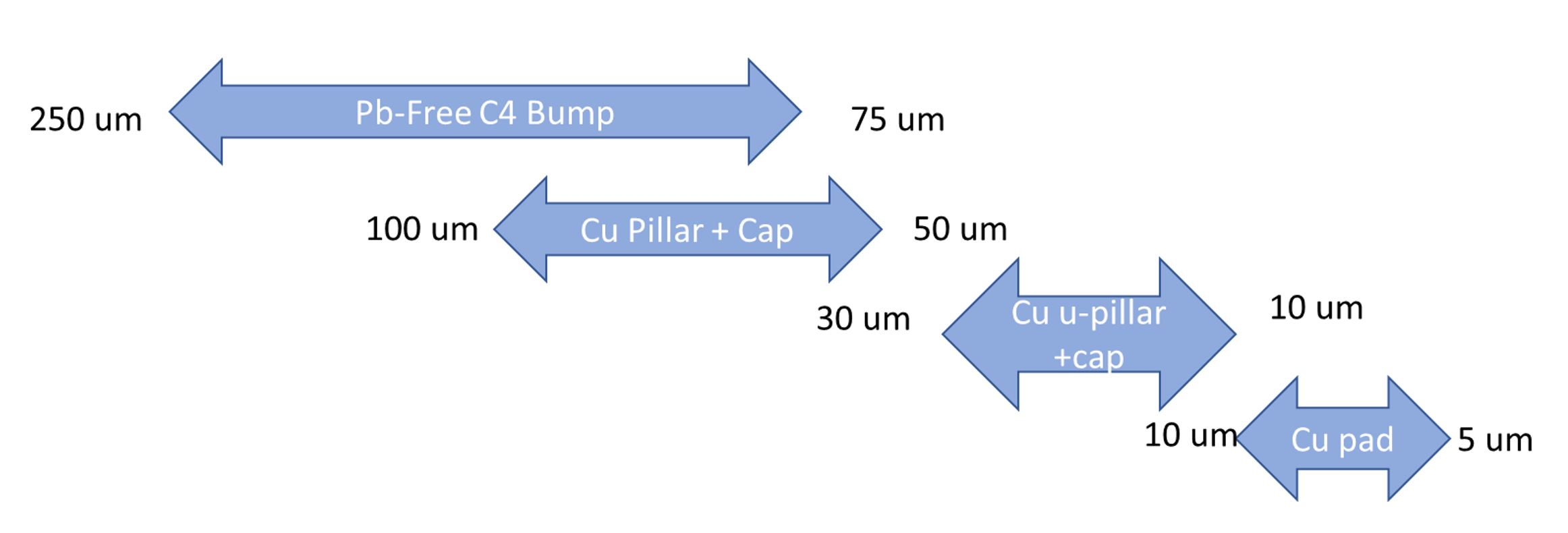

Set over tid udvikler køreplanen for flip-chip-sammenkobling sig fra blyfri bumps til kobbersøjler og derefter til kobbermikrobumps. Pitchstørrelser fortsætter med at krympe, hvilket igen har skabt produktionsudfordringer for stød og limning.

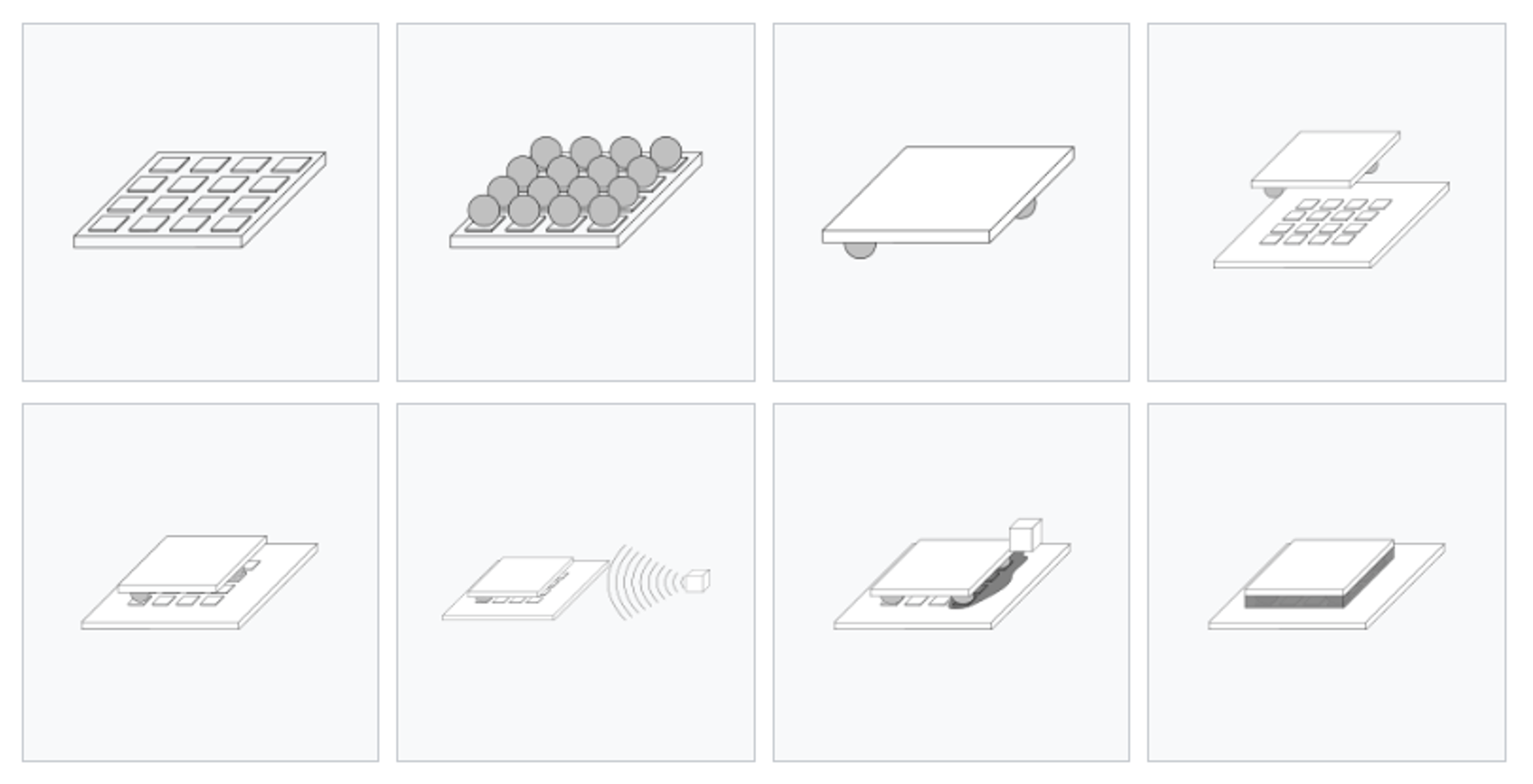

Fig. 1: Flip-chip teknologi pitch områder. Kilde: A. Meixner/Semiconductor Engineering

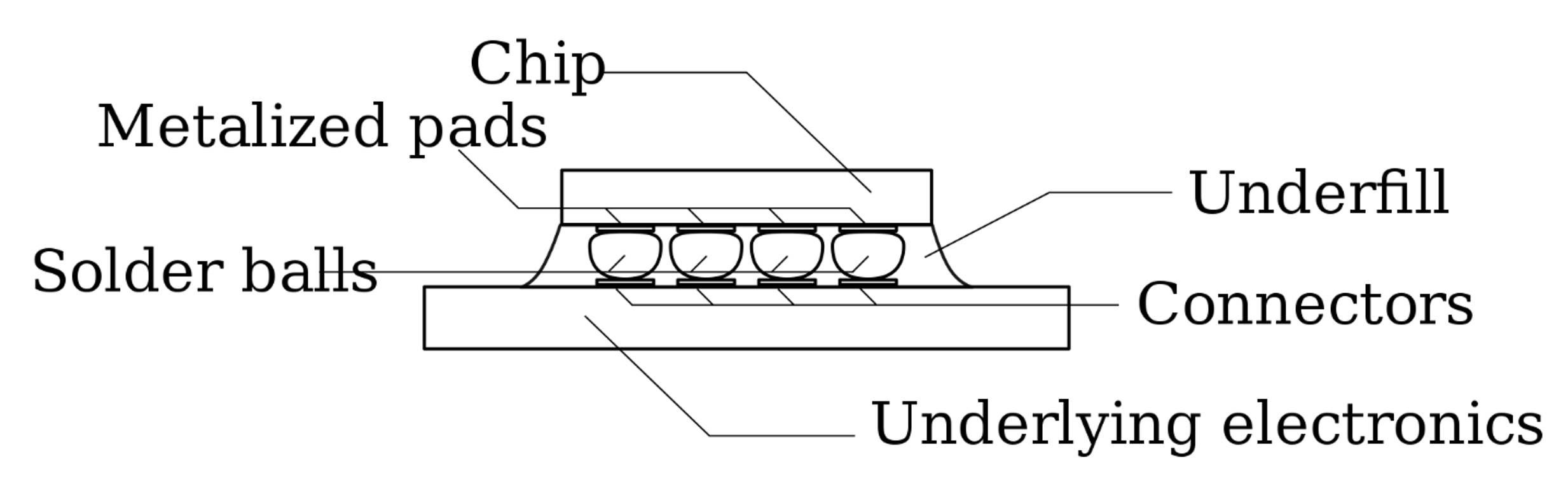

Fig. 2: Flip-chip komponenter. Kilde: Wikipedia

"I flip-chip-arenaen - 250 mikron pitch og derunder - var det oprindeligt tin-bly bump, og et af de store træk var at blive blyfri. Men når du begynder at nå 100 mikron eller derunder, begynder du at se mere af en kobbersøjle, selvom der er et overlap, da vi ser kobbersøjler op til 250 mikron,” sagde Jeff Schaefer, senior procesingeniør hos Promex Industries. "Med 250 mikron pitch ser vi 130 mikron bump størrelser eller kobber søjle diametre. Når vi kommer omkring 100 mikron pitch, er det 80 mikron diameter. Den mindste, jeg har set, er en 62.5 mikron pitch med en 40 mikron søjle. Jeg forventer at begynde at se 50 mikron pitch snart."

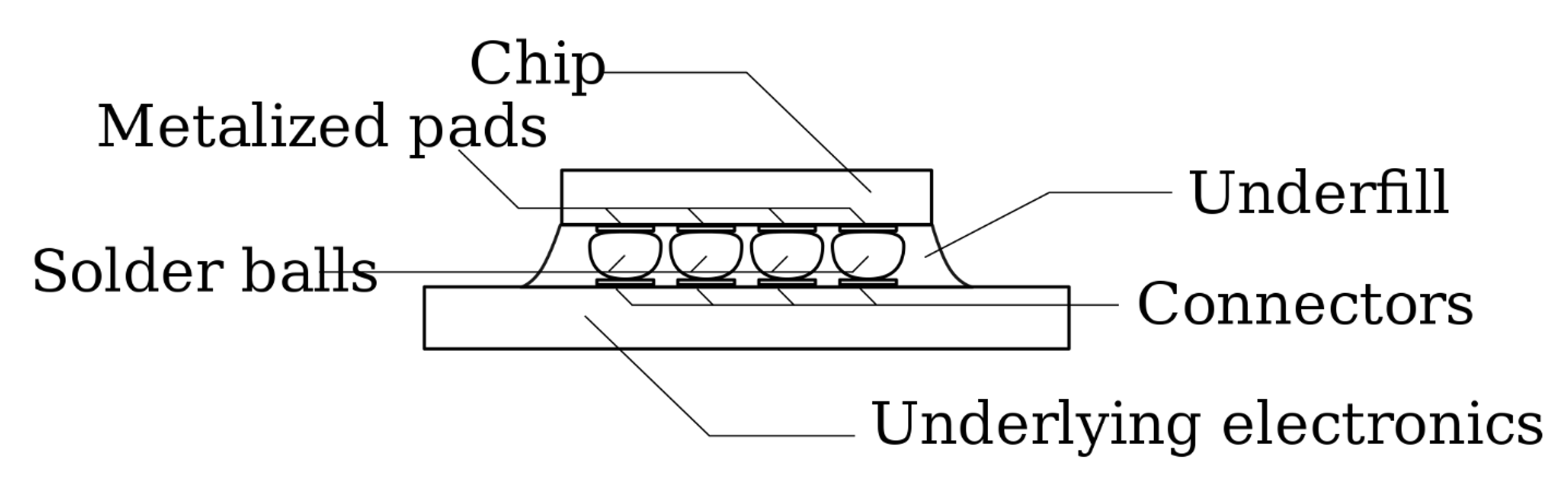

Den grundlæggende flip-chip-proces begynder efter kredsløbsfremstilling, når metalpuder skabes på matricens overflade for at forbinde til I/O'erne. Dernæst kommer wafer bumping, hvor en loddekugle er afsat på hver pude. Waferen skæres derefter i tern, og disse matricer vendes og placeres, så loddekuglerne flugter med substratpuderne. Loddekuglerne smeltes/gennemstrømmes derefter, typisk ved brug af varmluft, og en monteret matrice underfyldes med et elektrisk isolerende klæbemiddel, sædvanligvis ved hjælp af kapillarvirkning. [1]

Fig. 3: Flip-chip fremstillingsproces. Kilde: Wikipedia

At flytte til en kobbersøjle eller mikrobump kræver litografi for at skabe disse strukturer.

"Kobbersøjle bruges generelt under 130 µm pitch, fordi i stedet for at være en cirkulær loddebule, er kobbersøjlen for det meste en Cu-stolpe med lodde på toppen," sagde Doug Scott, senior vice president for wafer level packaging hos Amkor-teknologi. "Dette gør det muligt at placere kobbersøjle-bumpene tættere sammen uden risiko for, at loddet forbindes sammen under samlingsreflow - generelt ~40 µm Cu + ~25 µm."

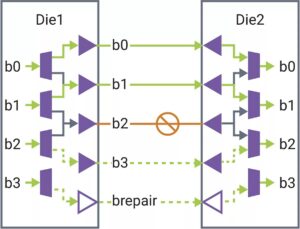

Der er også variationer på temaet. "Microbump, som er et almindeligt begreb, der bruges, hvor du har en sammenkobling mellem silicium-til-silicium, er lidt anderledes, fordi CTE (koefficienten for termisk udvidelse) generelt er den samme," sagde Mark Gerber, seniordirektør for ingeniør/teknisk markedsføring på ASE Gruppen. "Nogle af de generelle designregler, der bruges til kobbersøjler, er de samme, men den flade overfladetopografi og samlinger med lav belastning giver mulighed for fleksibilitet af den underfyldning, der bruges. Dette kan også drive den enkelte bump pitch. I dag er en 35 µm bump fuld-array pitch mulig, på grund af de førnævnte routingovervejelser, for den wafer-niveau eller fab-niveau routing, der bruges."

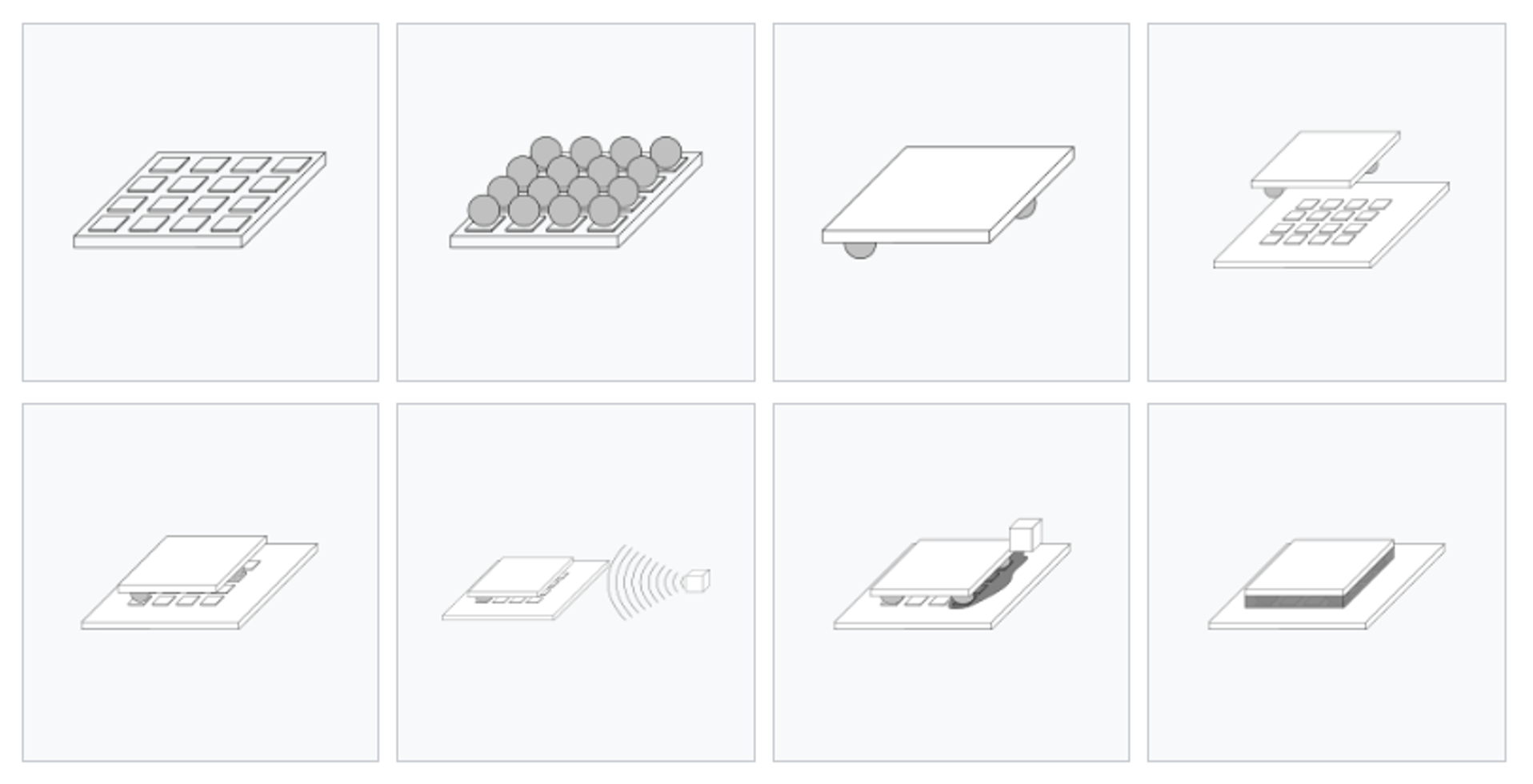

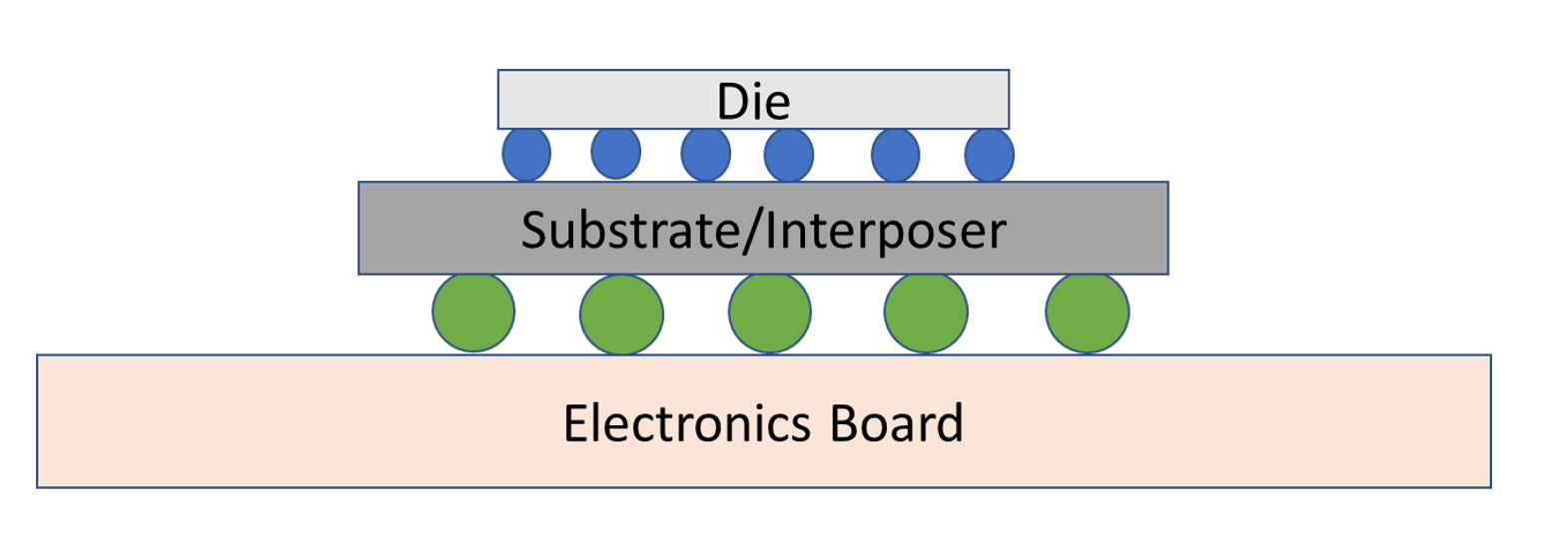

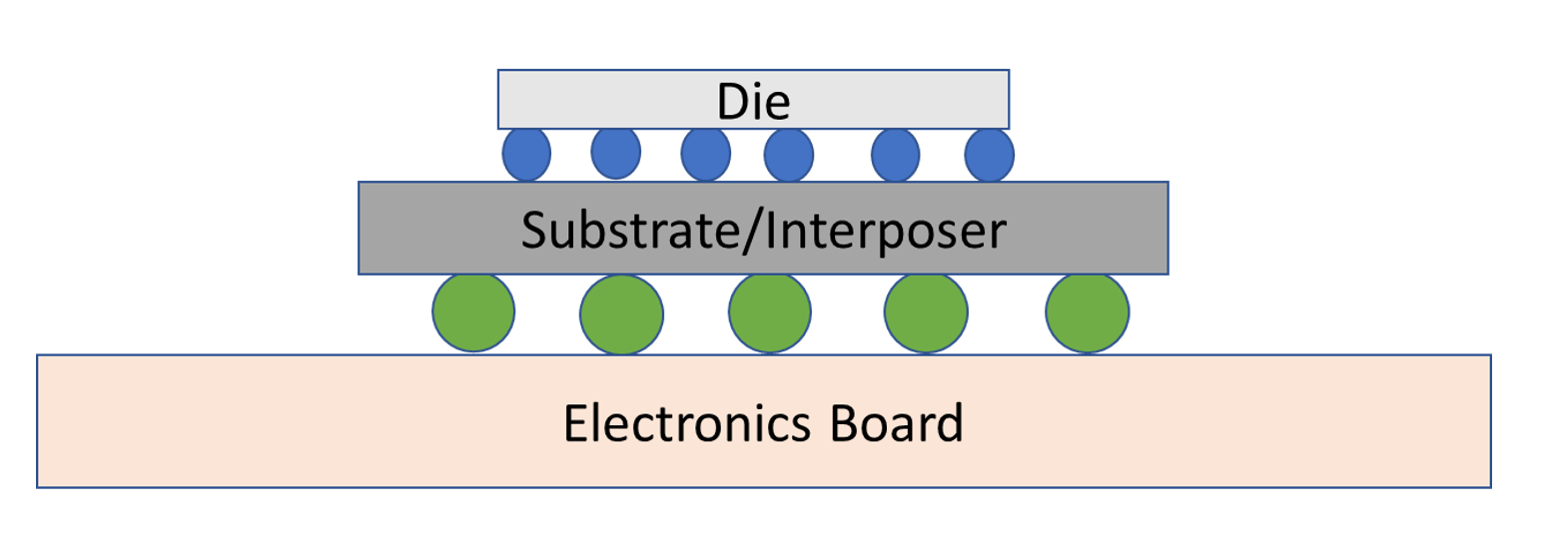

The Heterogeneous Integration Roadmap [2] beskriver alle aspekter af emballering, inklusive die-til-substrat-forbindelser lige fra wire-bonds til through-silicium vias. Med flip-chip-pakker spiller die-til-substrat-sammenkoblinger, substratomfordelingsområder og substrat-til-kort-sammenkoblinger alle en rolle i fremstillingsgrænserne.

Fig. 4: Konceptuelt diagram af flip-chip emballage. Kilde: A. Meixner/Semiconductor Engineering

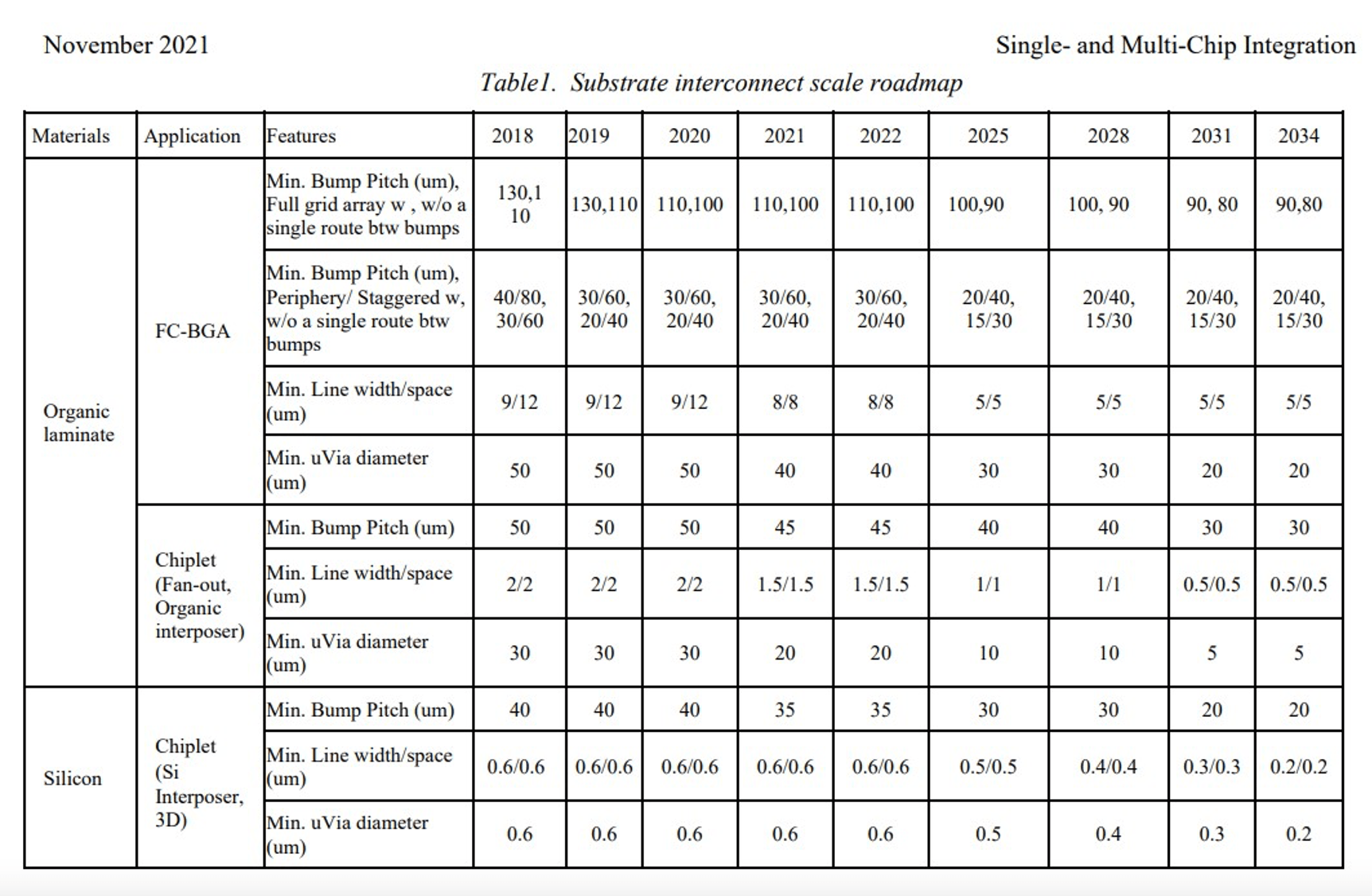

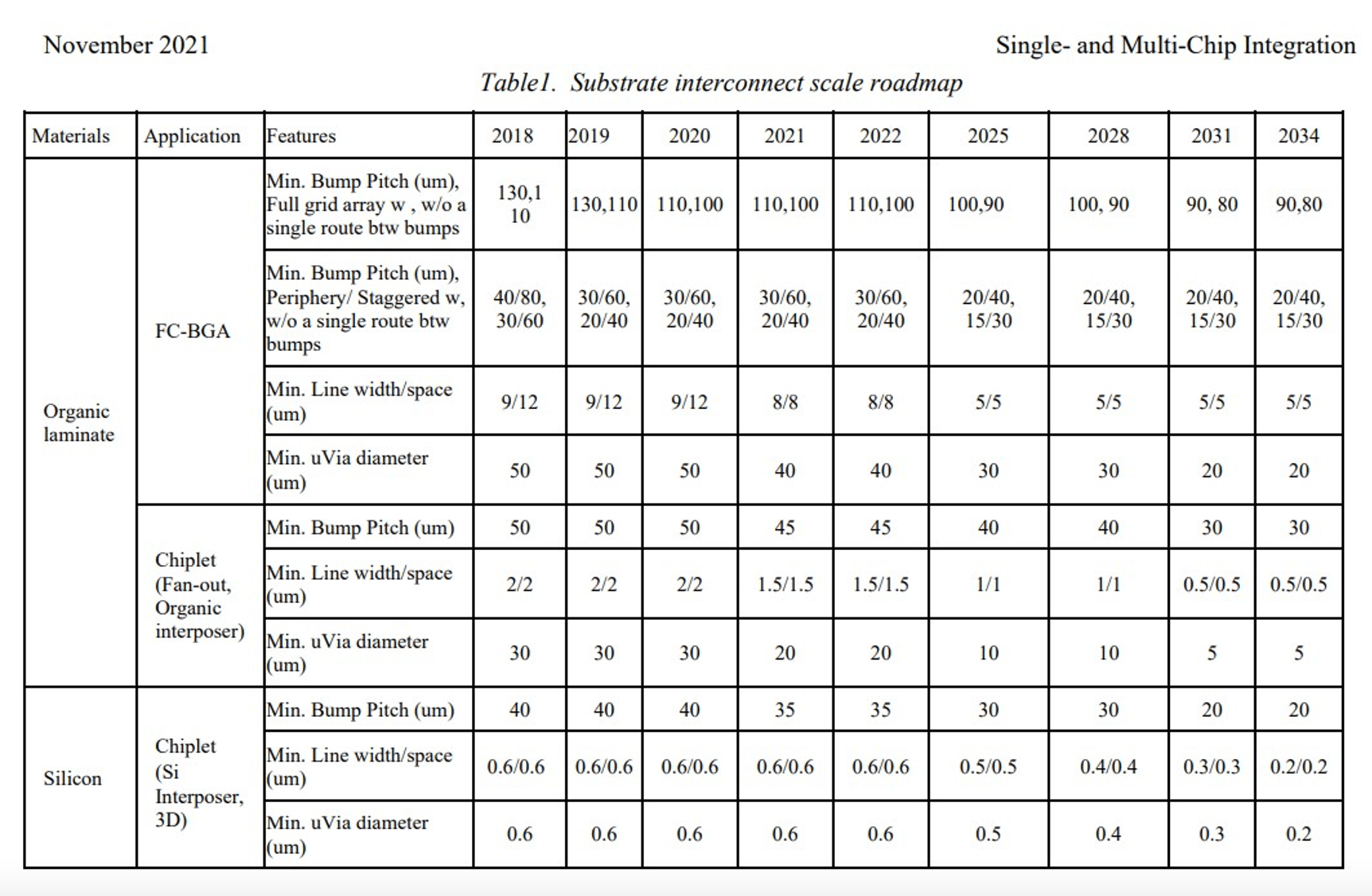

Kapitel 8 i heterogene integrations-køreplan [3] dokumenterer landskabet af nuværende og forventede emballageteknologi-pitch. Den mindste tonehøjde for hver flip-chip-sammenkoblingsteknologi er vist i tabel 1 i underafsnit 8.7 (side 41).

![Kapitel 8 i heterogene integrations-køreplan [3] dokumenterer landskabet af nuværende og forventede emballageteknologi-pitch. Den mindste tonehøjde for hver flip-chip-sammenkoblingsteknologi er vist i tabel 1 i underafsnit 8.7 (side 41).](https://platoaistream.com/wp-content/uploads/2023/05/challenges-grow-for-creating-smaller-bumps-for-flip-chips-7.png)

![Kapitel 8 i heterogene integrations-køreplan [3] dokumenterer landskabet af nuværende og forventede emballageteknologi-pitch. Den mindste tonehøjde for hver flip-chip-sammenkoblingsteknologi er vist i tabel 1 i underafsnit 8.7 (side 41).](https://platoaistream.com/wp-content/uploads/2023/05/challenges-grow-for-creating-smaller-bumps-for-flip-chips-8.png)

Den tilsvarende tabel for sammenkobling af substrat (den del, der forbinder pakke til print) findes i underafsnit 8.8 (side 43).

Med hver ændring i sammenkoblingsteknologi kommer nye processer og deres begrænsninger, som driver innovation, udbyttestyring og fejlinspektion.

Bumping teknologi grænser

Bumping-teknologi måles ved pitch, størrelse, højde og elektriske og mekaniske egenskaber. Termiske overvejelser varierer afhængigt af materialets CTE-uoverensstemmelse. Forvridning er et problem for større matricer og wafers, som forværres af tilbageslibning af en wafer før matricen fastgøres.

"Der er en række drivere til pitch-begrænsninger for hver type sammenkobling," sagde ASE's Gerber. "Begyndende med traditionel loddebump flip chip interconnect bestemmes pitch-kapaciteten af kollapshøjde for underfill, capture pad pitch for trace routing, capture pad pitch for bump-to-bump short risiko og flere andre pitch-relaterede følsomheder. Den forudmonterede bump-højde har en defineret højde, men som IBM definerede C4-begrebet - Controlled Collapse Chip Connection - vil diameteren af loddebulen og capture pad-størrelsen bestemme "kollapsen eller den endelige højde" af sammenkoblingen. Dette er den vigtigste pitch-begrænsende faktor for brug af loddebuler relateret til pitch."

Bumphøjden bestemmes af design, men også forarbejdningsvalg.

"For standardbelagte loddebuler og kobbersøjlebuler er bumphøjder før montering generelt omkring 70 µm til 75 µm, med kollapsede bump-højder efter samling på ~50 µm for at give mulighed for x, y, z plads til underfyldningsflow mellem bumpene. Microbumps vil have meget lavere bump højder og involvere plettering meget mindre lodde. Specifikt kan mikrobump være mindre end 10 µm høje med reducerede Cu- og loddehøjder afhængigt af stigning og endebehov,” sagde Amkors Scott. "Standardbelagte loddebuler bruges generelt på afstande fra 130 µm til 250 µm. Under 130 µm er der ikke nok xy mellemrum mellem bump, når man starter med en 70µm pre-assembly bump højde.”

At skabe kobbersøjler kræver flere behandlingstrin end loddebuler.

“Da vi gik over til die-to-die-verdenen, var teknologien anderledes, fordi nu har du at gøre med en wafer, og planeritterne er så gode sammenlignet med die til substrat. Først laver du kobbersøjlen, på den første wafer, der skal få loddet eller kobbersøjlen, er der først et under bump metal (UBM). Det er en lille hætte over åbningen, der går ned i silicium. Så bygger vi en kobberkerne af den og sætter så en blikhætte på den. Så så ser den modtagende wafer ud, som om de har en UBM-pude der, og den har normalt noget nikkelguld-belægning på, så den er flot og uberørt,” forklarede Promex Industries' Schaefer. Så i stedet for at have en lille fordybning som et laminatsubstrat, har du en let ekstrudering. Vi har fundet ud af, at vi faktisk er i stand til at lodde dem våde uden "lodde på puden." Det er sådan, de er designet og bygget. Den fungerer næsten som en loddeplade og en pude, fordi den er en lille kuppel i modsætning til at prøve at komme ned i et hul."

Fotolitografiske trin, der er nødvendige for Cu-søjledannelse, kommer med begrænsninger såvel som substratdesignreglerne.

"For kobbersøjle, som består af en kobberstolpe og en loddehætte ved spidsen, kan kobberstolpens højde defineres til begrænsningen af en eller flere fotoresistlagtykkelser, og når du reducerer stigningen, vil billedformatet af cu stolpehøjde til pitch bliver begrænsningen sammen med fotoresistmaterialet og billedværktøjets muligheder,” sagde Gerber. "En sekundær begrænsning for kobbersøjleforbindelsen er de anvendte substratdesignregler. For fin pitch >110um pitch anvendes 2 primære metoder- BOT (Bond on Trace) eller ET – Embedded Trace, hvor loddehætten på kobbersøjlen placeres oven på traceen i stedet for en traditionel capture pad. Størrelse og form af kobbersøjler, inklusive begrænsningerne ovenfor, kan udgøre en grænse for mulighederne og køreplanen for at fortsætte med at skrumpe pladserne. Mange af disse begrænsninger skyldes evnen til at dirigere spor mellem søjlerne på substratsiden. Efterhånden som nye teknologier er tilgængelige, såsom RDL på wafer-niveau, vil interconnect-køreplanerne blive skubbet yderligere, men stadig med begrænsninger omkring højde/formatforholdet for fremstillingsprocesser såsom underfill."

Andre er enige om, at underfyldningsprocessen kommer med udfordringer. “Når du får finere tonehøjde, bliver mindre bump, de bliver kortere. Det bliver nu svært at finde underfyldninger til at komme nedenunder. Underfyldene er historisk blevet designet til at komme under et mellemrum på 5 mil, og nu kommer de ned til 3 mil, hvilket er 75 mikron,” sagde Schaefer. "Nu begynder vi at se 60 og 25 mikron huller. Jeg er sikker på, at folk arbejder på nye underfyldninger. Men der er mange ting at arbejde på. For det første, efterhånden som du får finere partikler, bliver det mere som et slam, hvilket gør det sværere at flyde. Dette er en vejspærring, der skal fjernes."

Håndtering af udbytte

Efterhånden som bumping-teknologien bliver mindre, åbner yderligere behandlingstrin - for eksempel litografi til at skabe kobbersøjler - nye muligheder for udbyttedetektorer. For en vellykket bindingsproces er partikler, overfladeforurenende stoffer og loddepudsning problematiske for udbyttet. Disse kræver proceskontrol, metrologi og inspektion.

Der kræves naturligvis kontrol af forurening. "Tier 1 OSAT'er investerer for at reducere niveauet af fabrikkens kontamineringskilder og derfor reducere defektprocenterne," sagde Amkors Scott. "Pitch bidrager ikke til defekt. Lignende niveauer af defekt eksisterer uanset tonehøjde."

Men pitch tilføjer nogle af sine egne udfordringer. "Efterhånden som stigningen bliver mindre, og bumpens størrelse reduceres, er håndtering af partikelforurening meget vigtig. For andre typer sammenkoblinger såsom hybrid bonding, hvor afstande er reduceret til under 30µm, og overflade-til-overflade kontakten er vigtig, er wafer-baseret renrumsmiljø afgørende for udbyttet,” sagde ASE's Gerber.

Forberedelse til underfyldningsprocessen skal heller ikke undervurderes.

"Generelt med et laminat vil du lave en underfill, efter du har lavet flip-chippen," sagde Promex's Schaefer. "Vi bestemmer, hvor vi vil placere den, og hvordan den skal omformes. Vi renser det for at få alt flusmateriale ud under mellemrummet mellem matricen og underlaget. Så underfylder vi med en epoxy, der flyder. Den er designet til at blive våd og ikke efterlade hulrum og den slags ting. Men der er en udfordring, når vi kommer til finere baner. Ujævnheder bliver lidt kortere, og efterhånden som de bliver kortere, bliver afstanden mellem chip og underlag mindre, så det er sværere at rengøre. Forestil dig at stikke to glasglas sammen for at prøve at få snavset ud mellem dem."

Metrologi og inspektionsbehov

Til styring af proceskontrol og udbytte spiller metrologi- og inspektionsværktøjer en vigtig rolle. "Der er tilgængelige værktøjer på markedet, som kan hjælpe med at give vejledning om interconnect-integritet, ud over tværsnitsanalyse i processen, der bruges ved opsætning og ved definerede produktionsintervaller," sagde ASE's Gerber.

Bumping-processen og bindingsprocesserne har hver især specifikke karakteristika, som skal overvåges. For bump fokuserer metrologi på diameter, højde og co-planaritet. Mindre pladser kræver mere stringent kontrol af bumpdiameter og højdekontrol. På samme måde bliver vinduet for co-planaritet mindre, når bumphøjden krymper. Typisk er 10 % variation tilladt. For eksempel resulterer en bumphøjde på 30 µm i en tilladt variation på ±3 µm. At overskride dette bidrager til mislykket eller dårlig binding.

"Binding udføres normalt med masse-reflow-ovne," sagde Mike Kelly, vicepræsident for avanceret pakke- og teknologiintegration hos Amkor. "Den indledende karakterisering af reflow-processen er etableret ved hjælp af shadow-moire til at kvantificere forvridningen under reflow, og temperaturkortlægning af ovnene for at sikre ensartet temperaturkontrol af selve flip-chip-delen. Under opsætning, mekanisk dyseløft og inspektion for at sikre god loddebefugtning. Flux påføres også sædvanligvis med en 'dip-flux', hvor støbebulene 'dyppes' ned i tynde, stramt kontrollerede fluxreservoirer. Visuel inspektion af disse genstande udføres på stikprøvebasis."

Øget automatisering af visuel inspektion reducerer afhængigheden af, at operatører ser et billede og træffer en beslutning. Den eksponentielle stigning i bump-forbindelserne er én driver. Ændringer i bindingsprocesser giver en anden. En selvjusteret loddegenstrømningsproces er en moden teknologi. Med den termiske kompressionsbinding, der almindeligvis anvendes i avanceret emballage, er der pålidelighedsmekanismer, der består elektrisk test. Det beder til gengæld brugen af røntgeninspektion og metrologiværktøjer til at se bumpene efter limning.

"For emballage med lav kompleksitet kunne faciliteter slippe af sted med en operatør og manuelt inspicere. For en del med 100 bump er denne metode gennemførlig. Ved 1,000 bump er det bestemt en belastning. Når en del har 10,000 bump, er der ingen chance. Vi går ud over dette punkt, og vi er nødt til at gå videre til den næste metode,” bemærkede Frank Chen, direktør for applikationer og produktstyring hos Bruker. "Kvaliteten og kompleksiteten går hånd i hånd, for når du forsøger at gøre noget mere komplekst, vil dit udbytte blive påvirket, og der vil være behov for noget nyt værktøj. Og værktøj betyder både procesværktøjer og metrologiværktøjer, så begge skal avanceres parallelt. Fra vores egne undersøgelser kan vi se, at når du først har nået de 1,000 bump, så skal du begynde at tænke 'Min manuelle teknik er utilstrækkelig, og jeg har brug for noget nyt'.”

En række inspektions- og metrologiværktøjer er tilgængelige for at understøtte pakkefremstilling.

”Der er flere metoder, der kan eller bør bruges til at opnå processtyring. Først traditionel 2D-inspektion (AOI) for 100 % overfladedefektinspektion pr. procesflow (dvs. IQC, OQA, foto, rensning, plettering osv.) Dernæst kan 2D-metrologi (AOI) bruges til at kontrollere bumpstørrelse og diameterstørrelse styring. Ydermere kan 3D-metrologi (AOI) bruges til en sampling af bump højde/co-planaritet metrologisk informationsindsamling (dette udføres typisk med en lasertrianguleringsbaseret teknologi),” sagde Nathan Peng, produktmarketingchef hos På innovation. "Yderligere kan 3D-metrologi målrette individuelle bumphøjdekarakteristika, typisk indsamlet med interferometerteknologi med hvidt lys. Der er også metoder til at muliggøre detektion af organiske rester på bump-toppen, der kan føre til fejl med bump-to-pad-forbindelse."

Konklusion

Produkter, der kræver højere sammenkoblingstal, fortsætter med at drive samtrafikkøreplanen. Hver flip-chip-teknologi har produktionsgrænser, der involverer materialeegenskaber, krympende størrelser, der udfordrer underfill-teknologier, og øget brug af litografi til at skabe sammenkoblingsstrukturerne. Enhver ændring i limningsprocesser resulterer i en stigning i metrologi- og inspektionstrin for at opfylde udbytte- og kvalitetsmål.

Referencer

- https://en.wikipedia.org/wiki/Flip_chip

- https://eps.ieee.org/technology/heterogeneous-integration-roadmap/2021-edition.html

- HIR Kapitel 8 Single Chip og Multi Chip Integration, https://eps.ieee.org/images/files/HIR_2021/ch08_smcfinal.pdf

Relaterede historier:

Bump Co-planaritet og uoverensstemmelser forårsager udbytte, pålidelighedsproblemer

Avancerede emballageudfordringer vokser, efterhånden som chips og pakkestørrelser krymper; forskelligt udstyr vinder teknologier indpas.

Bump-pålidelighed er udfordret af latente defekter

Automatiserede løsninger er på vej, men de vil tage tid at udvikle.

Store ændringer forude i strømforsyning, materialer og sammenkoblinger

Hvordan produktion og emballering vil ændre sig i løbet af de næste par årtier.

- SEO Powered Content & PR Distribution. Bliv forstærket i dag.

- PlatoAiStream. Web3 Data Intelligence. Viden forstærket. Adgang her.

- Udmøntning af fremtiden med Adryenn Ashley. Adgang her.

- Køb og sælg aktier i PRE-IPO-virksomheder med PREIPO®. Adgang her.

- Kilde: https://semiengineering.com/challenges-grow-for-creating-smaller-bumps-for-flip-chips/

- :har

- :er

- :ikke

- :hvor

- $OP

- 000

- 1

- 10

- 100

- 250

- 2D

- 3d

- 40

- 7

- 8

- a

- evne

- I stand

- over

- opnå

- erhvervelse

- Handling

- handlinger

- faktisk

- Desuden

- Yderligere

- Tilføjer

- fremme

- fremskreden

- Efter

- forude

- LUFT

- tilpasse

- Alle

- tillade

- tillader

- sammen

- også

- an

- analyse

- ,

- En anden

- enhver

- applikationer

- anvendt

- ER

- OMRÅDE

- områder

- omkring

- AS

- udseende

- aspekter

- Assembly

- At

- vedhæfte

- Automation

- til rådighed

- væk

- tilbage

- bold

- grundlæggende

- grundlag

- BE

- fordi

- bliver

- været

- før

- være

- jf. nedenstående

- mellem

- Beyond

- Big

- board

- obligation

- Bot

- både

- bygge

- bygget

- men

- by

- kom

- CAN

- kasket

- kapaciteter

- fange

- Årsag

- udfordre

- udfordret

- udfordringer

- chance

- lave om

- Ændringer

- Kapitel

- karakteristika

- chen

- chip

- Chips

- valg

- valg

- tættere

- Bryder sammen

- kollapsede

- Kom

- kommer

- Fælles

- almindeligt

- sammenlignet

- komplekse

- kompleksitet

- komponenter

- computing

- konceptuelle

- Bekymring

- Tilslut

- Tilslutning

- tilslutning

- Tilslutninger

- forbinder

- overvejelser

- konsekvent

- kontakt

- kontaminanter

- fortsæt

- fortsættende

- bidrage

- kontrol

- kontrolleret

- styring

- kontrol

- Kobber

- Core

- Tilsvarende

- kunne

- Par

- skabe

- oprettet

- Oprettelse af

- kritisk

- Nuværende

- For øjeblikket

- data

- beskæftiger

- årtier

- beslutning

- definerede

- definitivt

- levering

- Efterspørgsel

- tæthed

- Afhængigt

- deponeret

- Design

- konstrueret

- Detektion

- Bestem

- bestemmes

- udvikle

- udviklet

- Enheder

- Die

- forskellige

- svært

- Direktør

- snavs

- do

- dokumenter

- gør

- færdig

- ned

- køre

- driver

- drivere

- grund

- i løbet af

- e

- E&T

- hver

- enten

- indlejret

- muliggøre

- muliggør

- ende

- ingeniør

- Engineering

- nok

- sikre

- Miljø

- udstyr

- etableret

- etc.

- Ether (ETH)

- udviklet sig

- eksempel

- eksisterer

- udvidelse

- forvente

- dyrt

- forklarede

- eksponentiel

- faciliteter

- faktor

- fabrik

- Manglende

- Fig

- endelige

- Finde

- ende

- Fornavn

- flad

- Fleksibilitet

- Flip

- flow

- strømme

- FLUX

- fokuserer

- Til

- for udbytte

- formation

- fundet

- fra

- yderligere

- Endvidere

- Gevinst

- kløft

- huller

- Generelt

- generelt

- få

- få

- glas

- Go

- Goes

- gå

- Guld

- godt

- slibning

- Grow

- vejledning

- håndtere

- Hård Ost

- Have

- have

- højde

- højder

- hjælpe

- Høj

- Høj ydeevne

- højere

- historisk

- Hole

- HOT

- Hvordan

- How To

- HTML

- HTTPS

- Hybrid

- i

- IBM

- IEEE

- billede

- billede

- Imaging

- påvirket

- vigtigt

- in

- Herunder

- Forøg

- øget

- stigende

- stigende

- individuel

- oplysninger

- initial

- Innovation

- i stedet

- integration

- integritet

- sammenkobler

- ind

- Invest

- involvere

- IT

- Varer

- ITS

- selv

- landskab

- større

- laser

- lag

- føre

- Forlade

- mindre

- Niveau

- niveauer

- lys

- ligesom

- GRÆNSE

- begrænsning

- begrænsninger

- grænser

- lidt

- Lang

- Se

- ligner

- Lot

- Lav

- Main

- lave

- maerker

- ledelse

- leder

- styring

- manuel

- manuelt

- Produktion

- mange

- kortlægning

- markere

- Marked

- Marketing

- materiale

- materialer

- modne

- max-bredde

- midler

- mekanisk

- mekanismer

- Mød

- møde

- Hukommelse

- nævnte

- metal

- metode

- metoder

- Metrologi

- micron

- mike

- minimum

- Mobil

- overvåges

- mere

- for det meste

- bevæge sig

- bevæger sig

- meget

- multi

- Natur

- Behov

- behov

- behov

- Ny

- Nye teknologier

- næste

- rart

- Nikkel

- ingen

- bemærkede

- nu

- nummer

- målsætninger

- of

- on

- engang

- ONE

- åbent

- åbning

- operatør

- Operatører

- Muligheder

- modsætning

- or

- organisk

- oprindeligt

- Andet

- vores

- ud

- i løbet af

- egen

- pakke

- pakker

- emballage

- pad

- side

- Parallel

- del

- partikel

- passerer

- Mennesker

- Søjle

- Pitch

- pladser

- Place

- plato

- Platon Data Intelligence

- PlatoData

- Leg

- Punkt

- fattige

- Populær

- populært valg

- positionerede

- mulig

- Indlæg

- magt

- præsident

- primære

- Forud

- behandle

- Processer

- forarbejdning

- Produkt

- produktstyring

- produktion

- Produkter

- fremskrevet

- egenskaber

- give

- skubbet

- sætte

- kvalitet

- spænder

- forholdet

- nå

- virkelig

- modtagende

- reducere

- Reduceret

- reducerer

- Uanset

- relaterede

- pålidelighed

- afhængighed

- fjernet

- kræver

- påkrævet

- Kræver

- Resultater

- Risiko

- køreplan

- køreplaner

- roller

- Værelse

- R

- routing

- regler

- Said

- samme

- sekundær

- se

- se

- set

- halvleder

- senior

- setup

- flere

- Shape

- skifte

- Kort

- bør

- side

- Signal

- Silicon

- lignende

- Tilsvarende

- siden

- enkelt

- Størrelse

- størrelser

- Slides

- lidt anderledes

- mindre

- So

- Løsninger

- nogle

- noget

- Snart

- Kilde

- Kilder

- Space

- specifikke

- specifikt

- standard

- starte

- Starter

- Steps

- stikning

- Stadig

- Historier

- stress

- undersøgelser

- vellykket

- sådan

- support

- overflade

- SVG

- bord

- Tag

- mål

- Teknologier

- Teknologier

- semester

- Test

- end

- at

- Landskabet

- deres

- Them

- tema

- derefter

- Der.

- derfor

- termisk

- Disse

- de

- ting

- Tænker

- denne

- dem

- selvom?

- stramt

- tid

- tip

- til

- i dag

- sammen

- værktøj

- værktøjer

- top

- spore

- trækkraft

- traditionelle

- prøv

- TUR

- to

- typen

- typer

- typisk

- under

- på

- brug

- anvendte

- ved brug af

- sædvanligvis

- udnytte

- række

- meget

- Vice President

- Specifikation

- vandladning

- var

- we

- GODT

- hvornår

- som

- hvid

- Hele

- udbredt

- Wikipedia

- vilje

- med

- uden

- Arbejde

- arbejder

- virker

- world

- X

- røntgen

- Udbytte

- udbytter

- dig

- Din

- zephyrnet