Termisk stress er et velkendt problem i avanceret emballage sammen med udfordringerne ved mekanisk stress. Begge forværres af heterogen integration, som ofte kræver blandingsmaterialer med inkompatible termiske udvidelseskoefficienter (CTE).

Effekterne viser sig allerede og vil sandsynligvis kun blive værre, efterhånden som pakketætheden stiger ud over 1,000 bump pr. chip.

»Man kombinerer metaller, der har en relativt høj CTE, så har man polymerer, der har endnu større CTE-stivhed, og så har man dielektrika, der har ekstremt lav CTE. Når du først har sat alt sammen, er stress uundgåelig,” sagde Mario Gonzalez, videnskabelig direktør og R&D-chef for mekanisk og termisk modellering og karakterisering hos imec.

En sådan stress resulterer ofte i betydelig skævhed eller hældning af matricen, hvilket igen fører til forhold, der forringer pålideligheden. "Du har at gøre med forskellige substratteknologier med flere lagoptællinger," sagde Chip Greely, vicepræsident for ingeniør hos Promex Industries. ”Forskellige kernetykkelser i substrater begynder især at skabe en masse klassiske mekaniske problemer, herunder vridning, som er blevet et smertepunkt for nogle af de større spillere. Vi beder mange af vores kunder, som har et system-i-pakke, heterogent integration multi-chip-modul, om at levere skyggemoiré-dataene for deres substrater, så vi kan se, hvordan dens forvridning ændrer sig over reflow-temperaturen og ideelt set finde dens refleksionspunkt."

Denne stamme har forskellige negative virkninger, oplevet over mange dimensionelle skalaer, ifølge Gilad Barak, vicepræsident for avancerede nye teknologier hos Nova. "Ofte er bøjning og vridning af funktioner på nanostrukturniveau resultatet af den indbyggede stress, der er blevet skabt, som findes i nogle DRAM og front-end logiske nanoark," sagde han. "Et andet eksempel vedrører områder i mikronskala, hvor induceret belastning forhindrer fremstillingen af avancerede halvlederstrukturer, som det er typisk i 'hold-out-zoner' omkring through-silicium vias (TSV'er). Endelig kan de store påvirkninger af induceret belastning forårsage waferbøjning, hvilket betydeligt komplicerer waferhåndtering og fremstilling, hvilket risikerer at bryde selve waferen. Waferbøjning ses især under aflejringen af tykke dielektriske lag, som det er almindeligt under fremstillingen af 3D NAND-enheder."

Den gode nyhed er, at industrien er meget opmærksom på disse og tilhørende problemer. Den dårlige nyhed er, at der stadig mangler løsninger, selvom der er mange tilgange, der i øjeblikket undersøges.

"Der er forskellige metoder til at reducere skævhed, men ingen af dem er fuldstændig succesfulde, og de kommer altid med afvejninger," sagde Frank Chen, direktør for applikationer og produktstyring hos Bruker Nano Surfaces & Metrology. “Problemerne er ikke isoleret til et snævert udvalg af applikationer. Hver gang du vedhæfter en matrice til et andet substrat, vil du have disse problemer."

Alt dette betyder, at inspektion og metrologi fortsat skal spille en afgørende rolle. Andre problemer, såsom hot spots, kan også forværres, når flere chips kombineres i heterogene pakker.

"Under testen vil forskellige chips varme op på forskellige tidspunkter og forskellige temperaturer, hvilket skaber mulige hot spots, der skal afkøles ordentligt," sagde Andrei Berar, seniordirektør for Test Business Development hos Amkor. "Udover at skabe specifikke termiske aktive controllere - der matcher arealet af forskellige chips - er der betydelige bestræbelser på at udvikle adaptive termiske controllere, der kan 'foregribe' hot spots baseret på vektorerne leveret af testprogrammet."

Sådanne kombinationer fører også til øget brug af hybrid metrologi - ved at kombinere forskellige teknikker for hurtigst at komme til roden af problemer.

Design, inspektion, testløsninger

Faktisk er det klassiske samspil mellem design, inspektion og termomekanisk stress kun blevet mere komplekst med tusindvis af stadig mindre og mere skrøbelige forbindelser.

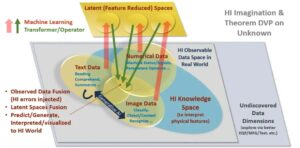

Et resultat er en fornyet vægt på at flytte til venstre for forhåbentlig at "designe" CTE-problemerne og deraf følgende kaskadeeffekter, der kan føre til overophedning og mekanisk stress. Og for at øge chancerne for at forebygge såvel som at finde kritiske defekter, er både simulering og inspektion nødvendige, ifølge Andras Vass-Varnai, porteføljeudviklingschef for Electronics and Semiconductor Industry-segmentet. Siemens Digital Industries Software.

"Termisk og strukturel co-simulering ved hjælp af beregningsmæssig flowdynamik (CFD), finite element-modellering (FEA) osv., i det tidlige designstadium af pakken hjælper både med at forstå den forventede ydeevne af samlingen og giver også et godt grundlag for ' AI-drevet optimering, da mange af designvalgene kan parametreres,” forklarede Vass-Varnai. "Når den første prototype er bygget, kan termisk transienttestning hjælpe med at kortlægge komponentens termiske ydeevne. Hvis der er et misforhold mellem den forventede og den reelle termiske adfærd, kan testdataene bruges til at 'kalibrere' materialeegenskaberne for pakkens digitale tvilling og opdatere materialebibliotekerne for højere initial nøjagtighed af kommende designs."

At finde den bedste måde at teste bump-arrays på og designe til test er en voksende udfordring. "Hvad hvis der er et signal, der går op og ned?" spurgte Rob Aitken, en Synopsys fyr. "Det skaber et testproblem, for nu har du et signal, der går til ingen steder, og et andet signal, der kommer fra ingenting, og du skal finde ud af, hvordan du vil teste de ting. Undersøger du dem? Men i så fald er der fysiske dimensioner, du skal vedligeholde, og så risikerer du at få mekaniske skader. Eller finder du en slags JTAG-lignende struktur? Men det reducerer så effektiviteten af disse forbindelsespunkter. Vi er i den store eksperimenteringsfase, hvor alle siger: 'Måske vil det her virke, måske vil det virke.' Lige nu ville jeg ikke nødvendigvis satse på, hvad 'det' er."

Der er både indirekte og direkte testmuligheder for defektundersøgelse, ifølge JCET. For eksempel er CSAM (Computed Scanning Acoustic Tomography) og 3D-røntgen indirekte, mens mekanisk tværsnitsanalyse er et værktøj til direkte bevis. JCET har også avanceret termisk karakteriseringsudstyr til at karakterisere materiale/strukturproblemer som følge af mekaniske defekter.

Optisk inspektion er som altid den hurtigste tilgang til inline-inspektion, men best practice er en hybrid tilgang. "Den bedste metode til at detektere shorts/åbninger og marginale defekter ville være SPI (loddepasta-inspektion) til pre-reflow AOI (automatiseret optisk inspektion) til post-reflow AOI til inline røntgen," rådgav Timothy Skunes, vicepræsident for forskning og udvikling i Nordson Test & Inspection's Cyberoptik portefølje.

Derudover kan andre modaliteter være nyttige, især ved avancerede noder. For eksempel er en nyere tilgang til karakterisering af belastning i halvlederenheder Raman Spectroscopy (RS). "RS er yderst anvendelig til målinger på strukturen, og tilbyder hurtige målinger i størrelsesordenen sekunder og små pletstørrelser på få mikron for at tillade detaljerede målinger," sagde Novas Barak. "Vanskeligheden ved direkte at måle belastningen på strukturer før introduktionen af Raman-spektroskopi som in-line metrologiværktøjer i fabrikken førte til test på meget senere stadier i fremstillingsprocessen."

I sidste ende, for grundig inspektion, er der ingen skærende hjørner. Budgetberegninger kan kræve komparative målinger, såsom startomkostningerne for et nyt instrument versus de løbende omkostninger ved overdreven RMA'er. Og der er endnu en ting at overveje – hvordan du sikrer dig, at du kan stole på dine data.

”Skal du smide det, der sandsynligvis var godt materiale, for at sikre, at du ikke har noget problemmateriale i det, du giver videre til slutbrugeren? Hvem skal bære omkostningerne ved det?” advarede Mike McIntyre, direktør for software produktstyring på På innovation, som anbefaler en statistisk database til nøjagtig sammenlignende vurdering, når man laver automatiseret defektklassificering.

Warpage

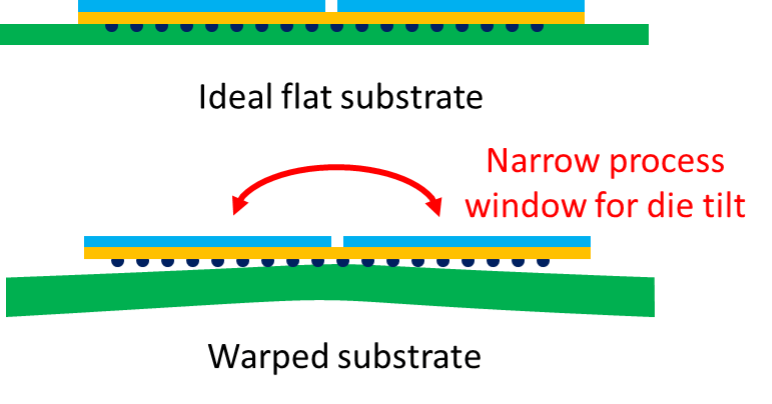

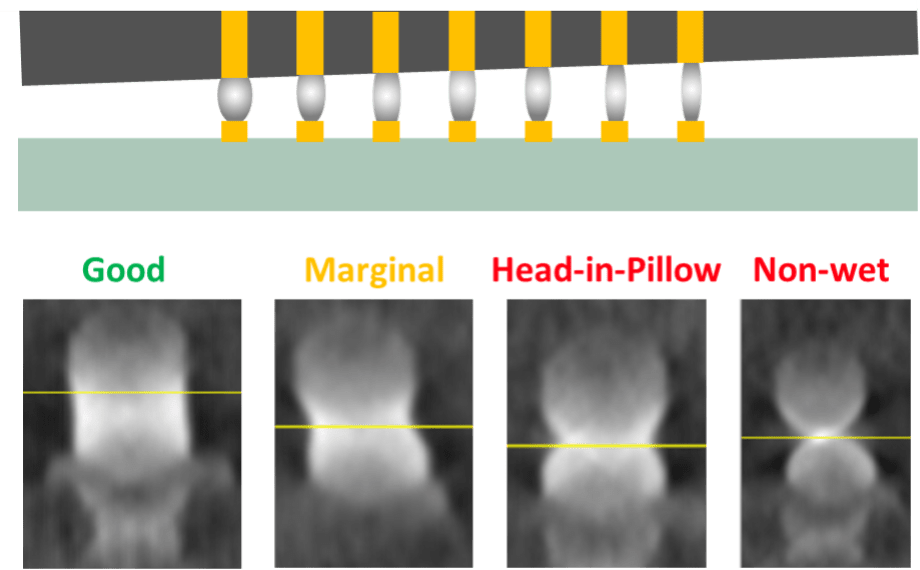

Et af de værste resultater af stress er forvridning. Det kan være overraskende, at forvridning kan være svær at opdage, men effekten er ikke altid så tydelig, som den ser ud til. Forvridning forårsager små forskelle i koplanaritet mellem chip og substrat, hvilket forårsager, at nogle mikrobump ikke forbindes tilstrækkeligt med puderne nedenfor, en fejl kaldet ikke-våd.

"Overvej en avanceret processor, der er 50 til 60 mm, som et eksempel," sagde Chen. "På grund af dens store størrelse er den udfordrende at behandle uden nogen form for skævhed. Ikke desto mindre, hvis matricefastgørelsesværktøjet er indstillet i midten af sit procesvindue, kan det bestå inspektion og fremstilles med høje udbytter. Problemet er, at tolerancen kan være meget snæver. Så snart du har en smule die-tilt oven på warpage, har du ikke-våde problemer."

Hvad værre er, hvis dette sker ved bump-afstande i 50µm-området (̴35µm bump-størrelse), forestil dig problemerne, da bump-dimensionerne skrumper yderligere. Det er allerede en bekymring for bilindustrien, da den bevæger sig mod sin næste generation i 2023 til 2024. Den kritiske overgang vil være omkring 28nm-knuden, sagde Chen.

Fig. 1 Matriceværktøj har et meget snævert procesvindue for matricetilt, når der er skævhed. Kilde: Bruker

Ikke-våde

"Ikke-våde," er et bredt udtryk, der dækker adskillige problemer, der kan opstå med loddebuler, hvoraf de fleste er frustrerende subtile. Fordi loddemetal ofte er i flydende tilstand, er processen med at påføre det blevet kaldt "befugtning". Svage links kaldes "ikke-våde", som bliver mere af en udfordring ved mindre noder med tyndere forbindelser.

Ikke-våde stoffer undslipper ofte typiske screeningsprocesser, for senere at dukke op som returnerede chips (RMA'er). De grundlæggende årsager kan være termiske, mekaniske eller en kombination, såsom termisk cykling i en bil, der også kører over ujævnt terræn. Den kumulative effekt kan give tilstrækkelig termisk-mekanisk belastning til at bryde kontakten.

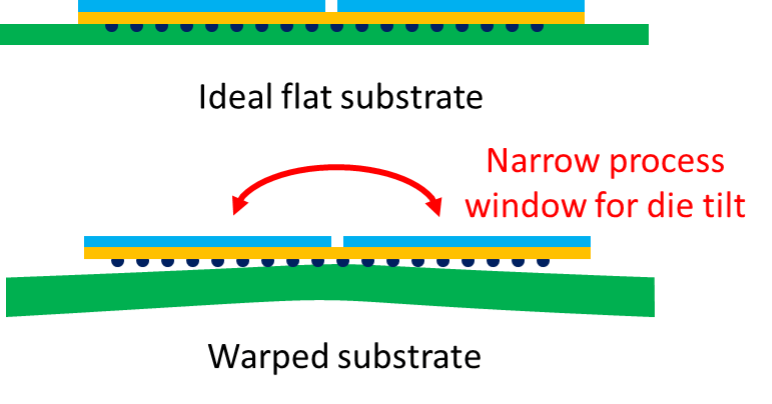

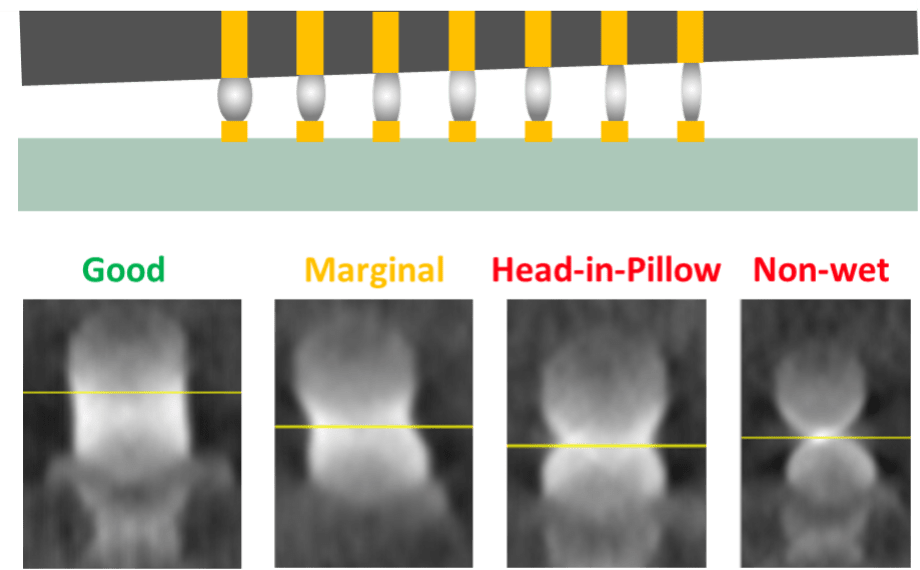

Der er yderligere kaldenavne, der beskriver specifikke typer problemer. I stedet for den glatte, søjleformede form af en god forbindelse, i en "hoved-i-pude"-defekt, synes den ene bold at synke ned i den anden, som et hoved på en pude.

"Den er stadig i kontakt, så den elektriske test kan være god, men du kan se, at den er meget skrøbelig," sagde Chen og pegede på røntgenbilledet af en hoved-i-pude. "Så snart du har en vis termisk belastning eller mekanisk belastning, kan den bryde fuldstændigt. Selvom det er en kontakt, der ikke er våd, fører den tynde forbindelse til høj modstand, suboptimal ydeevne og vil sandsynligvis ikke vare længe. En åben ikke-våd virker slet ikke. I et typisk scenarie med matricetilt er der en synlig overgang fra velformede bump til ikke-våde."

Det kritiske problem er latente defekter - forbindelser, der er funktionelle nok til at bestå en elektrisk test, men fejler i marken.

Fig. 2 Gradvis overgang fra gode ujævnheder til ikke-våde i nærvær af matricehældning. Kilde: Bruker

"Det er et stort problem lige nu med mange typer enheder på grund af virkningerne af termisk stress," sagde Chen. "En kunde havde et produkt, der bestod e-test screening og blev sendt ud. Desværre havde de mange RMA'er på grund af ikke-våde fejl, der udviklede sig bagefter."

Nogle virksomheder løser dette gennem smerteligt kedelige manuelle inspektioner. Desværre er enhver menneskelig undersøgelse underlagt operatørtræthed, især når eksaminatorer forsøger at opdage subtile fejl under et skift på flere timer.

På den positive side er der nu automatiserede tilgange til inspektion, såsom røntgenværktøjer, der kan bruges inline. "Der er en stor drivkraft i retning af højhastigheds, fuldautomatisk inspektion for at opnå <100 dppb, især for bilindustrien," sagde Chen.

Det bliver mere kompliceret derfra. "Det er bemærkelsesværdigt, at loddemetal, synderen bag mange ikke-våde stoffer, også er genstand for elektromigrering," sagde Tom Marinis, et hovedmedlem af Laboratory Technical Staff hos Draper. "Hvis strømtætheden i en forbindelse mellem en chip og et substrat er for høj for en bestemt loddemetal over en periode, fordi smeltetemperaturen på loddet kan være relativt lav sammenlignet med enhedens driftstemperatur, kan du få migrering af atomerne og danner faktisk tomrum og åbner til sidst en forbindelse."

Marinis advarede om, at kommercielle modelleringsværktøjer på enhed-PCB-niveau ikke er helt modne nok til konsekvent at advare om potentielle elektromigreringsproblemer, så det er vigtigt stadig at udføre en accelereret ældningstest.

Konklusion

I sidste ende vil detektering af pålidelighedsproblemer fra latente defekter kræve højere prøvetagningsmetrologi, der er følsom over for forskydning, rotation, højde, hældning og andre parametre. Det vil også kræve mere afhængighed af multi-fysisk modellering for at forsøge at forudse og løse potentielle problemer før produktion. Og efterhånden som halvleder- og bilindustrien fortsætter med at blande sig, er der langt mere på spil end blot RMA'er.

"Omkostningerne ved fejl vokser eksponentielt, efterhånden som latente defekter går fra enheder til moduler til biler, der kan bringe menneskers liv i fare," sagde Chen. Det er grunden til, at chipproducenter skaber holistiske løsninger, der kombinerer design, inspektion og test for bedre at fange latente fejl.

- SEO Powered Content & PR Distribution. Bliv forstærket i dag.

- Platoblokkæde. Web3 Metaverse Intelligence. Viden forstærket. Adgang her.

- Kilde: https://semiengineering.com/bump-reliability-is-challenged-by-latent-defects/

- 000

- 1

- 2023

- 2024

- 3d

- a

- accelereret

- Ifølge

- nøjagtighed

- præcis

- opnå

- aktiv

- faktisk

- Desuden

- Yderligere

- adressering

- fremskreden

- Aging

- Alert

- Alle

- tillader

- allerede

- Skønt

- altid

- analyse

- ,

- En anden

- foregribe

- anvendelig

- applikationer

- Anvendelse

- tilgang

- tilgange

- OMRÅDE

- områder

- omkring

- Assembly

- vurdering

- forbundet

- vedhæfte

- Automatiseret

- automotive

- bilindustrien

- Bad

- bold

- baseret

- grundlag

- Husk

- fordi

- bliver

- blive

- før

- bag

- være

- jf. nedenstående

- BEDSTE

- Bet

- Bedre

- mellem

- Beyond

- Big

- større

- Bit

- Pause

- bred

- budget

- bygget

- indbygget

- virksomhed

- forretningsudvikling

- kaldet

- Kan få

- bil

- biler

- tilfælde

- brydning

- Årsag

- årsager

- forårsager

- center

- CFD

- udfordre

- udfordret

- udfordringer

- udfordrende

- odds

- Ændringer

- karakterisere

- chen

- chip

- Chips

- valg

- Classic

- klassificering

- kombination

- kombinationer

- kombinerer

- kombineret

- kombinerer

- Kom

- kommerciel

- Fælles

- Virksomheder

- sammenlignet

- fuldstændig

- komplekse

- kompliceret

- komponent

- Bekymring

- betingelser

- Tilslut

- tilslutning

- Tilslutninger

- Overvej

- kontakt

- fortsæt

- Core

- hjørner

- Koste

- kunne

- dækker

- skabe

- oprettet

- skaber

- Oprettelse af

- kritisk

- Nuværende

- For øjeblikket

- kunde

- Kunder

- skære

- data

- Database

- beskæftiger

- tæthed

- beskrive

- Design

- designs

- detaljeret

- udvikle

- udviklet

- Udvikling

- enhed

- Enheder

- Die

- forskelle

- forskellige

- Vanskelighed

- digital

- digital tvilling

- størrelse

- direkte

- direkte

- Direktør

- gør

- Dont

- ned

- manufakturhandler

- driver

- døbt

- i løbet af

- dynamik

- Tidligt

- effekt

- effekter

- effektivitet

- indsats

- Elektronik

- vægt

- Engineering

- nok

- sikre

- udstyr

- fejl

- især

- etc.

- Ether (ETH)

- Endog

- til sidst

- at alt

- eksempel

- udøvende

- udvidelse

- forventet

- erfarne

- forklarede

- udforsket

- eksponentielt

- ekstremt

- FAIL

- Manglende

- hurtigste

- træthed

- Funktionalitet

- fyr

- få

- felt

- Fig

- Figur

- Endelig

- Finde

- finde

- Fornavn

- flow

- formular

- fundet

- fra

- frustrerende

- funktionel

- yderligere

- generation

- få

- Goes

- gå

- godt

- gradvis

- Dyrkning

- Vokser

- Håndtering

- Hård Ost

- hoved

- højde

- hjælpe

- hjælper

- Høj

- højere

- stærkt

- holistisk

- Forhåbentlig

- HOT

- Hvordan

- How To

- HTTPS

- menneskelig

- Hybrid

- Påvirkninger

- vigtigt

- in

- Herunder

- Forøg

- stigende

- industrier

- industrien

- initial

- i stedet

- instrument

- integration

- Introduktion

- undersøgelse

- isolerede

- spørgsmål

- spørgsmål

- IT

- selv

- Venlig

- laboratorium

- stor

- storstilet

- større

- Efternavn

- lag

- lag

- føre

- førende

- Leads

- Led

- Niveau

- biblioteker

- Sandsynlig

- links

- Flydende

- Lives

- Lang

- Lot

- Lav

- vedligeholde

- lave

- Making

- ledelse

- leder

- manuel

- fremstillet

- mange

- kort

- Mario

- matchende

- materiale

- materialer

- modne

- max-bredde

- midler

- målinger

- måling

- mekanisk

- medlem

- Metaller

- metode

- metoder

- Metrics

- Metrologi

- måske

- migration

- blandet

- modellering

- modul

- Moduler

- mere

- mest

- bevæger sig

- flere

- nano

- nødvendigvis

- behov

- negativ

- Ikke desto mindre

- Ny

- Nye teknologier

- nyheder

- næste

- node

- noder

- Obvious

- tilbyde

- ONE

- igangværende

- åbent

- drift

- operatør

- optimering

- Indstillinger

- ordrer

- Andet

- pakke

- pakker

- emballage

- Smerte

- parametre

- særlig

- især

- Bestået

- folks

- udføre

- ydeevne

- periode

- fase

- fysisk

- pladser

- plato

- Platon Data Intelligence

- PlatoData

- Leg

- spillere

- Punkt

- punkter

- Polymerer

- portefølje

- positiv

- mulig

- potentiale

- praksis

- tilstedeværelse

- præsident

- forebyggelse

- Main

- Forud

- sandsynligvis

- sonde

- Problem

- problemer

- behandle

- Processer

- Processor

- Produkt

- produktstyring

- produktion

- Program

- bevis

- korrekt

- egenskaber

- prototype

- give

- forudsat

- sætte

- F & U

- rækkevidde

- hurtige

- ægte

- nylige

- anbefaler

- reducere

- reducerer

- refleksion

- relativt

- pålidelighed

- afhængighed

- fornyet

- kræver

- Kræver

- forskning

- forskning og udvikling

- resultere

- resulterer

- Resultater

- Risiko

- risici

- roller

- rod

- Kør

- Said

- siger

- skalaer

- scanning

- scenarie

- screening

- sekunder

- synes

- segment

- valg

- halvleder

- senior

- følsom

- flere

- Shadow

- Shape

- skifte

- SKIFT

- afsendt

- Kort

- Vis

- Signal

- signifikant

- betydeligt

- simulation

- Størrelse

- størrelser

- lille

- mindre

- So

- Software

- Løsninger

- nogle

- Snart

- Kilde

- specifikke

- Spektroskopi

- Spot

- Personale

- Stage

- etaper

- spil

- starte

- Tilstand

- statistiske

- Stadig

- stress

- strukturel

- struktur

- emne

- vellykket

- sådan

- overraskende

- Teknisk

- teknikker

- Teknologier

- prøve

- Test

- Området

- deres

- Der.

- termisk

- ting

- ting

- tusinder

- Gennem

- Kaste

- tid

- gange

- til

- sammen

- tolerance

- også

- værktøj

- værktøjer

- top

- mod

- overgang

- Stol

- TUR

- typer

- typisk

- forstå

- kommende

- Opdatering

- brug

- Bruger

- forskellige

- Vast

- Vice President

- synlig

- Kendt

- Hvad

- som

- mens

- WHO

- vilje

- uden

- Arbejde

- Værst

- ville

- røntgen

- udbytter

- Din

- zephyrnet