1980 এর দশকে 10Mbps শেয়ার্ড LAN-এর সাথে কোঅক্সিয়াল ক্যাবলের মাধ্যমে আত্মপ্রকাশের পর থেকে, ইথারনেট ধারাবাহিক অগ্রগতি দেখেছে, এখন 1.6Tbps পর্যন্ত গতি সমর্থন করার সম্ভাবনা রয়েছে। এই অগ্রগতি ইথারনেটকে লাইভ স্ট্রিমিং, রেডিও অ্যাক্সেস নেটওয়ার্ক এবং ইন্ডাস্ট্রিয়াল কন্ট্রোলের মতো বিস্তৃত পরিসরে অ্যাপ্লিকেশন পরিবেশন করার অনুমতি দিয়েছে, নির্ভরযোগ্য প্যাকেট স্থানান্তর এবং পরিষেবার গুণমানকে গুরুত্ব দিয়ে। বর্তমান ইন্টারনেট ব্যান্ডউইথ ~500 Tbps-এ গুনগুন করে, উন্নত ব্যাক-এন্ড ইন্ট্রা ডেটাসেন্টার ট্রাফিক পরিচালনার জন্য একটি ক্রমবর্ধমান চাহিদা রয়েছে। যদিও স্বতন্ত্র সার্ভারগুলি এখনও টেরাবিট-প্রতি-সেকেন্ড স্তরে কাজ করছে না, সামগ্রিক ডেটাসেন্টার ট্র্যাফিক এই স্কেলের কাছাকাছি, যা IEEE-এর 802.3dj গ্রুপকে প্রমিতকরণের প্রচেষ্টা গ্রহণ করতে প্ররোচিত করে এবং প্রসারিত ডেটা প্রবাহ পরিচালনা করার জন্য শক্তিশালী ইথারনেট কন্ট্রোলার এবং SerDes প্রয়োজন। ক্রমবর্ধমান চাহিদার এই পটভূমির মধ্যে, আন্তঃপ্রসেসর যোগাযোগ ইতিমধ্যে এই গতিতে ঠেলে দিচ্ছে।

আন্তঃপ্রসেসর যোগাযোগ ন্যূনতম লেটেন্সি সহ 1.6T হারের প্রয়োজনে নেতৃত্ব দিচ্ছে। যদিও পৃথক ডিভাইসগুলি তাদের অন্তর্নিহিত প্রক্রিয়াকরণ ক্ষমতা এবং চিপের আকার দ্বারা সীমাবদ্ধ থাকে, চিপগুলি একত্রিত করা এই ক্ষমতাগুলি উল্লেখযোগ্যভাবে প্রসারিত করতে পারে। প্রথম প্রজন্মের অ্যাপ্লিকেশনগুলি ইন্ট্রা ডেটাসেন্টার সুইচ-টু-সুইচ সংযোগগুলি অনুসরণ করবে বলে আশা করা হচ্ছে, উচ্চ-পারফরম্যান্স প্রসেসর এবং মেমরির পুলিং সক্ষম করে, ক্লাউড কম্পিউটিং-এর মধ্যে স্কেলেবিলিটি এবং দক্ষতা বৃদ্ধি করে৷

IEEE এর 802.3dj উদ্যোগ: 1.6 Tbps ইন্টারঅপারেবিলিটির জন্য ইথারনেট মান উন্নত করা

ক্রমবর্ধমান প্রমিতকরণ প্রচেষ্টার সম্মতি নিরবচ্ছিন্ন ইকোসিস্টেম আন্তঃকার্যযোগ্যতার জন্য গুরুত্বপূর্ণ। IEEE এর 802.3dj গ্রুপ আসন্ন ইথারনেট স্ট্যান্ডার্ড তৈরির প্রক্রিয়ার মধ্যে রয়েছে, যা 200G থেকে প্রতি সেকেন্ডে 1.6 টেরাবিট পর্যন্ত গতির জন্য শারীরিক স্তর এবং পরিচালনার পরামিতিগুলিকে অন্তর্ভুক্ত করে। গ্রুপের উদ্দেশ্য হল একটি 1.6 Tbps ইথারনেট MAC ডেটা রেট, যার লক্ষ্য হল MAC স্তরে সর্বোচ্চ 10-13 এর বেশি বিট ত্রুটির হার না হওয়া। আরও বিধানের মধ্যে রয়েছে ঐচ্ছিক 16 এবং 8 লেন সংযুক্তি ইউনিট ইন্টারফেস (AUI) বিভিন্ন চিপ অ্যাপ্লিকেশনের জন্য উপযুক্ত, 112G এবং 224G SerDes ব্যবহার করে। শারীরিকভাবে, 1.6Tbps স্পেসিফিকেশন 8 মিটার থেকে 8 কিমি পর্যন্ত দূরত্বের জন্য 500 জোড়া কপার টুইন্যাক্স তারের মাধ্যমে এক মিটার পর্যন্ত এবং 2 জোড়া ফাইবারের মাধ্যমে ট্রান্সমিশন করে। যদিও স্ট্যান্ডার্ডের সম্পূর্ণ অনুমোদন 2026 সালের বসন্তের মধ্যে প্রত্যাশিত, বৈশিষ্ট্যগুলির মূল সেটটি 2024 সমাপ্তির জন্য অনুমান করা হয়েছে।

একটি 1.6T ইথারনেট সাবসিস্টেমে ব্যান্ডউইথ ওভারহেড এবং ত্রুটি সংশোধন

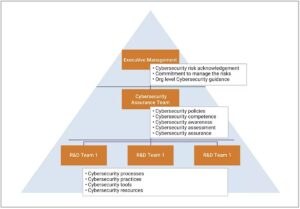

চিত্র 1: একটি 1.6T ইথারনেট সাবসিস্টেমের উপাদানগুলি চিত্রিত করা চিত্র।

পূর্ববর্তী ইথারনেট পুনরাবৃত্তিতে, পিসিএস প্রাথমিকভাবে নির্ভরযোগ্য প্যাকেট সনাক্তকরণের জন্য ডেটা এনকোডিংয়ের উপর দৃষ্টি নিবদ্ধ করেছিল। যাইহোক, 1.6T ইথারনেট গতি বৃদ্ধির সাথে, ফরোয়ার্ড এরর কারেকশন (এফইসি) এর প্রয়োজনীয়তা স্পষ্ট হয়ে ওঠে, বিশেষ করে এমনকি ছোট লিঙ্কগুলিতেও সংকেত ক্ষয় প্রতিরোধ করার জন্য। এই উদ্দেশ্যে, 1.6T ইথারনেট রিড-সলোমন FEC ব্যবহার করে চলেছে৷ এই পদ্ধতিটি 514 প্রতীক ব্লকে এনকোড করা 10 544-বিট চিহ্ন সমন্বিত একটি কোডওয়ার্ড তৈরি করে, যার ফলে 6% ব্যান্ডউইথ ওভারহেড হয়। এই FEC কোডওয়ার্ডগুলি AUI ফিজিক্যাল লিঙ্ক জুড়ে বিতরণ করা হয় যাতে প্রতিটি ফিজিক্যাল লিঙ্ক (8T ইথারনেটের জন্য 1.6) একটি সম্পূর্ণ কোডওয়ার্ড বহন করে না। এই পদ্ধতিটি শুধুমাত্র ত্রুটির বিস্ফোরণের বিরুদ্ধে অতিরিক্ত সুরক্ষা দেয় না বরং দূরবর্তী ডিকোডারে সমান্তরালকরণ সক্ষম করে, যার ফলে লেটেন্সি হ্রাস পায়।

ফিজিক্যাল মিডিয়াম অ্যাটাচমেন্ট (PMA), একটি গিয়ারবক্স এবং SerDes সমন্বিত, ইথারনেট সংকেত প্রেরণ করা চ্যানেলগুলিতে নিয়ে আসে। 1.6T ইথারনেটের জন্য, এতে 8Gbps গতিতে 212টি চ্যানেল চলছে, যার জন্য 6% FEC ওভারহেড রয়েছে। নিযুক্ত মডুলেশন কৌশল হল 4-লেভেল পালস এমপ্লিটিউড মডুলেশন (PAM-4), যা প্রতিটি ট্রান্সমিশন চিহ্নের জন্য দুটি ডেটা বিট এনকোড করে, যার ফলে প্রথাগত নন-রিটার্ন জিরো (NRZ) পদ্ধতির সাথে মিলিত হলে ব্যান্ডউইথ কার্যকরভাবে দ্বিগুণ হয়। ট্রান্সমিশন মেকানিজম ডিজিটাল-টু-অ্যানালগ রূপান্তরের উপর নির্ভর করে, যখন প্রাপ্তির শেষে একটি এনালগ-থেকে-ডিজিটাল রূপান্তর DSP-এর সাথে মিলিত সঠিক সংকেত নিষ্কাশন নিশ্চিত করে।

উপরন্তু, এটা মনে রাখা গুরুত্বপূর্ণ যে ইথারনেট পিসিএস একটি "বাহ্যিক FEC" প্রবর্তন করে যা একটি ইথারনেট লিঙ্কে এন্ড-টু-এন্ড বিস্তৃত। দীর্ঘতর নাগালের চ্যানেলগুলিকে শক্তিশালী করতে, পৃথক ফিজিক্যাল লাইনগুলির জন্য ত্রুটি সংশোধনের একটি অতিরিক্ত স্তর পাইপলাইনে রয়েছে, সম্ভবত একটি হ্যামিং কোড FEC গ্রহণ করে। এই সংশোধনটি অপটিক্যাল ট্রান্সসিভার মডিউলগুলিতে এর প্রাথমিক প্রয়োগ খুঁজে পাওয়ার জন্য প্রত্যাশিত যেখানে এই ধরনের সংশোধন অপরিহার্য।

চিত্র 2: বর্ধিত নাগালের জন্য একটি সংযুক্ত FEC ব্যবহার করার সময় অতিরিক্ত ওভারহেড যোগ করা চিত্র প্রদর্শন করে।

চিত্র 2 এ চিত্রিত উদাহরণ সিস্টেমে, MAC এবং PCS একটি অপটিক্যাল মডিউল এবং একটি ফাইবার স্ট্রেচের মাধ্যমে সংযুক্ত। PCS-এর বিট ত্রুটির হার 10-5 অপটিক্যাল মডিউল লিঙ্কে, এছাড়াও অপটিক্যাল লিঙ্ক থেকেই ত্রুটি। 10 অর্জনের জন্য একমাত্র RS-FEC এন্ড-টু-এন্ড ব্যবহার করা যথেষ্ট হবে না-13 ইথারনেট স্ট্যান্ডার্ড, লিঙ্কটিকে অবিশ্বস্ত করছে। একটি বিকল্প হ'ল প্রতিটি হপে পৃথক RS FEC এর ট্রিপল বাস্তবায়ন, খরচ এবং বিলম্বিতা উল্লেখযোগ্যভাবে বৃদ্ধি পাবে। একটি আরও কার্যকর সমাধান হল অপটিক্যাল সংযোগের সাধারণ র্যান্ডম ত্রুটিগুলি পূরণ করে, বিশেষত অপটিক্যাল লিঙ্কের জন্য একটি সমন্বিত হ্যামিং কোড FEC এর একীকরণ। এই অভ্যন্তরীণ FEC স্তরটি 212 Gbps থেকে 226 Gbps পর্যন্ত লাইনের হারের একটি অতিরিক্ত প্রসারণ তৈরি করে, এইভাবে এটি অপরিহার্য যে SerDes এই লাইন হারকে সমর্থন করতে পারে।

1.6T ইথারনেট সিস্টেমে লেটেন্সি চ্যালেঞ্জ

চিত্র 3: 1.6T ইথারনেট সাবসিস্টেমের জন্য লেটেন্সি পাথ।

বিভিন্ন উপাদান ইথারনেট লেটেন্সিতে অবদান রাখে: ট্রান্সমিট সারি, ট্রান্সমিশন সময়কাল, মাঝারি ট্রাভার্সাল সময় এবং বেশ কিছু প্রক্রিয়াকরণ এবং প্রাপ্তির সময়। এটি কল্পনা করতে, চিত্র 3 বিবেচনা করুন, যা একটি ব্যাপক 1.6T ইথারনেট সাবসিস্টেম প্রদর্শন করে। যদিও সুদূরপ্রসারী প্রয়োগের প্রতিক্রিয়া সময় দ্বারা লেটেন্সি প্রভাবিত হতে পারে, এই ফ্যাক্টরটি ইথারনেটের বাহ্যিক এবং তাই প্রায়ই লেটেন্সি বিশ্লেষণের সময় বাদ দেওয়া হয়। ইথারনেট ইন্টারফেসে বিলম্ব কমানোর জন্য নির্দিষ্ট পরিস্থিতিতে বোঝার প্রয়োজন। উদাহরণস্বরূপ, ধীরগতির ক্লায়েন্ট লিঙ্কগুলিতে অন্তর্নিহিত বিলম্বের কারণে সুইচগুলির মধ্যে ট্রাঙ্ক সংযোগের জন্য লেটেন্সি একটি প্রাথমিক উদ্বেগ নাও হতে পারে। দূরত্বও একটি ভূমিকা পালন করে; বৃহত্তর দৈর্ঘ্য আরো লেটেন্সি পরিচয় করিয়ে দেয়। অবশ্যই, এর অর্থ এই নয় যে আমাদের অন্যান্য পরিস্থিতিতে বিলম্বকে উপেক্ষা করা উচিত, বিলম্ব হ্রাস করা সর্বদা একটি উদ্দেশ্য।

ট্রান্সমিশন লেটেন্সি সহজাতভাবে ইথারনেট হার এবং ফ্রেমের আকারের সাথে আবদ্ধ। বিশেষত, একটি 1.6T ইথারনেট সিস্টেমের জন্য, একটি ন্যূনতম আকারের প্যাকেট প্রেরণের জন্য 0.4ns প্রয়োজন - মূলত, একটি 2.5 GHz ঘড়ির প্রতি টিক একটি ইথারনেট ফ্রেম। অন্যদিকে, একটি আদর্শ সর্বোচ্চ আকারের ফ্রেম প্রেরণ করতে 8ns লাগে, যা জাম্বো ফ্রেমের জন্য 48ns পর্যন্ত প্রসারিত হয়। নির্বাচিত মাধ্যমটি আরও বিলম্বের নির্দেশ দেয়। উদাহরণস্বরূপ, অপটিক্যাল ফাইবার সাধারণত প্রতি মিটারে 5ns এর লেটেন্সি বহন করে, যেখানে কপার ক্যাবলিং 4ns প্রতি মিটারে সামান্য দ্রুততর হয়।

সামগ্রিক বিলম্বের একটি উল্লেখযোগ্য অংশ রিসিভার কন্ট্রোলারে নিহিত। আরএস এফইসি ডিকোডার অন্তর্নিহিতভাবে লেটেন্সি প্রবর্তন করে। ত্রুটি সংশোধন শুরু করার জন্য, সিস্টেমটিকে অবশ্যই 4টি কোডওয়ার্ড পেতে হবে, যা 1.6Tbps-এ, 12.8ns। ত্রুটি সংশোধন এবং বাফারিং সহ পরবর্তী ক্রিয়াকলাপগুলি এই বিলম্বকে প্রসারিত করে৷ যদিও FEC কোডওয়ার্ড স্টোরেজ সময়কাল সামঞ্জস্যপূর্ণ থাকে, বার্তা গ্রহণের সময় বিলম্ব নির্দিষ্ট বাস্তবায়নের উপর নির্ভরশীল। তবুও, সূক্ষ্ম ডিজিটাল ডিজাইন কৌশল প্রয়োগ করে বিলম্বকে অপ্টিমাইজ করা যেতে পারে।

সংক্ষেপে, FEC প্রক্রিয়া এবং শারীরিক দূরত্ব বা তারের দৈর্ঘ্যের কারণে একটি অন্তর্নিহিত, অনিবার্য বিলম্ব রয়েছে। এই কারণগুলির বাইরে, ডিজাইনের দক্ষতা ইথারনেট কন্ট্রোলার লেটেন্সি কমাতে একটি গুরুত্বপূর্ণ ভূমিকা পালন করে। MAC, PCS এবং PHY-কে একীভূত এবং অপ্টিমাইজ করে এমন একটি সম্পূর্ণ সমাধান ব্যবহার করা, সবচেয়ে দক্ষ, কম লেটেন্সি বাস্তবায়নের পথ তৈরি করে।

সারাংশ

চিত্র 4: 224nm প্রক্রিয়ায় Synopsys 3G ইথারনেট PHY IP-এর জন্য প্রথম-পাস সিলিকন সাফল্য অত্যন্ত লিনিয়ার PAM-4 চোখ প্রদর্শন করে।

1.6 Tbps ইথারনেট সবচেয়ে বেশি ব্যান্ডউইথের চাহিদা এবং লেটেন্সি সংবেদনশীল অ্যাপ্লিকেশনের জন্য তৈরি করা হয়েছে। 224G SerDes প্রযুক্তির উদ্ভবের সাথে, MAC এবং PCS IP-এর অগ্রগতির সাথে একত্রে, ব্যাপক সমাধানগুলি এখন অ্যাক্সেসযোগ্য যা ক্রমাগত বিকশিত 1.6T ইথারনেট মানগুলির সাথে সামঞ্জস্যপূর্ণ। অতিরিক্তভাবে, প্রোটোকলের অন্তর্নিহিত লেটেন্সি এবং ত্রুটি সংশোধন পদ্ধতির কারণে, ডেটাপথে অপ্রয়োজনীয় লেটেন্সি প্রবর্তন এড়াতে বিশেষজ্ঞ ডিজাইনারদের দ্বারা আইপি ডিজিটাল এবং অ্যানালগ ডিজাইনটি যত্ন সহকারে তৈরি করা উচিত।

1.6T SoC ডিজাইনের জন্য সেরা পারফরম্যান্স অর্জনের জন্য প্রতিটি চিপ উপাদানের জন্য একটি দক্ষভাবে অপ্টিমাইজ করা আর্কিটেকচার এবং সূক্ষ্ম নকশা অনুশীলনের প্রয়োজন। এটি শক্তি সংরক্ষণের উপর জোর দেয় এবং সিলিকন পদচিহ্নকে ন্যূনতম করে, 1.6T ডেটা রেটকে বাস্তবে পরিণত করে। সিলিকন-প্রমাণিত Synopsys 224G ইথারনেট PHY আইপি 1.6T MAC এবং PCS কন্ট্রোলারের জন্য মঞ্চ সেট করেছে। অগ্রণী-প্রান্তের নকশা, বিশ্লেষণ, সিমুলেশন এবং পরিমাপ কৌশল ব্যবহার করে, Synopsys ব্যতিক্রমী সংকেত অখণ্ডতা এবং জিটার কর্মক্ষমতা প্রদান করে চলেছে, MAC+PCS+PHY সহ সম্পূর্ণ ইথারনেট সমাধান.

- এসইও চালিত বিষয়বস্তু এবং পিআর বিতরণ। আজই পরিবর্ধিত পান।

- PlatoData.Network উল্লম্ব জেনারেটিভ Ai. নিজেকে ক্ষমতায়িত করুন। এখানে প্রবেশ করুন.

- প্লেটোএআইস্ট্রিম। Web3 ইন্টেলিজেন্স। জ্ঞান প্রসারিত. এখানে প্রবেশ করুন.

- প্লেটোইএসজি। কার্বন, ক্লিনটেক, শক্তি, পরিবেশ সৌর, বর্জ্য ব্যবস্থাপনা. এখানে প্রবেশ করুন.

- প্লেটো হেলথ। বায়োটেক এবং ক্লিনিক্যাল ট্রায়াল ইন্টেলিজেন্স। এখানে প্রবেশ করুন.

- উত্স: https://semiengineering.com/latency-considerations-for-1-6t-ethernet-designs/

- : আছে

- : হয়

- :না

- :কোথায়

- $ ইউপি

- 1

- 12

- 16

- 2024

- 2026

- 212

- 220

- 362

- 500

- 8

- a

- প্রবেশ

- প্রবেশযোগ্য

- হিসাবরক্ষণ

- সঠিক

- অর্জন করা

- দিয়ে

- ক্রিয়াকলাপ

- যোগ

- অতিরিক্ত

- উপরন্তু

- দত্তক

- উন্নয়নের

- আগুয়ান

- বিরুদ্ধে

- লক্ষ্য

- অনুমতি

- ইতিমধ্যে

- এছাড়াও

- যদিও

- সর্বদা

- অন্তরে

- পরিমাণে

- প্রশস্ত করা

- an

- বিশ্লেষণ

- এবং

- অপেক্ষিত

- আবেদন

- অ্যাপ্লিকেশন

- অভিগমন

- স্থাপত্য

- রয়েছি

- AS

- At

- এড়াতে

- ব্যাক-এন্ড

- ব্যাকড্রপ

- ব্যান্ডউইথ

- BE

- হয়ে

- মধ্যে

- তার পরেও

- বিট

- বাধা

- তাকিয়া

- boosting

- আনে

- তৈরী করে

- কিন্তু

- by

- USB cable.

- তারের

- CAN

- ক্ষমতা

- বহন

- চ্যালেঞ্জ

- চ্যানেল

- চিপ

- চিপস

- মনোনীত

- পরিস্থিতি

- মক্কেল

- ঘড়ি

- মেঘ

- ক্লাউড কম্পিউটিং

- কোড

- মিলিত

- মিশ্রন

- যোগাযোগ

- সম্পূর্ণ

- পরিপূরণ

- উপাদান

- উপাদান

- ব্যাপক

- অংশীভূত

- কম্পিউটিং

- উদ্বেগ

- সংযোগ

- সংযুক্ত

- সংযোগ

- বিবেচনা

- বিবেচনা

- বিবেচ্য বিষয়

- সঙ্গত

- চলতে

- একটানা

- অবদান

- নিয়ন্ত্রণ

- নিয়ামক

- পরিবর্তন

- তামা

- মূল

- খরচ

- পাল্টা

- পথ

- পেরেছিলেন

- সৃষ্টি

- বর্তমান

- উপাত্ত

- তথ্য কেন্দ্র

- উদয়

- বিলম্ব

- প্রদান করা

- চাহিদা

- চাহিদা

- দাবি

- তা পেশ

- নকশা

- ডিজাইনার

- ডিজাইন

- সনাক্তকরণ

- ডিভাইস

- আদেশ দেয়

- বিভিন্ন

- ডিজিটাল

- অধ্যবসায়

- প্রদর্শন

- দূরত্ব

- বণ্টিত

- না

- দ্বিত্ব

- কারণে

- স্থিতিকাল

- সময়

- প্রতি

- পূর্বে

- বাস্তু

- কার্যকর

- কার্যকরীভাবে

- দক্ষতা

- দক্ষ

- দক্ষতার

- প্রচেষ্টা

- উত্থান

- জোর দেয়

- জোর

- নিযুক্ত

- প্রয়োজক

- সম্ভব

- সক্রিয়

- পরিবেষ্টিত

- শেষ

- সর্বশেষ সীমা

- নিশ্চিত

- সমগ্র

- ভুল

- ত্রুটি

- তীব্রতাবৃদ্ধি

- সারমর্ম

- অপরিহার্য

- মূলত

- থার (eth)

- এমন কি

- প্রতি

- স্পষ্ট

- নব্য

- উদাহরণ

- ব্যতিক্রমী

- ছাঁটা

- বিস্তৃত

- সম্প্রসারণ

- প্রত্যাশিত

- ক্যান্সার

- ল্যাপারোস্কোপিক পদ্ধতি

- প্রসারিত করা

- ব্যাপ্ত

- বহিরাগত

- নিষ্কাশন

- চোখ

- গুণক

- কারণের

- এ পর্যন্ত

- দ্রুত

- বৈশিষ্ট্য

- সমন্বিত

- ব্যক্তিত্ব

- আবিষ্কার

- প্রথম

- প্রথম প্রজন্ম

- প্রবাহ

- দৃষ্টি নিবদ্ধ করা

- অনুসৃত

- পদাঙ্ক

- জন্য

- প্রণয়ন

- অগ্রবর্তী

- ফ্রেম

- থেকে

- অধিকতর

- প্রজন্ম

- দেয়

- বৃহত্তর

- গ্রুপ

- গ্রুপের

- ক্রমবর্ধমান

- হাত

- হ্যান্ডলিং

- উচ্চ

- উচ্চ পারদর্শিতা

- অত্যন্ত

- যাহোক

- এইচটিএমএল

- HTTPS দ্বারা

- অনুজ্ঞাসূচক

- বাস্তবায়ন

- গুরুত্ব

- গুরুত্বপূর্ণ

- উন্নত

- in

- অন্যান্য

- অন্তর্ভুক্ত করা

- সুদ্ধ

- ক্রমবর্ধমান

- স্বতন্ত্র

- শিল্প

- প্রভাবিত

- সহজাত

- মজ্জাগতভাবে

- আরম্ভ করা

- ইনিশিয়েটিভ

- উদাহরণ

- সংহত

- ইন্টিগ্রেশন

- অখণ্ডতা

- ইন্টারফেস

- ইন্টারফেসগুলি

- Internet

- আন্তঃক্রিয়া

- মধ্যে

- স্বকীয়

- প্রবর্তন করা

- পরিচয় করিয়ে দেয়

- উপস্থাপক

- জড়িত

- IP

- IT

- পুনরাবৃত্তি

- এর

- নিজেই

- JPG

- গলি

- অদৃশ্যতা

- স্তর

- স্তর

- লম্বা

- মাত্রা

- উপজীব্য

- সম্ভবত

- লাইন

- লাইন

- LINK

- লিঙ্ক

- জীবিত

- আর

- কম

- ম্যাক

- মেকিং

- পরিচালনা করা

- ব্যবস্থাপনা

- সর্বোচ্চ প্রস্থ

- সর্বাধিক

- মে..

- গড়

- মাপা

- পদ্ধতি

- মধ্যম

- স্মৃতি

- বার্তা

- পদ্ধতি

- পদ্ধতি

- সাবধানী

- যত্সামান্য

- কমান

- ছোট

- ছোট করা

- মডিউল

- মডিউল

- অধিক

- সেতু

- অবশ্যই

- প্রায়

- প্রয়োজন

- নেটওয়ার্ক

- তবু

- না।

- বিঃদ্রঃ

- এখন

- উদ্দেশ্য

- of

- প্রায়ই

- on

- ONE

- কেবল

- অপারেটিং

- অপ্টিমাইজ

- সেরা অনুকূল রূপ

- পছন্দ

- or

- অন্যান্য

- শেষ

- সামগ্রিক

- জোড়া

- পরামিতি

- বিশেষত

- পথ

- পিসি

- প্রতি

- কর্মক্ষমতা

- ক্রিয়াকাণ্ড

- শারীরিক

- শারীরিক

- পাইপলাইন

- কেঁদ্রগত

- Plato

- প্লেটো ডেটা ইন্টেলিজেন্স

- প্লেটোডাটা

- নাটক

- যোগ

- সম্ভাব্য

- ক্ষমতা

- চর্চা

- প্রাথমিকভাবে

- প্রাথমিক

- প্রক্রিয়া

- প্রক্রিয়াজাতকরণ

- প্রসেসর

- অগ্রগতি

- অভিক্ষিপ্ত

- রক্ষা

- প্রোটোকল

- নাড়ি

- উদ্দেশ্য

- ঠেলাঠেলি

- গুণ

- রেডিও

- এলোমেলো

- পরিসর

- হার

- হার

- নাগাল

- পৌঁছনো

- প্রতিক্রিয়া

- বাস্তবতা

- গ্রহণ করা

- গ্রহণ

- অভ্যর্থনা

- হ্রাস

- বিশ্বাসযোগ্য

- দেহাবশেষ

- অনুবাদ

- প্রয়োজন

- সীমাবদ্ধ

- ফলে এবং

- শক্তসমর্থ

- ভূমিকা

- মূলী

- দৌড়

- স্কেলেবিলিটি

- স্কেল

- পরিস্থিতিতে

- নির্বিঘ্ন

- দ্বিতীয়

- দেখা

- রেখাংশ

- সংবেদনশীল

- আলাদা

- পরিবেশন করা

- সেবা

- সেট

- বিভিন্ন

- ভাগ

- সংক্ষিপ্ত

- উচিত

- বেড়াবে

- সংকেত

- উল্লেখযোগ্যভাবে

- সিলিকোন

- ব্যাজ

- আয়তন

- So

- সমাধান

- সলিউশন

- ঘটনাকাল

- নেতৃত্বদান

- নির্দিষ্ট

- বিশেষভাবে

- সবিস্তার বিবরণী

- গতি

- বসন্ত

- পর্যায়

- মান

- প্রমিতকরণ

- মান

- স্টোরেজ

- কৌশল

- স্ট্রিমিং

- পরবর্তী

- সারগর্ভ

- সাফল্য

- এমন

- উপযুক্ত

- সমর্থন

- প্রতীক

- পদ্ধতি

- উপযোগী

- লাগে

- প্রযুক্তি

- প্রযুক্তি

- প্রযুক্তিঃ

- চেয়ে

- যে

- সার্জারির

- তাদের

- সেখানে।

- যার ফলে

- অতএব

- এইগুলো

- এই

- দ্বারা

- এইভাবে

- টিক্ টিক্ শব্দ

- বাঁধা

- সময়

- বার

- থেকে

- শীর্ষ

- ঐতিহ্যগত

- ট্রাফিক

- হস্তান্তর

- প্রেরণ করা

- ত্রৈধ

- দুই

- টিপিক্যাল

- সাধারণত

- অনিবার্য

- বোধশক্তি

- দায়িত্বগ্রহণ করা

- একক

- আসন্ন

- উপরে

- ব্যবহার

- সদ্ব্যবহার করা

- মাধ্যমে

- ঠাহর করা

- উপায়..

- we

- কখন

- যে

- যখন

- ব্যাপকতর

- সঙ্গে

- মধ্যে

- would

- এখনো

- zephyrnet

- শূন্য