كانت S2C رائدة عالميًا في النماذج الأولية لـ FPGA منذ ما يقرب من عقدين من الزمن حتى الآن ، وتتبعت منصات النماذج الأولية الخاصة بها FPGA عن كثب مدى توفر أحدث نماذج FPGA - بما في ذلك أحدث FPGA من كل من Xilinx و Intel. وهم يفيون بالتأكيد بوعدهم بتطوير حلول النماذج الأولية الخاصة بهم لنماذج التصميم فائقة النطاق - زيادة قدرات وقدرات منصة النماذج الأولية لدعم تصميمات بمليارات من البوابات.

إذا نظرنا إلى الوراء إلى أوائل الربع الرابع من عام 4 ، أعلنت S2020C عن دعمها لـ Xilinx VU2P UltraScale + FPGAs الجديدة آنذاك ، حيث تقدم منصات نماذج أولية أحادية وثنائية ورباعية FPGA. بعد ذلك ، في ديسمبر من عام 19 ، تابعت S2020C بإعلان عن عائلة Prodigy Logic Matrix عالية الكثافة من منصات النماذج الأولية مع 2 FPGAs لكل مصفوفة منطقية ، و 8 مصفوفة منطقية لكل رف خادم واحد (8 FPGA) ، واتصال متعدد رفوف الخادم معًا. تم تسليم التكرارات الأولى لمصفوفة المنطق باستخدام Xilinx VU64 FPGAs (أطلق عليها اسم LX1) للعملاء الأوائل الذين لم يتمكنوا من انتظار إصدار VU19P (يطلق عليه اسم LX2).

الآن ، تقوم S2C بتكثيف لعبة Logic Matrix الخاصة بها مع LX2، والذي يقفز سعة البوابة القابلة للاستخدام بنسبة 60٪ عن إصدار VU440! المزيد من البوابات القابلة للاستخدام لكل FPGA تعني عددًا أقل من FPGA ، وعدد أقل من وصلات FPGA ، وأداء أعلى لنفس التصميم النموذجي. بسعة بوابة تقدر بـ 392 مليون بوابة لكل LX2، رف خادم قياسي معبأ بالكامل بـ 8 LX2's تمكن قدرة النماذج المقدرة لأكثر من 3 مليارات بوابات ASIC!

الشكل 1: مصفوفة المنطق المعجزة LX2

| عائلة مصفوفة المنطق المعجزة | ||

| LX1 | LX2 | |

| FPGA | XCVU440 | XCVU19P |

| بوابات ASIC المقدرة (M) | 240 | 392 |

| عدد FPGAs | 8 | 8 |

| خلايا منطق النظام (K) | 44,328 | 71,504 |

| ذاكرة FPGA (ميجابايت) | 709 | 1,327.2 |

| شرائح DSP | 23,040 | 30,720 |

| I / Os المستخدم الخارجي | 9,216 | 10,368 |

| SerDes أجهزة الإرسال والاستقبال | 384 جيجا | 640 جي تي واي |

| موصلات معجزة | 64 | 72 |

| موصلات PGT | 8 | 0 |

| موصلات جهاز الإرسال والاستقبال | 80 MSAS لكل منها 4 GTH + 8 IOs | 160 MCIO لكل منها 4 GTY + 8 IOs |

| أداء SerDes | 16 جيجابايت في الثانية | 28 جيجابايت في الثانية |

الشكل 2: عائلة مصفوفة المنطق

يعد الاتصال المرن وعالي السرعة مفتاحًا لنماذج FPGA عالية الكثافة ، وتدعم المصفوفة المنطقية استراتيجية اتصال هرمي من 3 مستويات: شورت بريدج للتواصل بين FPGAs المجاورة ؛ رابط النظام لتوصيل كابل FPGA ذي النطاق الترددي العالي ، و ترانسلينك للحصول على مسافة أطول من FPGA SerDes ، قم بالتوصيل البيني عبر كبلات MCIO. لتبسيط الاتصال البيني FPGA وتعظيم قيمة ترانسلينك، يدعم تدفق التقسيم الخاص بـ S2C تقنية Xilinx التي تم طرحها حديثًا لتعدد الإرسال والاستقبال عالي السرعة (HSTPM) ، مما يبسط نقل الإشارات بدقة الدورة ، وتعدد إرسال الدبوس ، واتصال SerDes FPGA بزمن وصول منخفض.

لتقليل الوقت اللازم لوضع النماذج الأولية ، وزيادة إنتاجية النماذج الأولية ، تم تصميم أدوات إنتاجية النماذج الأولية الأخرى من S2C مع وضع Logic Matrix في الاعتبار ، بما في ذلك لاعب محترف وقت التشغيل البرامج - وأدوات النمذجة الإضافية S2C بما في ذلك بروتوبريدج, ام دي ام بروو S2C's النموذج الأولي IP جاهز.

لاعب محترف وقت التشغيل تم تضمين البرنامج مع LX2، مما يوفر ميزات ملائمة مثل إدارة الساعة المتقدمة ، والاختبار الذاتي المتكامل ، والكشف التلقائي للوحة ، وبرمجة جهد الإدخال / الإخراج ، وتنزيلات FPGA المتعددة ، ومراقبة النظام وإدارته عن بُعد. كما تم تضمين AXEVision ، وهي أداة مدمجة لتصحيح أخطاء AXI-over-Ethernet لتبسيط تصحيح الأخطاء عن بُعد للتصاميم ذات الصلة بـ AXI.

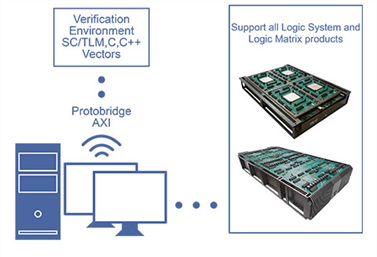

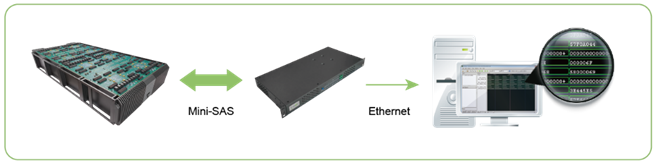

بروتوبريدج يدعم عمليات نقل البيانات عالية الإنتاجية (تصل إلى 1 جيجابايت / ثانية) بين الكمبيوتر المضيف و LX2 - تمكين نقل كميات كبيرة من المعاملات على غرار البرامج ، أو تدفقات الفيديو ، أو حوافز اختبار أخرى للتحقق من صحة النظام.

الشكل 3: جسر بروتوبريدج

ام دي ام برو يتميز بتصحيح التتبع العميق مع المشغلات المتقاطعة لما يصل إلى ثمانية FPGAs ، وعرض تتبع إشارة FPGA متعدد من نافذة عرض واحدة ، و 64 جيجابايت من تخزين شكل الموجة الخارجية ، ومعدلات أخذ عينات التتبع حتى 125 ميجا هرتز ، ويدعم لغات آلة حالة التشغيل لالتقاط التتبع المعقدة المتطلبات.

الشكل 4: MDM Pro

تقدم S2C's أيضًا مكتبة غنية بـ النموذج الأولي IP جاهز ل LX2 - بطاقات ابنة التوصيل والتشغيل - التي تسرع إنشاء بيئة النماذج الأولية حول النموذج الأولي FPGA.

الشكل 5: النموذج الأولي لبطاقات ابنة IP الجاهزة

مصفوفة المنطق المعجزة LX2 متاح الآن. لمزيد من المعلومات ، يرجى الاتصال بممثل مبيعات S2C المحلي ، أو زيارة www.s2ceda.com.

شارك هذا المنشور عبر: المصدر: https://semiwiki.com/prototyping/s2c-eda/304634-s2c-delivers-on-plan-to-scale-up-fpga-prototyping-platforms-to-billions-of-gates/- 2020

- اضافه

- أعلن

- اشعارات

- حول

- ASIC

- توفر

- مليار

- مجلس

- الكابلات

- الطاقة الإنتاجية

- صلة

- الإتصال

- العملاء

- البيانات

- تقديم

- تصميم

- كشف

- مسافة

- في وقت مبكر

- البيئة

- للعائلات

- المميزات

- تين

- الاسم الأول

- تدفق

- FPGA

- لعبة

- البوابات و حواجز اللعب

- العالمية

- HTTPS

- بما فيه

- معلومات

- إنتل

- IP

- القفل

- اللغات

- كبير

- آخر

- المكتبة

- محلي

- إدارة

- مصفوفة

- مليون

- مراقبة

- الوهب

- عروض

- أخرى

- PC

- أداء

- المنصة

- منصات التداول

- برو

- إنتاجية

- أدوات الإنتاجية

- برمجة وتطوير

- النماذج

- الأجور

- المتطلبات الأساسية

- الأملاح

- زيادة

- تطبيقات الكمبيوتر

- الحلول

- الولايه او المحافظه

- حافز

- تخزين

- الإستراتيجيات

- تيارات

- الدعم

- الدعم

- نظام

- تجربه بالعربي

- المعاملات

- قيمنا

- فيديو

- انتظر

- من الذى