هناك اثنتين من التقنيات الخوارزمية الحديثة القائمة على البرمجيات - القيادة الذاتية (ADAS/AD) والذكاء الاصطناعي التوليدي (GenAI) - تعملان على إبقاء مجتمع هندسة أشباه الموصلات مستيقظًا في الليل.

في حين أن ADAS في المستوى 2 والمستوى 3 يسير على الطريق الصحيح، فإن AD في المستويين 4 و 5 بعيدان عن الواقع، مما يتسبب في انخفاض حماس رأس المال الاستثماري والمال. اليوم، تحظى GenAI بالاهتمام، وتستثمر شركات رأس المال الاستثماري بشغف مليارات الدولارات.

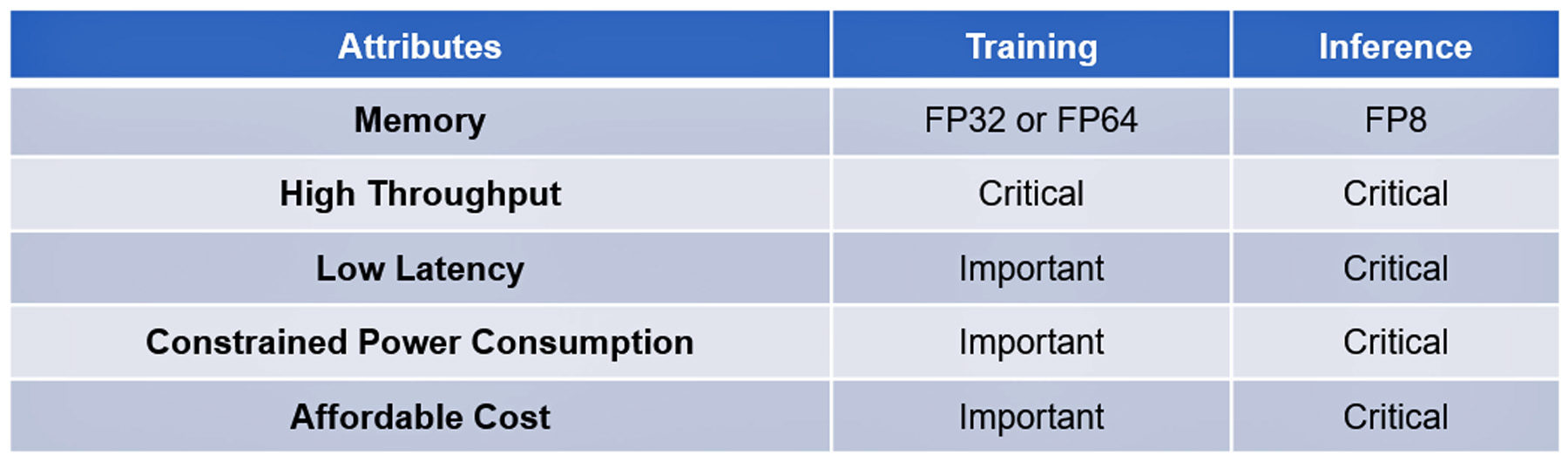

تعتمد كلتا التقنيتين على خوارزميات حديثة ومعقدة. تشترك معالجة تدريبهم واستدلالهم في بعض السمات، بعضها بالغ الأهمية، والبعض الآخر مهم ولكنه ليس ضروريًا: انظر الجدول الأول.

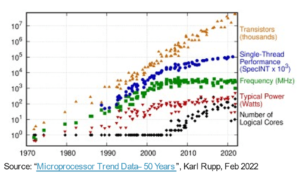

لم يتم حتى الآن تكرار التقدم الملحوظ في البرامج في هذه التقنيات من خلال التقدم في الأجهزة الخوارزمية لتسريع تنفيذها. على سبيل المثال، لا تتمتع المعالجات الخوارزمية المتطورة بالأداء اللازم للرد على استعلامات ChatGPT-4 في ثانية أو ثانيتين بتكلفة 2 سنت لكل استعلام، وهو المعيار الذي وضعه بحث Google، أو لمعالجة البيانات الضخمة. يتم جمعها بواسطة أجهزة استشعار AD في أقل من 20 مللي ثانية.

وذلك حتى استثمرت شركة VSORA الفرنسية الناشئة قدراتها العقلية لمعالجة عنق الزجاجة في الذاكرة المعروف باسم جدار الذاكرة.

جدار الذاكرة

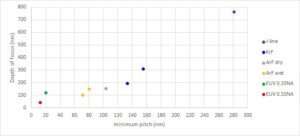

تم وصف جدار الذاكرة لوحدة المعالجة المركزية لأول مرة من قبل وولف وماكي في عام 1994. ومنذ ذلك الحين، أصبح الوصول إلى الذاكرة بمثابة عنق الزجاجة لأداء الحوسبة. لم ينعكس التقدم في أداء المعالج في التقدم في الوصول إلى الذاكرة، مما دفع المعالجات إلى الانتظار لفترة أطول من أي وقت مضى للبيانات التي تقدمها الذكريات. في النهاية، تنخفض كفاءة المعالج إلى أقل من 100%.

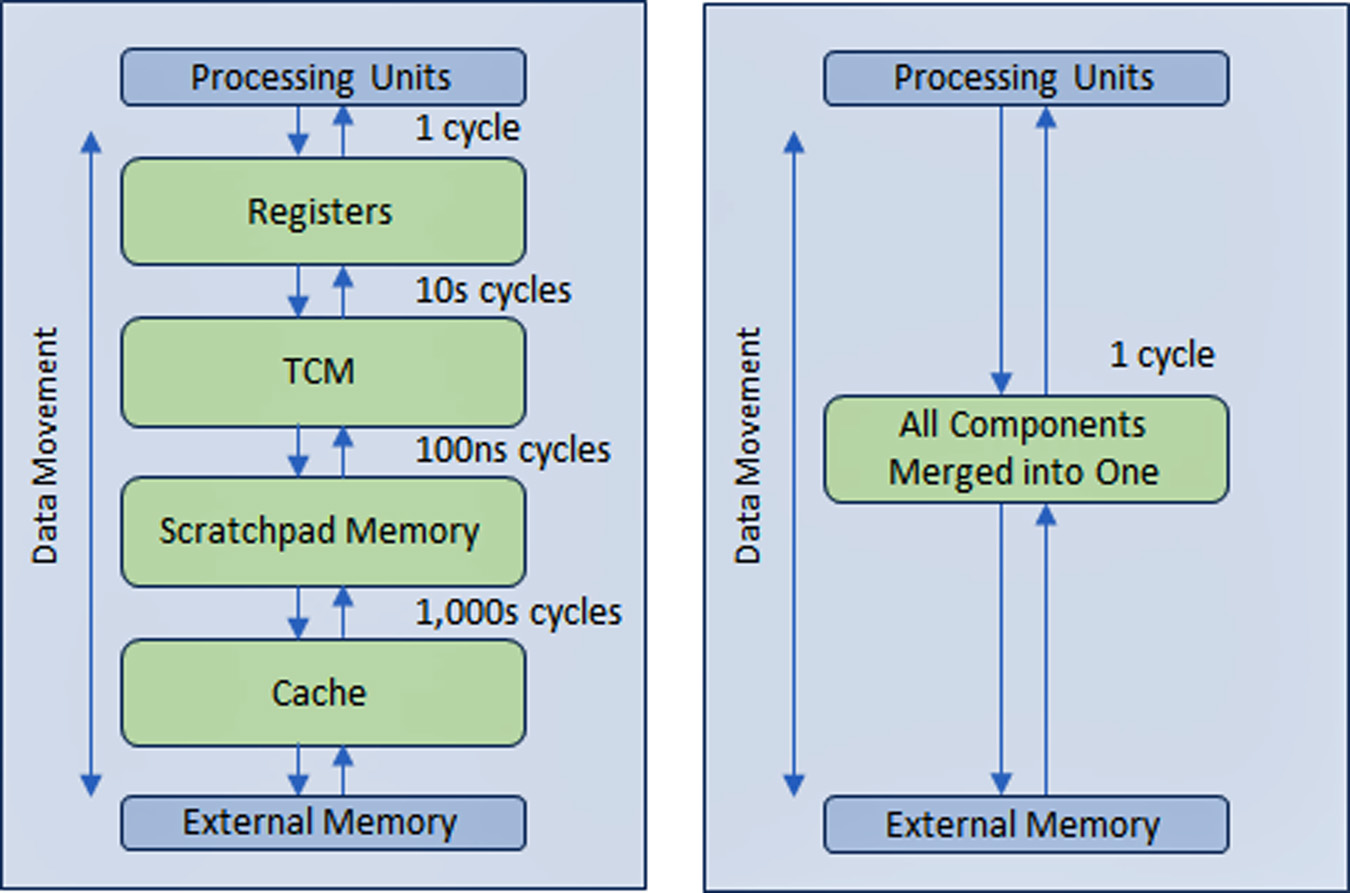

ولحل المشكلة، أنشأت صناعة أشباه الموصلات بنية ذاكرة هرمية متعددة المستويات مع مستويات متعددة من ذاكرة التخزين المؤقت بالقرب من المعالج مما يقلل من مقدار حركة المرور مع الذكريات الرئيسية والخارجية الأبطأ.

يعتمد أداء معالجات AD وGenAI أكثر من الأنواع الأخرى من أجهزة الحوسبة على النطاق الترددي الواسع للذاكرة.

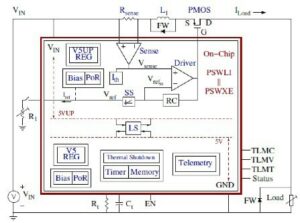

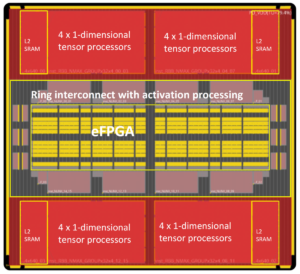

ابتكرت VSORA، التي تأسست في عام 2015 لاستهداف تطبيقات 5G، بنية حاصلة على براءة اختراع تعمل على تفكيك بنية الذاكرة الهرمية إلى نطاق ترددي كبير وعالي، وذاكرة مقترنة بإحكام (TCM) يمكن الوصول إليها في دورة ساعة واحدة.

من منظور نوى المعالج، يبدو جهاز TCM وكأنه بحر من السجلات بحجم ميغابايت مقابل كيلو بايت من السجلات الفعلية الفعلية. تؤدي القدرة على الوصول إلى أي خلية ذاكرة في TMC في دورة واحدة إلى سرعة تنفيذ عالية، وزمن وصول منخفض، واستهلاك منخفض للطاقة. كما يتطلب مساحة أقل من السيليكون. تحميل بيانات جديدة من الذاكرة الخارجية إلى TCM أثناء معالجة البيانات الحالية لا يؤثر على إنتاجية النظام. بشكل أساسي، تسمح البنية باستخدام 80+% من وحدات المعالجة من خلال تصميمها. ومع ذلك، هناك إمكانية لإضافة ذاكرة تخزين مؤقت وذاكرة مسودة إذا رغب مصمم النظام في ذلك. انظر الشكل 1.

من خلال بنية ذاكرة شبيهة بالسجل يتم تنفيذها في جميع الذكريات تقريبًا عبر جميع التطبيقات، لا يمكن المبالغة في تقدير ميزة نهج ذاكرة VSORA. عادةً ما توفر معالجات GenAI المتطورة كفاءة بنسبة مئوية واحدة. على سبيل المثال، يوفر معالج GenAI ذو الإنتاجية الاسمية التي تبلغ بيتافلوب واحد من الأداء الاسمي ولكن بكفاءة أقل من 5% أداءً قابلاً للاستخدام أقل من 50 تيرافلوب. وبدلاً من ذلك، تحقق بنية VSORA كفاءة أكبر بأكثر من 10 مرات.

مسرعات خوارزمية VSORA

قدمت VSORA فئتين من المسرعات الخوارزمية - عائلة Tyr لتطبيقات AD وعائلة Jotunn لتسريع GenAI. يوفر كلاهما إنتاجية ممتازة، والحد الأدنى من الكمون، واستهلاك منخفض للطاقة في بصمة سيليكون صغيرة.

مع الأداء الاسمي الذي يصل إلى ثلاثة بيتافلوب، فإنها تتميز بكفاءة تنفيذ نموذجية تتراوح من 50 إلى 80% بغض النظر عن نوع الخوارزمية، واستهلاك طاقة يصل إلى 30 وات/بيتافلوب. هذه سمات ممتازة، لم يتم الإبلاغ عنها بواسطة أي مسرع تنافسي للذكاء الاصطناعي حتى الآن.

Tyr وJotunn قابلان للبرمجة بالكامل ويدمجان قدرات الذكاء الاصطناعي ومعالجة الإشارات الرقمية، وإن كان ذلك بكميات مختلفة، ويدعمان الاختيار الفوري للحسابات من 8 بت إلى 64 بت إما على أساس عدد صحيح أو الفاصلة العائمة. تستوعب قابلية برمجتها عالمًا من الخوارزميات، مما يجعلها لا تعرف الخوارزميات. يتم أيضًا دعم عدة أنواع مختلفة من التناثر.

تدفعهم سمات معالجات VSORA إلى صدارة مشهد المعالجة الخوارزمية التنافسي.

برامج دعم VSORA

صممت VSORA منصة فريدة للتجميع/التحقق من الصحة مصممة خصيصًا لبنية أجهزتها لضمان حصول أجهزتها SoC المعقدة وعالية الأداء على الكثير من دعم البرامج.

من المفترض أن يتم وضع المصمم الخوارزمي في قمرة القيادة، حيث تقدم مجموعة من مستويات التحقق/التحقق الهرمية - ESL، والهجين، وRTL، والبوابة - ردود فعل بضغطة زر إلى المهندس الخوارزمي استجابةً لاستكشافات الفضاء التصميمية. وهذا يساعده على اختيار أفضل حل وسط بين الأداء وزمن الوصول والطاقة والمساحة. يمكن تعيين كود البرمجة المكتوب بمستوى عالٍ من التجريد لاستهداف نوى معالجة مختلفة بشفافية للمستخدم.

يمكن تنفيذ التواصل بين النوى داخل نفس السيليكون، أو بين الرقائق الموجودة على نفس PCB أو من خلال اتصال IP. تتم إدارة المزامنة بين النوى تلقائيًا في وقت التجميع ولا تتطلب عمليات برمجية في الوقت الفعلي.

حاجز للقيادة الذاتية L4/L5 واستدلال الذكاء الاصطناعي التوليدي على الحافة

يجب أن يتضمن الحل الناجح أيضًا إمكانية البرمجة في الميدان. تتطور الخوارزميات بسرعة، مدفوعة بأفكار جديدة عفا عليها الزمن بين عشية وضحاها. تعد القدرة على ترقية الخوارزمية في الميدان ميزة جديرة بالملاحظة.

في حين أن الشركات ذات الحجم الكبير تقوم بتجميع مزارع حوسبة ضخمة تحتوي على عدد كبير من معالجاتها عالية الأداء للتعامل مع خوارزميات البرامج المتقدمة، فإن هذا النهج عملي فقط للتدريب، وليس للاستدلال عند الحافة.

يعتمد التدريب عادةً على حسابات الفاصلة العائمة 32 بت أو 64 بت التي تولد كميات كبيرة من البيانات. إنه لا يفرض زمن وصول صارم ويتحمل استهلاك الطاقة العالية بالإضافة إلى التكلفة الكبيرة.

يتم إجراء الاستدلال عند الحافة عادةً على حساب الفاصلة العائمة 8 بت الذي يولد كميات أقل إلى حد ما من البيانات، ولكنه يتطلب زمن انتقال لا هوادة فيه، واستهلاك منخفض للطاقة، وتكلفة منخفضة.

تأثير استهلاك الطاقة على الكمون والكفاءة

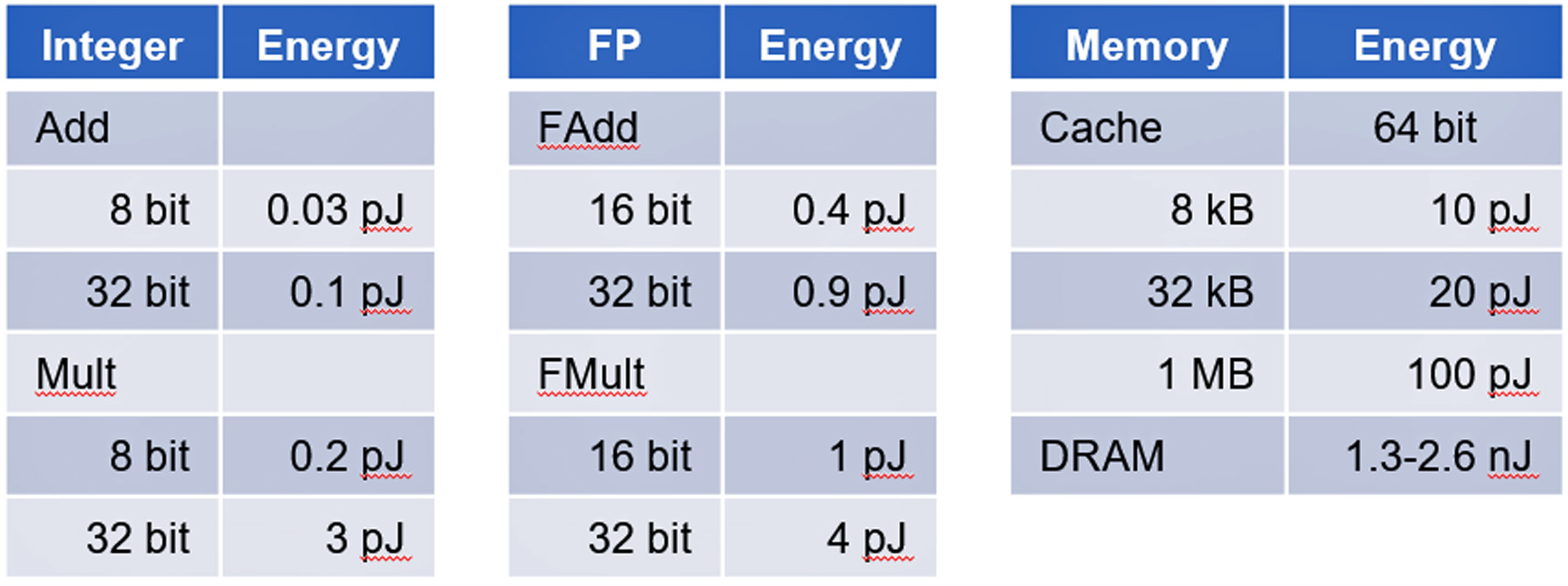

يهيمن على استهلاك الطاقة في دوائر CMOS المرحلية حركة البيانات وليس معالجة البيانات.

أظهرت دراسة أجرتها جامعة ستانفورد بقيادة البروفيسور مارك هورويتز أن استهلاك الطاقة للوصول إلى الذاكرة يستهلك طاقة بحجم أكبر من حسابات المنطق الرقمي الأساسية. انظر الجدول الثاني.

تعد مسرعات AD وGenAI من الأمثلة الرئيسية للأجهزة التي تهيمن عليها حركة البيانات مما يشكل تحديًا لاحتواء استهلاك الطاقة.

وفي الختام

يشكل استنتاج AD وGenAI تحديات غير تافهة لتحقيق تطبيقات ناجحة. يمكن لشركة VSORA تقديم حل شامل للأجهزة وبرامج دعم لتلبية جميع المتطلبات الهامة للتعامل مع AD L4/L5 وGenAI مثل تسريع GPT-4 بتكاليف قابلة للتطبيق تجاريًا.

يمكن العثور على مزيد من التفاصيل حول VSORA وTyr وJotunn على الموقع www.vsora.com.

حول لاورو ريزاتي

لاورو ريزاتي هو مستشار أعمال لـ VSORA، وهي شركة ناشئة مبتكرة تقدم حلول IP للسيليكون ورقائق السيليكون، ومستشار تحقق مشهور وخبير في الصناعة في مجال محاكاة الأجهزة. في السابق، شغل مناصب في الإدارة وتسويق المنتجات والتسويق الفني والهندسة.

اقرأ أيضا:

تعمل Soitec على هندسة مستقبل صناعة أشباه الموصلات

ISO 21434 لتطوير SoC المدرك للأمن السيبراني

الصيانة التنبؤية في سياق السلامة الوظيفية للسيارات

شارك هذا المنشور عبر:

- محتوى مدعوم من تحسين محركات البحث وتوزيع العلاقات العامة. تضخيم اليوم.

- PlatoData.Network Vertical Generative Ai. تمكين نفسك. الوصول هنا.

- أفلاطونايستريم. ذكاء Web3. تضخيم المعرفة. الوصول هنا.

- أفلاطون كربون، كلينتك ، الطاقة، بيئة، شمسي، إدارة المخلفات. الوصول هنا.

- أفلاطون هيلث. التكنولوجيا الحيوية وذكاء التجارب السريرية. الوصول هنا.

- المصدر https://semiwiki.com/automotive/336201-long-standing-roadblock-to-viable-l4-l5-autonomous-driving-and-generative-ai-inference-at-the-edge/

- :لديها

- :يكون

- :ليس

- $ UP

- 000

- 1

- 10

- 1800

- 1994

- 20

- 30

- 50

- 5G

- a

- القدرة

- حول المستشفى

- التجريد

- تسريع

- تسارع

- مسرع

- المعجلات

- الوصول

- الوصول

- الوصول

- التأهيل

- يحقق

- في

- الأفعال

- يقدم

- Ad

- أدا

- تضيف

- العنوان

- متقدم

- التطورات

- مميزات

- المستشار

- تؤثر

- AI

- خوارزمية

- خوارزمية

- خوارزميات

- الكل

- يسمح

- أيضا

- كمية

- المبالغ

- an

- و

- إجابة

- أي وقت

- التطبيقات

- نهج

- هندسة معمارية

- هي

- المنطقة

- فنـون

- AS

- At

- اهتمام

- سمات

- تلقائيا

- السيارات

- مستقل

- عرض النطاق الترددي

- على أساس

- الأساسية

- في الأساس

- BE

- أصبح

- كان

- أقل من

- مؤشر

- أفضل

- ما بين

- المليارات

- على حد سواء

- الأعمال

- لكن

- by

- مخبأ

- CAN

- لا تستطيع

- قدرات

- الموارد

- مما تسبب في

- الخلية

- تحدى

- التحديات

- شيبس

- فصول

- ساعة حائط

- مقصورة الطيار

- الكود

- الانهيارات

- تجاريا

- مجتمع

- الشركات

- تنافسي

- مجمع

- معقد

- شامل

- حل وسط

- الحسابات

- إحصاء

- الحوسبة

- صلة

- consultants

- استهلاك

- تحتوي على

- سياق الكلام

- التكلفة

- التكاليف

- إلى جانب

- وحدة المعالجة المركزية:

- خلق

- حرج

- حالياًّ

- المتطور والحديث

- دورة

- البيانات

- معالجة المعلومات

- نقل

- تم التوصيل

- يسلم

- كثيف

- يعتمد

- وصف

- تصميم

- تصميم

- مصمم

- تفاصيل

- الأجهزة

- مختلف

- رقمي

- الأرقام

- do

- هل

- دولار

- مدفوع

- قيادة

- قطرة

- قطرات

- بلهفة

- حافة

- كفاءة

- إما

- النهاية

- طاقة

- استهلاك الطاقة

- مهندس

- الهندسة

- ضمان

- حماسة

- ESL

- أساسي

- أنشئ

- EVER

- يتطور

- مثال

- أمثلة

- خبير

- خارجي

- للعائلات

- بعيدا

- المزارع

- ردود الفعل

- قليل

- حقل

- الشكل

- الاسم الأول

- يطفو على السطح

- البصمة

- في حالة

- طليعة

- وجدت

- تاسست

- الفرنسية

- تبدأ من

- تماما

- وظيفي

- مستقبل

- يولد

- توليدي

- الذكاء الاصطناعي التوليدي

- شراء مراجعات جوجل

- Google بحث

- أكبر

- مقبض

- أجهزة التبخير

- يملك

- he

- عقد

- يساعد

- لها

- مرتفع

- أداء عالي

- أعلى

- وسلم

- هورويتز

- HTTP

- HTTPS

- ضخم

- مهجنة

- i

- ICS

- الأفكار

- if

- ii

- التنفيذ

- تطبيقات

- نفذت

- أهمية

- مفروض

- in

- تتضمن

- العالمية

- خبير الصناعة

- مبتكرة

- مثل

- بدلًا من ذلك

- دمج

- إلى

- أدخلت

- اخترع

- استثمر

- استثمرت

- IP

- IT

- انها

- JPG

- يقفز

- حفظ

- معروف

- المشهد

- كبير

- كمون

- ليد

- أقل

- مستوى

- ومستوياتها

- مثل

- جار التحميل

- منطق

- طويل الأمد

- يعد

- تبدو

- منخفض

- الرئيسية

- صيانة

- القيام ب

- تمكن

- إدارة

- ولايات

- علامة

- التسويق

- هائل

- ماكس العرض

- تعرف علي

- ذكريات

- مكبر الصوت : يدعم، مع دعم ميكروفون مدمج لمنع الضوضاء

- ميلي ثانية

- أدنى

- تقدم

- مال

- الأكثر من ذلك

- حركة

- متعدد

- جموع

- جديد

- ليل

- وأشار

- جدير بالملاحظة

- الآن

- مهمل

- of

- الوهب

- on

- ONE

- فقط

- عمليات

- or

- طلب

- الطلبات

- أخرى

- أخرى

- على مدى

- بين عشية وضحاها

- مبالغ فيه

- براءة اختراع

- قمة

- إلى

- نسبة مئوية

- أداء

- تنفيذ

- منظور

- مادي

- المنصة

- أفلاطون

- الذكاء افلاطون البيانات

- أفلاطون داتا

- وفرة

- البوينت

- مواقف

- إمكانية

- منشور

- قوة

- عملية

- سابقا

- رئيسي

- المشكلة

- عملية المعالجة

- معالجة

- معالجة

- المعالج

- المعالجات

- المنتج

- البروفيسور

- برمجة

- برمجة وتطوير

- التقدّم

- دفع

- وضع

- الاستفسارات

- نطاق

- بسرعة

- عرض

- في الوقت الحقيقي

- واقع

- الأخيرة

- يقلل

- بغض النظر

- سجلات

- لافت للنظر

- منسوخة

- وذكرت

- تطلب

- المتطلبات الأساسية

- يتطلب

- استجابة

- نفسه

- SEA

- بحث

- ثواني

- انظر تعريف

- اختيار

- أشباه الموصلات

- أجهزة الاستشعار

- عدة

- مشاركة

- مشاركة

- ينبغي

- أظهرت

- السيليكون

- منذ

- عزباء

- صغير

- So

- تطبيقات الكمبيوتر

- حل

- الحلول

- حل

- بعض

- قليلا

- مصدر

- الفضاء

- سرعة

- قضى

- ستانفورد

- جامعة ستانفورد

- بدء التشغيل

- الولايه او المحافظه

- دولة من بين الفن

- ممتاز

- لا يزال

- تبسيط

- صارم

- بناء

- دراسة

- جوهري

- ناجح

- الدعم

- مدعومة

- دعم

- تزامن

- نظام

- جدول

- تناسب

- الهدف

- استهداف

- تقني

- التكنولوجيا

- من

- أن

- •

- المستقبل

- من مشاركة

- منهم

- هناك.

- تشبه

- هم

- ثلاثة

- عبر

- الإنتاجية

- بإحكام

- الوقت

- مرات

- إلى

- اليوم

- مسار

- تقليدي

- حركة المرور

- قادة الإيمان

- بشفافية

- اثنان

- نوع

- أنواع

- نموذجي

- عادة

- فريد من نوعه

- الوحدات

- الكون

- جامعة

- حتى

- ترقية

- صالح للإستعمال

- مستخدم

- استخدام

- فكس

- مشروع

- فينشر كابيتال

- التحقق

- مقابل

- بواسطة

- قابل للحياة

- عمليا

- مجلدات

- انتظر

- جدار

- وكان

- طريق..

- حسن

- متى

- في حين

- واسع

- رغبات

- مع

- في غضون

- مكتوب

- حتى الآن

- عائدات

- زفيرنت