نشرت شركة Synopsys على موقع SolvNet محاضرة رائعة ألقاها الدكتور ثيو درين من شركة Intel Graphics. الموضوع هو التحقق من معادلة مسار البيانات. قد يبدو الأمر وكأنه مجرد تأييد رسمي آخر لـ Synopsys VC ولكن يجب عليك مشاهدته على أي حال. هذه مناقشة توسع العقل حول الاستخدامات والاعتبارات الرسمية والتي ستأخذك إلى ما هو أبعد من نوع دليل المستخدم الروتيني إلى منطقة أكثر روعة.

الفهم الفكري مقابل اختبار العينة

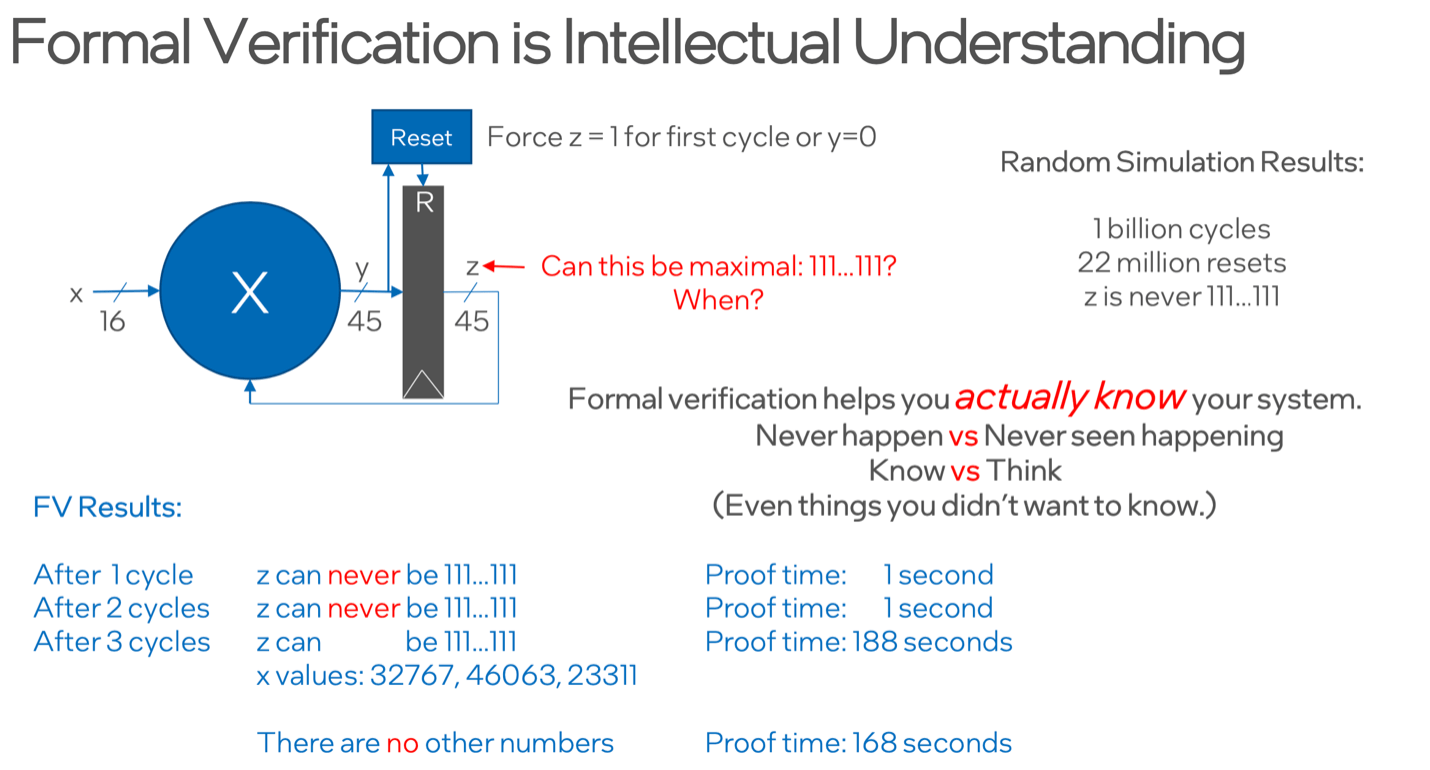

تعد المحاكاة القائمة على الاختبار بجميع أشكالها ممتازة ولا يمكن استبدالها في كثير من الأحيان للتحقق من صحة مواصفات التصميم أو التنفيذ. من السهل أيضًا البدء. ما عليك سوى كتابة برنامج اختبار والبدء في المحاكاة. لكن الجانب الآخر من تلك البساطة هو أننا لسنا بحاجة إلى ذلك تماما فهم ما نختبره للبدء. نحن نقنع أنفسنا بأننا قد قرأنا المواصفات بعناية وفهمنا جميع الحالات الأساسية، لكن الأمر لا يتطلب الكثير من التعقيد المضاعف ليطغى على فهمنا.

يشجعك Formal على فهم الوظيفة على مستوى عميق (على الأقل إذا كنت تريد تقديم نتيجة قيمة). في المثال أعلاه، فشل سؤال بسيط - هل يمكن أن تكون z جميعها 1 - في توضيح مثال في مليار دورة على جهاز محاكاة. ليس من المستغرب، لأن هذه حالة زاوية متطرفة. يقدم الاختبار الرسمي مثالاً محددًا وغير واضح للغاية في 188 ثانية، ويمكن أن يثبت أن هذه هي الحالة الوحيدة من نوعها في وقت أقل قليلاً.

حسنًا، فعلت الطريقة الرسمية ما لم يستطع الاختبار الديناميكي فعله، ولكن الأهم من ذلك أنك تعلمت شيئًا ربما لم يخبرك به جهاز المحاكاة أبدًا. أنه كانت هناك حالة واحدة فقط محتملة يمكن أن يحدث فيها هذا الشرط. لقد ساعدك الشكل الرسمي على فهم التصميم بشكل أفضل على المستوى الفكري، وليس فقط كملخص احتمالي عبر مجموعة محدودة من حالات الاختبار.

قضايا المواصفات

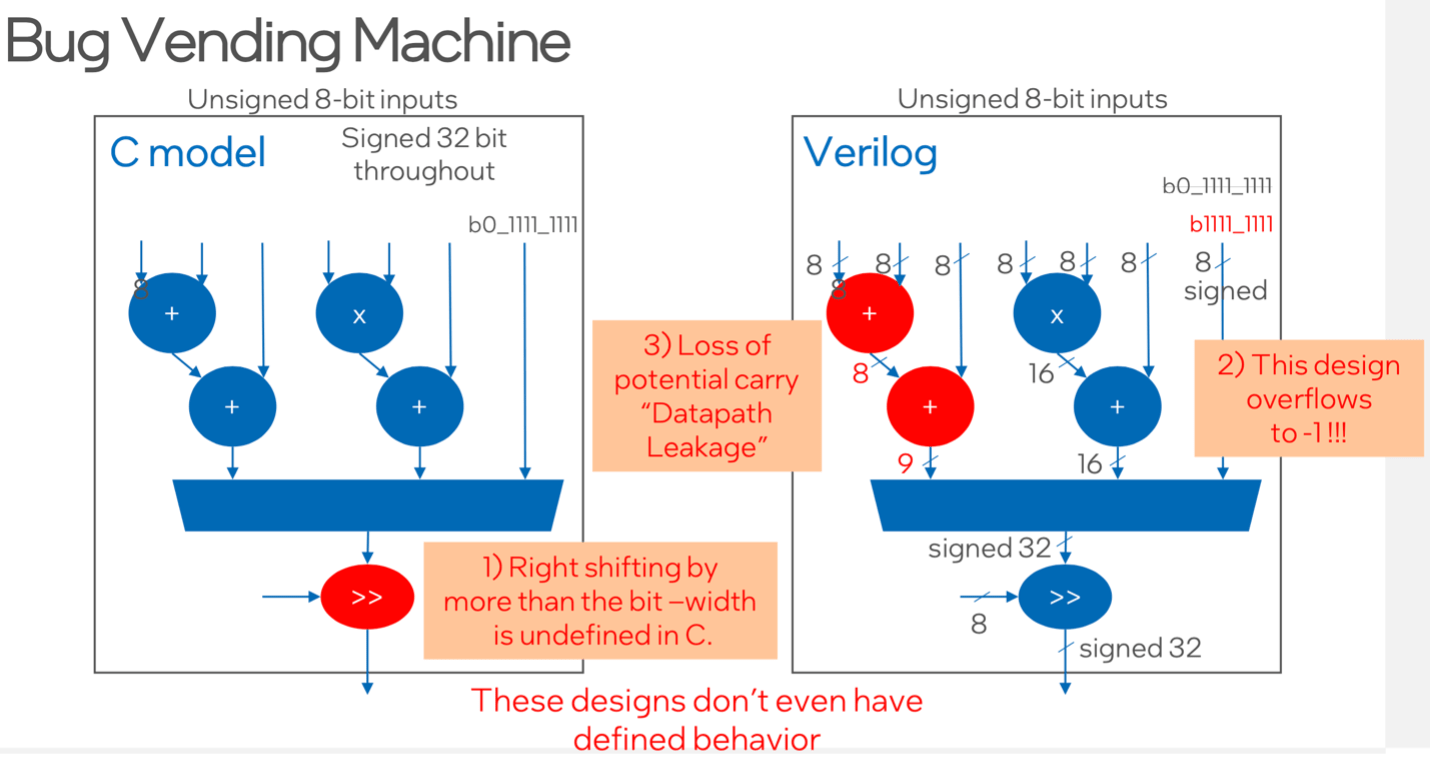

يعتمد مثال ثيو التالي على آلة بيع الأخطاء (تسمى هكذا لأنه عندما تضغط على زر تحصل على خطأ). يبدو هذا وكأنه مشكلة واضحة ومباشرة للتحقق من تكافؤ C إلى RTL، نموذج C على اليسار، ونموذج RTL على اليمين. كانت إحدى مفاجآت ثيو في أيامه الأولى في العمل الرسمي هي أن سلوك التحول إلى اليمين في النموذج C لم يتم تعريفه بالكامل في معيار C، على الرغم من أن دول مجلس التعاون الخليجي سوف تتصرف بشكل معقول. ومع ذلك، سوف تشكو DPV من عدم التطابق في المقارنة مع RTL، كما ينبغي. السلوك غير المحدد هو أمر خطير يمكن الاعتماد عليه.

تأتي مقارنة المواصفات بين لغة C وRTL مع مخاطر أخرى، خاصة فيما يتعلق بعرض البتات. يعد اقتطاع أو فقدان البت المحمول في الإشارة المتوسطة (رقم 3 أعلاه) من الأمثلة الجيدة. هل هذه مشاكل المواصفات؟ ربما منطقة رمادية بين المواصفات وخيارات التنفيذ.

أبعد من التحقق من التكافؤ

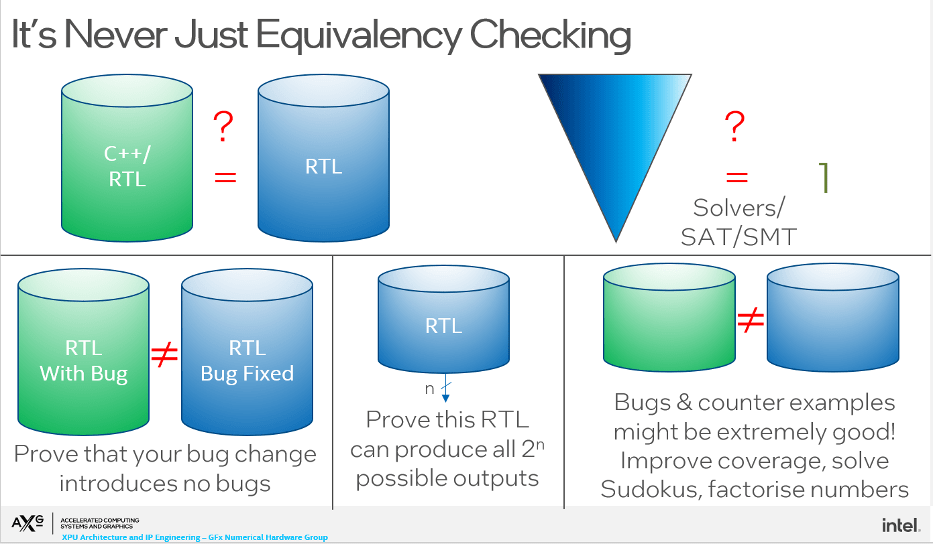

يبدو أن الغرض الأساسي من DPV هو التحقق من التكافؤ بين مرجع C أو RTL وتنفيذ RTL. لكن هذه الحاجة نادرة نسبيًا، وهناك طرق أخرى مفيدة يمكن من خلالها تطبيق مثل هذه التكنولوجيا، ولو بطريقة خارجة عن المألوف. في البداية، كان الأمر كلاسيكيًا في عالم التنفيذ - لقد أجريت تغييرًا وأصلحت خطأً ما - هل أدخلت أي أخطاء جديدة نتيجة لذلك؟ يشبه إلى حد ما التحقق من SEQ بعد إضافة بوابة الساعة. قد يكون تحليل إمكانية الوصول في مخرجات الكتلة تطبيقًا مفيدًا آخر في بعض الحالات.

أصبح ثيو أكثر إبداعًا، حيث طلب من المتدربين استخدام أمثلة مضادة لفهم التصميم بشكل أفضل، حل سودوكو or تحليل الأعداد الصحيحة. إنه يعترف بأن DPV يمثل طريقة غريبة للتعامل مع مثل هذه المشكلات ولكنه يشير إلى أن نيته هي كسر الوهم القائل بأن DPV هو فقط للتحقق من التكافؤ. فكرة مثيرة للاهتمام وتمتد بالتأكيد للعقل للتفكير في مثل هذه التحديات. (أعترف أنني بدأت على الفور أفكر في مشكلة سودوكو بمجرد أن ذكرها).

لف

ويختتم ثيو بمناقشة حول المنهجيات المهمة في استخدام الإنتاج، وحول القيود والانحدارات والمقارنات مع نماذج RTL القديمة. وأيضًا التحديات المتعلقة بمعرفة ما إذا كان ما تقوم بفحصه يتطابق بالفعل مع مواصفات اللغة الطبيعية ذات المستوى الأعلى.

كلام مؤثر جداً، يستحق المشاهدة هنا على سولفنت!

شارك هذا المنشور عبر:

- محتوى مدعوم من تحسين محركات البحث وتوزيع العلاقات العامة. تضخيم اليوم.

- بلاتوبلوكشين. Web3 Metaverse Intelligence. تضخيم المعرفة. الوصول هنا.

- المصدر https://semiwiki.com/eda/325878-intel-keynote-on-formal-a-mind-stretcher/

- :يكون

- a

- من نحن

- فوق

- في

- في الواقع

- بعد

- الكل

- تحليل

- و

- آخر

- تطبيق

- تطبيقي

- نهج

- هي

- المنطقة

- حول

- AS

- At

- على أساس

- BE

- لان

- أفضل

- ما بين

- Beyond

- مليار

- قطعة

- حظر

- صندوق

- استراحة

- علة

- البق

- زر

- by

- تسمى

- CAN

- بعناية

- حمل

- حقيبة

- الحالات

- بالتأكيد

- التحديات

- تغيير

- التحقق

- تدقيق

- الخيارات

- كلاسيكي

- ساعة حائط

- مقارنة

- تماما

- تعقيد

- حالة

- الاعتبارات

- القيود

- إقناع

- زاوية

- استطاع

- Counter

- الإبداع

- دورات

- خطير

- أيام

- عميق

- تعريف

- نقل

- شرح

- تصميم

- فعل

- مناقشة

- لا

- لا

- ديناميكي

- في وقت مبكر

- يشجع

- خاصة

- حتى

- EVER

- مثال

- أمثلة

- ممتاز

- أقصى

- فشل

- ساحر

- الاسم الأول

- ثابت

- نقف

- في حالة

- رسمي

- أشكال

- وظيفة

- الخليج

- دولار فقط واحصل على خصم XNUMX% على جميع

- معطى

- خير

- الرسومات

- اللون الرمادي

- منطقة رمادية

- يحدث

- يملك

- ساعد

- لكن

- HTTPS

- i

- فكرة

- فورا

- التنفيذ

- أهمية

- in

- إنتل

- فكري

- نية

- وكتابة مواضيع مثيرة للاهتمام

- متوسط

- تقديم

- مسائل

- IT

- انها

- رئيسية

- نوع

- معرفة

- لغة

- تعلم

- إرث

- مستوى

- مثل

- القليل

- تبدو

- خسارة

- آلة

- صنع

- جعل

- ماكس العرض

- المذكورة

- المنهجيات

- ربما

- نموذج

- عارضات ازياء

- الأكثر من ذلك

- طبيعي

- اللغة الطبيعية

- حاجة

- جديد

- التالي

- of

- on

- ONE

- أخرى

- رمية

- أفلاطون

- الذكاء افلاطون البيانات

- أفلاطون داتا

- نقاط

- ممكن

- منشور

- نشر

- صحافة

- جميل

- ابتدائي

- المشكلة

- مشاكل

- الإنتــاج

- البرنامج

- إثبات

- ويوفر

- غرض

- سؤال

- عرض

- نسبيا

- نتيجة

- ثواني

- طقم

- ينبغي

- سيجنل

- الاشارات

- بساطة

- محاكاة

- محاكاة

- منذ

- الموقع

- So

- بعض

- شيء

- قريبا

- محدد

- مواصفة

- معيار

- بداية

- بدأت

- صريح

- هذه

- ملخص

- مفاجأة

- مفاجئ

- أخذ

- حديث

- تكنولوجيا

- تجربه بالعربي

- الاختبار

- أن

- •

- تشبه

- شيء

- تفكير

- عبر

- الوقت

- إلى

- افضل مستوى

- موضوع

- اقتطاع

- فهم

- فهم

- الأستعمال

- تستخدم

- القيمة

- VC

- التحقق

- مقابل

- بواسطة

- شاهد

- مراقبة

- طريق..

- طرق

- حسن

- ابحث عن

- سواء

- التي

- سوف

- مع

- العالم

- قيمة

- سوف

- اكتب

- زفيرنت